引言

數(shù)據(jù)采集設(shè)備是測(cè)試系統(tǒng)中不可缺少的一部分,數(shù)據(jù)采集需要針對(duì)不同類型的需求,需要有高速A/D、低速A/D、數(shù)字多用表等功能,傳統(tǒng)數(shù)據(jù)采集設(shè)備是用一種儀器進(jìn)行一類測(cè)試,通過多種儀器組合實(shí)現(xiàn)一組完整測(cè)試,這種由多種儀器堆疊起來的數(shù)據(jù)采集系統(tǒng)具有體積和重量較大、成本較高、維護(hù)困難等諸多問題。針對(duì)這些問題,為完成某系列型號(hào)裝備自動(dòng)測(cè)試任務(wù),設(shè)計(jì)實(shí)現(xiàn)了一種高集成度數(shù)據(jù)采集設(shè)備。該設(shè)備需實(shí)現(xiàn)100 M高速A/D、雙通道隔離A/D、6通道低速A/D和數(shù)字多用表功能,采集數(shù)據(jù)通過LAN傳輸給上位機(jī)。輸入前端調(diào)理電路支持寬范圍多種信號(hào)輸入,并采用超寬輸入范圍的保護(hù)電路,實(shí)現(xiàn)設(shè)備通用性的同時(shí)保證其安全可靠。本設(shè)計(jì)采用DSP+FPGA架構(gòu),利用DSP/BIOS實(shí)時(shí)操作系統(tǒng),結(jié)合TI提供的NDK 網(wǎng)絡(luò)開發(fā)工具包,選用高集成度芯片,在10 cm×18 cm面積上設(shè)計(jì)實(shí)現(xiàn)該數(shù)據(jù)采集系統(tǒng)。

1 總體設(shè)計(jì)

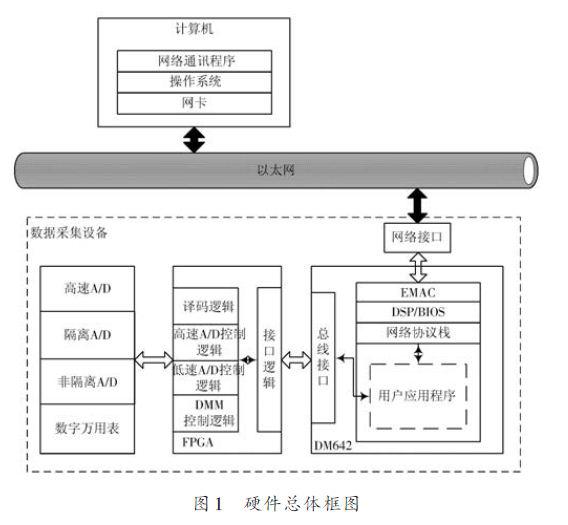

設(shè)備的總體結(jié)構(gòu)如圖1所示。設(shè)備能夠接入到以太網(wǎng)中,并能夠被計(jì)算機(jī)遠(yuǎn)程訪問。

計(jì)算機(jī)中網(wǎng)絡(luò)通訊程序控制設(shè)備進(jìn)行數(shù)據(jù)采集并讀取數(shù)據(jù)。整個(gè)設(shè)備以DSP+FPGA核心,包含高速A/D、低速隔離A/D、低速非隔離A/D和數(shù)字多用表。DSP選用TI公司主頻720 MHz、32 b定點(diǎn)高性能的TMS320DM642,DM642完成了網(wǎng)絡(luò)、主控功能。利用DM642的自帶的網(wǎng)絡(luò)功能接口,結(jié)合TI提供的網(wǎng)絡(luò)功能開發(fā)包(NDK)實(shí)現(xiàn)網(wǎng)絡(luò)通訊功能。采用DSP/BIOS實(shí)現(xiàn)分配調(diào)度線程、數(shù)據(jù)采集任務(wù)和網(wǎng)絡(luò)控制傳輸任務(wù),實(shí)現(xiàn)對(duì)數(shù)據(jù)采集、存儲(chǔ)和網(wǎng)絡(luò)通訊的控制。FPGA選用Altera公司的CycloneⅢ系列低成本工業(yè)級(jí)的EP3C55F484I8,編寫接口邏輯實(shí)現(xiàn)與DM642的數(shù)據(jù)交互,編寫譯碼邏輯、高速A/D控制邏輯、低速A/D控制邏輯、數(shù)字多用表控制邏輯實(shí)現(xiàn)數(shù)據(jù)采集功能。

2 硬件設(shè)計(jì)

2.1 網(wǎng)絡(luò)接口設(shè)計(jì)

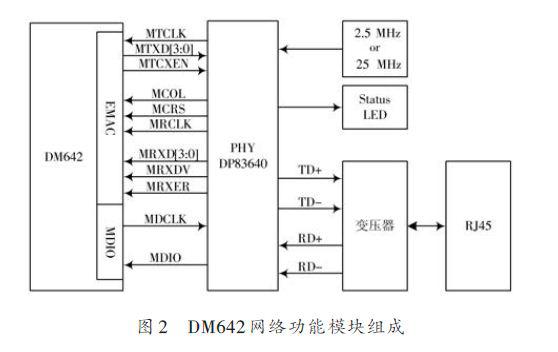

TMS320DM642 自帶一個(gè)網(wǎng)絡(luò)功能接口,由EMAC控制模塊、EMAC 模塊和MDIO 模塊組成[4],符合IEEE802.3協(xié)議,在設(shè)計(jì)網(wǎng)絡(luò)通訊接口時(shí)只需要外接一片網(wǎng)絡(luò)收發(fā)芯片即可,DM642的網(wǎng)絡(luò)功能模塊如圖2所示。

網(wǎng)絡(luò)收發(fā)芯片選用美國(guó)國(guó)家半導(dǎo)體公司推出的DP83640,其MII接口與DM642 的EMAC 接口直連,MII接口包括接收總線和發(fā)送總線,接收部分包括接收數(shù)據(jù)線RXD[30],接收錯(cuò)誤標(biāo)志RX_ER,接收數(shù)據(jù)有效標(biāo)志RX_DV 和數(shù)據(jù)同步接收時(shí)鐘信號(hào)RX_CLK,當(dāng)工作在10 Mb/s 時(shí),RX_CLK 為2.5 MHz,工作在100 Mb/s 時(shí),RX_CLK 為25 MHz.發(fā)送部分包含發(fā)送數(shù)據(jù)線TXD[30],發(fā)送使能位TX_EN,和發(fā)送時(shí)鐘TX_CLK,同樣,時(shí)鐘可以為2.5 MHz或者25 MHz.另外,MII接口帶有沖突檢測(cè)信號(hào)COL,用于檢測(cè)在半雙工模式下發(fā)送和接收同時(shí)發(fā)生的情況。該芯片具有的IEEE1588功能方便日后設(shè)備升級(jí)時(shí)鐘同步功能。

2.2 A/D采集模塊設(shè)計(jì)

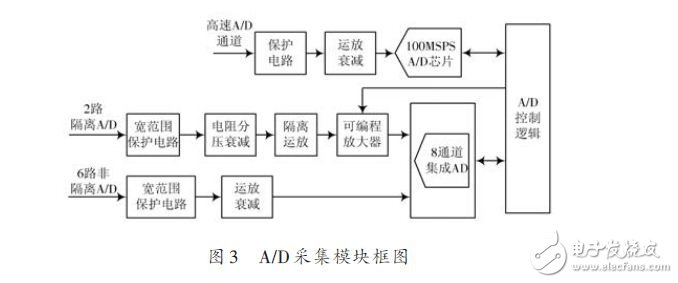

A/D 采集單元分為1 路高速采集和8 路低速采集兩部分,其中低速采集部分,分為2路隔離通道和6路非隔離通道,總圖框圖如圖3 所示。高速采集通道選用14 位的A/D6645,最高采樣率105 MSPS,并行輸出。低速采集通道選用24位的A/DS1278,單片并行8通道,最高采樣率144 KSPS,采用8 路串行輸出,同時(shí)采集8 路輸入信號(hào)。兩路隔離通道選用A/D215隔離運(yùn)放。

兩路隔離通道輸入電壓范圍±380 V,輸入阻抗為10 MΩ,1 路高速通道和6 路非隔離通道前端均采用運(yùn)放衰減,分別實(shí)現(xiàn)±5 V 和±40 V 電壓輸入范圍,高輸入阻抗和寬范圍電壓輸入范圍使該設(shè)備能夠適應(yīng)大部分被測(cè)系統(tǒng),實(shí)現(xiàn)了設(shè)備的通用化。每通道前端采用壓敏電阻和自恢復(fù)保險(xiǎn)絲設(shè)計(jì)寬范圍高可靠保護(hù)電路,保證設(shè)備的穩(wěn)定性和安全性。

2.3 數(shù)字多用表模塊設(shè)計(jì)

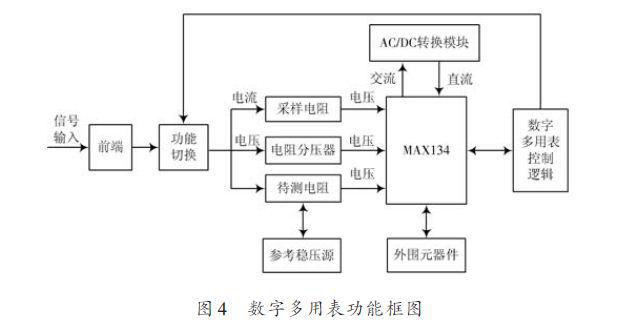

該設(shè)備對(duì)數(shù)字多用表測(cè)量速度、精度要求不是很高,但要求電路板的體積盡可能的小,因此在數(shù)字多用表電路設(shè)計(jì)上,選用了MAXIM 公司生產(chǎn)的MAX134 作為測(cè)量的核心芯片。MAX134 是單片智能數(shù)字多用表專用芯片,在其外圍配置少量元器件,設(shè)計(jì)簡(jiǎn)單的電路即可實(shí)現(xiàn)精度達(dá)到3位半的數(shù)字多用表。該設(shè)備的數(shù)字多用表功能框圖如圖4所示。采用繼電器實(shí)現(xiàn)功能切換;電阻分壓器實(shí)現(xiàn)0~400 V交、直流電壓輸入;0.1 Ω和1 Ω采樣電阻實(shí)現(xiàn)0~4 A交、直流電流轉(zhuǎn)換為電壓信號(hào)輸入;AC/DC轉(zhuǎn)換模塊采用有效值轉(zhuǎn)換芯片A/D637,實(shí)現(xiàn)交流信號(hào)轉(zhuǎn)直流;參考穩(wěn)壓源提供電阻測(cè)試的參考電壓,實(shí)現(xiàn)0~40 MΩ 電阻測(cè)量;外圍元器件實(shí)現(xiàn)MAX134 正常工作所需的晶振、電源、濾波等功能。

FPGA 內(nèi)部邏輯控制功能切換、實(shí)現(xiàn)MAX134內(nèi)部寄存器的讀寫,進(jìn)而實(shí)現(xiàn)數(shù)字多用表功能。

3 軟件設(shè)計(jì)

3.1 網(wǎng)絡(luò)通訊功能實(shí)現(xiàn)方法

本設(shè)計(jì)利用DSP/BIOS 結(jié)合NDK 實(shí)現(xiàn)網(wǎng)絡(luò)通訊功能。DSP/BIOS 是TI 公司為C28x,C5000 和C6000 系列DSP開發(fā)的可剪裁實(shí)時(shí)多任務(wù)操作系統(tǒng),同時(shí)也是CCS提供的一套多任務(wù)開發(fā)、硬件抽象、實(shí)時(shí)分析和系統(tǒng)配置的專用工具。DSP/BIOS以其功能豐富的APIs綜合管理系統(tǒng)內(nèi)存,實(shí)現(xiàn)任務(wù)分配和調(diào)度,實(shí)時(shí)監(jiān)測(cè)分析系統(tǒng)運(yùn)行,并提供方便的數(shù)據(jù)通信接口和外設(shè)驅(qū)動(dòng)開發(fā)工具。NDK是TI專門為網(wǎng)絡(luò)應(yīng)用開發(fā)提供的網(wǎng)絡(luò)開發(fā)工具包,利用其TCP/IP協(xié)議棧開發(fā)網(wǎng)絡(luò)應(yīng)用具有成本低、開發(fā)周期短的特點(diǎn)。網(wǎng)絡(luò)性能由套接字類型、套接字緩沖區(qū)、CPU速度和CPU緩沖等幾方面決定。要使用NDK 必須在DSP/BIOS 中配置TCP/IP 協(xié)議棧,主要在DSP/BIOS的。cdb文件中做以下配置:

(1)全局設(shè)置GBL

設(shè)置系統(tǒng)初始化函數(shù)dm642_init,用于設(shè)置L2 模式,分配MAC地址;

(2)設(shè)置MEM對(duì)象

配置程序、數(shù)據(jù)存儲(chǔ)區(qū)域及堆棧大小;

(3)設(shè)置HOOK對(duì)象

設(shè)置NDK的TCP/IP協(xié)議棧保存空間;

(4)設(shè)置PRD對(duì)象

設(shè)置NDK HAL庫中的定時(shí)驅(qū)動(dòng)事件;

(5)設(shè)置線程TSK

靜態(tài)創(chuàng)建2個(gè)線程:TSK_idle線程,優(yōu)先級(jí)最低,當(dāng)系統(tǒng)沒有其他任務(wù)執(zhí)行時(shí)運(yùn)行;TSK_main主線程,優(yōu)先級(jí)最高,用于配置服務(wù)器信息及啟動(dòng)HTTP服務(wù)。

配置文件生成之后,在DSP/BIOS 中編寫網(wǎng)絡(luò)主線程TSK_main,用于啟動(dòng)運(yùn)行TCP/IP 協(xié)議棧,啟動(dòng)HTTP服務(wù),同時(shí)不斷監(jiān)測(cè)和響應(yīng)網(wǎng)絡(luò)底層事件。在主線程中可以動(dòng)態(tài)創(chuàng)建任務(wù),用于實(shí)現(xiàn)與其他網(wǎng)絡(luò)設(shè)備的網(wǎng)絡(luò)通訊功能。

3.2 多任務(wù)線程管理機(jī)制

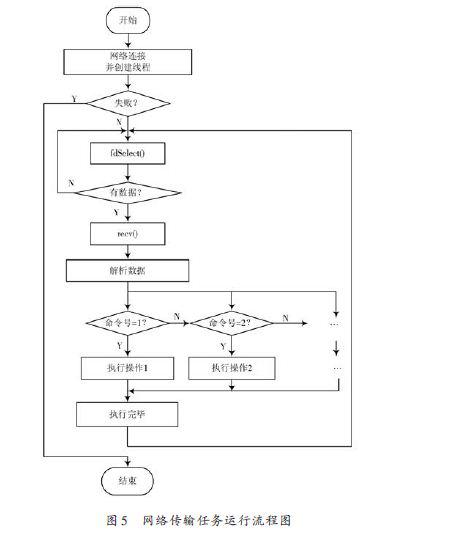

為了優(yōu)化CPU資源,實(shí)現(xiàn)各功能的協(xié)調(diào)運(yùn)作,需要合理劃分功能、規(guī)劃任務(wù)。本設(shè)計(jì)構(gòu)建了按優(yōu)先級(jí)從高到低創(chuàng)建了高速A/D 線程、低速A/D 線程、數(shù)字多用表線程、網(wǎng)絡(luò)傳輸線程和網(wǎng)絡(luò)配置線程。其中,網(wǎng)絡(luò)傳輸任務(wù)是最核心的任務(wù)線程,主要完成創(chuàng)建線程、網(wǎng)絡(luò)命令解析、通道查詢和數(shù)據(jù)上傳的功能,流程圖如5所示。

網(wǎng)絡(luò)傳輸任務(wù)使用套接字編程,工作在服務(wù)器模式,通訊方式采用TCP.首先調(diào)用fdOpenSession()函數(shù)建立文件描述表,調(diào)用socket()創(chuàng)建套接字,然后綁定IP信息、監(jiān)聽,然后等待客戶端連接請(qǐng)求,一旦客戶端連接上,便調(diào)用fdSelect()函數(shù)檢測(cè)客戶端是否發(fā)送數(shù)據(jù),如果有數(shù)據(jù)則接收,否則繼續(xù)檢測(cè),除非客戶端斷開連接。在這種設(shè)計(jì)模式下,允許客戶端重復(fù)的執(zhí)行斷開、連接操作,保證了系統(tǒng)工作的穩(wěn)定性。

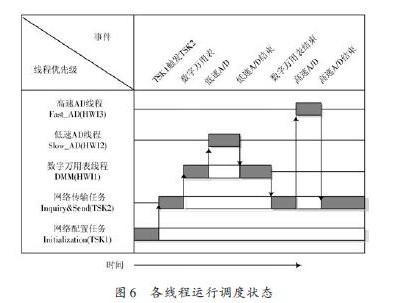

DSP/BIOS 支持硬件中斷(HWI)、軟件中斷(SWI)、任務(wù)(TSK)和空閑線程(IDL)4種類型的線程,它們的線程優(yōu)先級(jí)從高到低。硬件中斷線程主要用來處理響應(yīng)時(shí)間要求嚴(yán)格的請(qǐng)求,同時(shí)它的優(yōu)先級(jí)最高,能搶占當(dāng)前運(yùn)行的其他線程及時(shí)運(yùn)行,本設(shè)計(jì)各線程運(yùn)行調(diào)度狀態(tài)如圖6所示。

圖中黑色陰影部分表示線程運(yùn)行,白色不封表象線程掛起。高速A/D處理的數(shù)據(jù)量最大,對(duì)處理響應(yīng)的時(shí)間要求嚴(yán)格,故將它的優(yōu)先級(jí)設(shè)為最高,能搶占當(dāng)前運(yùn)行的其他線程及時(shí)運(yùn)行,保證數(shù)據(jù)實(shí)時(shí)上傳,低速A/D線程和數(shù)字多用表線程的優(yōu)先級(jí)根據(jù)其對(duì)時(shí)間的要求逐次降低。

4 測(cè)試

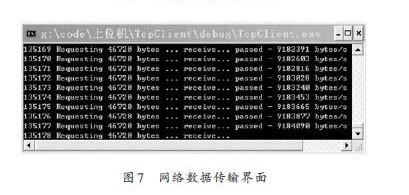

為了測(cè)試接口板的網(wǎng)絡(luò)通訊功能,使用PC 機(jī)作為客戶端,與設(shè)備通過路由器連在局域網(wǎng)內(nèi)。設(shè)備作為服務(wù)器端,在PC機(jī)端采用VS2005編寫上位機(jī)網(wǎng)絡(luò)通訊程序,每次傳輸46 720 B數(shù)據(jù),在開始和結(jié)束數(shù)據(jù)傳輸時(shí)刻讀取系統(tǒng)時(shí)間,并計(jì)算出網(wǎng)絡(luò)傳輸?shù)乃俾剩鐖D7所示。

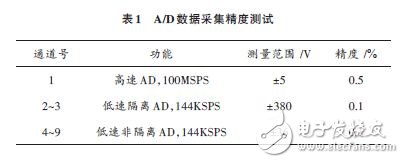

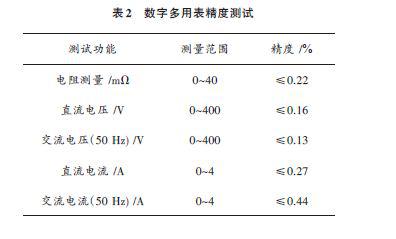

DM642中L2的Cache大小會(huì)影響網(wǎng)絡(luò)傳輸速度,實(shí)驗(yàn)發(fā)現(xiàn),當(dāng)Cache大小在128 KB是,傳輸速率達(dá)到了最佳,為89.2 Mb/s,由于在局域網(wǎng)中網(wǎng)絡(luò)環(huán)境相對(duì)復(fù)雜等原因,沒有達(dá)到理想的100 Mb/s的傳輸速率。A/D數(shù)據(jù)采集和數(shù)字多用表功能的測(cè)試,利用Agilent E3631A直流電源、Agilent 34110A6位半數(shù)字多用表和正泰TDGC2-0.2電源模塊等儀器,測(cè)試結(jié)果如表1和表2所示。

5 結(jié)語

本設(shè)備選用高性能高集成芯片,采用DSP+FPGA的主控方案,實(shí)現(xiàn)了數(shù)據(jù)采集設(shè)備的小型化。前端調(diào)理電路支持多種信號(hào)的寬動(dòng)態(tài)范圍測(cè)量,并具有可靠的過壓保護(hù),保證了設(shè)備的通用性與安全性。以DM642 的硬件資源為基礎(chǔ),通過調(diào)用NDK提供的APIs,實(shí)現(xiàn)了百兆以太網(wǎng)的傳輸。同時(shí),利用DSP/BIOS的多任務(wù)機(jī)制,實(shí)現(xiàn)網(wǎng)絡(luò)控制、數(shù)據(jù)采集以及網(wǎng)絡(luò)通訊的有效配合,保證底層高速采集的大數(shù)據(jù)量快速可靠得上傳給上位機(jī)。

實(shí)際應(yīng)用表明,該設(shè)備穩(wěn)定可靠、實(shí)時(shí)性強(qiáng)、兼容多種被測(cè)系統(tǒng),在數(shù)據(jù)采集領(lǐng)域中有一定的應(yīng)用價(jià)值。

-

dsp

+關(guān)注

關(guān)注

552文章

7962瀏覽量

348269 -

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601856 -

數(shù)據(jù)采集

+關(guān)注

關(guān)注

38文章

5906瀏覽量

113518

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)控機(jī)床數(shù)據(jù)采集如何實(shí)現(xiàn)?

小型化晶振的影響有哪些

天拓四方:設(shè)備數(shù)據(jù)采集網(wǎng)關(guān)如何有效解決生產(chǎn)設(shè)備數(shù)據(jù)采集的難題?

PLC采集網(wǎng)關(guān)如何實(shí)現(xiàn)多品牌PLC數(shù)據(jù)采集

數(shù)據(jù)采集處理設(shè)備是什么?數(shù)據(jù)采集處理設(shè)備的功能

工廠生產(chǎn)設(shè)備數(shù)據(jù)采集

PLC工業(yè)網(wǎng)關(guān)實(shí)現(xiàn)設(shè)備聯(lián)網(wǎng)與數(shù)據(jù)采集

物通博聯(lián)PLC網(wǎng)關(guān)實(shí)現(xiàn)mewtocol協(xié)議PLC設(shè)備數(shù)據(jù)采集

數(shù)據(jù)采集器是什么設(shè)備 數(shù)據(jù)采集器屬于什么設(shè)備類型

工業(yè)數(shù)據(jù)采集網(wǎng)關(guān)能采集工廠生產(chǎn)車間什么設(shè)備數(shù)據(jù)?

機(jī)床數(shù)據(jù)采集網(wǎng)關(guān)助力實(shí)現(xiàn)生產(chǎn)過程的智能化與高效化

如何實(shí)現(xiàn)更有效率的產(chǎn)線各工業(yè)設(shè)備數(shù)據(jù)采集?

數(shù)據(jù)采集網(wǎng)關(guān):工業(yè)數(shù)據(jù)采集上云

基于DSP技與+FPGA器件實(shí)現(xiàn)數(shù)據(jù)采集設(shè)備的小型化

基于DSP技與+FPGA器件實(shí)現(xiàn)數(shù)據(jù)采集設(shè)備的小型化

評(píng)論