在應(yīng)用DSP 進(jìn)行數(shù)字信號處理時(shí),通常都要用采樣電路對模擬信號進(jìn)行采樣,然后進(jìn)行A/D 轉(zhuǎn)換器轉(zhuǎn)換成數(shù)字信號再進(jìn)行數(shù)據(jù)處理。這里給出一種由TLV1571 與TMS320VC5410[1]組成的信號采集系統(tǒng)。

1 TLV1571 簡介:

在DSP 的外圍電路中,A/D 轉(zhuǎn)換器比較重要。基于不同的應(yīng)用,可選擇不同性能指標(biāo)和價(jià)位的芯片。一般的A/D 轉(zhuǎn)換器的選擇主要考慮:轉(zhuǎn)換精度、轉(zhuǎn)換時(shí)間、轉(zhuǎn)換器的價(jià)格。

這里選擇了TI 公司專門為DSP 配套的一種10 位的并行A/D 轉(zhuǎn)換器TLV1571, 該器件給定的CLK 頻率達(dá)到的等效最大采樣頻率為(1/16) fCLK。

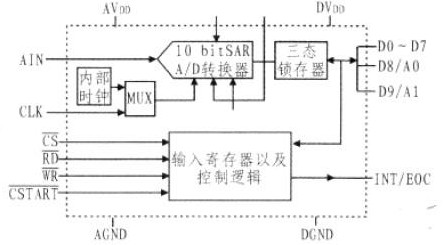

1.1 TLV1571 的內(nèi)部結(jié)構(gòu)及引腳定義:

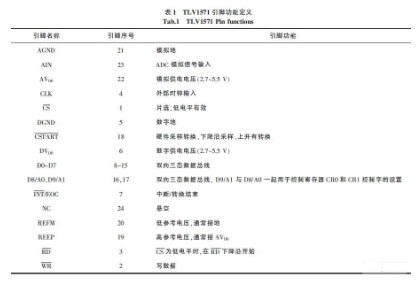

TLV1571 的內(nèi)部結(jié)構(gòu)及引腳功能定義如圖1 及表1 所示。

TLV1571 采用2.7~5.5 V 的單電源工作,能接受0~3.3 V的模擬輸入電壓, 此時(shí)以625 Kb/s 的速度使輸入電壓數(shù)字化。在5 V 電壓下,以最大1.25 Mb/s 的速度使輸入電壓數(shù)字化。該A/D 轉(zhuǎn)換器具有速度高,接口簡單以及功耗低等特點(diǎn),成為需要模擬輸入的高速數(shù)字信號處理的理想選擇。

1.2 TLV1571 的初始化:

上電后, 必須為低電平以開始I/O 周期,INT/EOC 最初為高電平。TLV1571 要求兩個(gè)寫周期以配置兩個(gè)控制寄存器。從掉電狀態(tài)返回后的首次轉(zhuǎn)換可能無效,應(yīng)當(dāng)不予考慮。

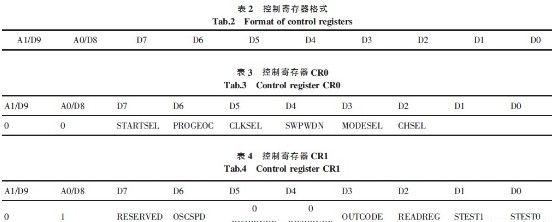

1.3 TLV1571 的控制寄存器控制字的設(shè)置:

TLV1571 的控制寄存器格式如表2 所示,它可以實(shí)現(xiàn)軟件配置,其兩個(gè)最高有效位D9 和D8 用于寄存器尋址,其余的8 位用作控制數(shù)據(jù)位。在寫周期內(nèi)所有寄存器位同時(shí)寫入控制寄存器,用戶可配置兩個(gè)控制寄存器CR0 和CR1,對于控制寄存器0(CR0),A1 ∶ A0=00,其配置如表3 所示;對于控制寄存器1(CR1),A1 ∶ A0 = 01,其配置如表4 所示。

通過改變控制寄存器的控制字,可以選擇TLV1571 的工作方式。通過配置CR0.D5 可以選擇時(shí)鐘源,對于時(shí)鐘源的選擇,有內(nèi)部時(shí)鐘和外部時(shí)鐘,它的內(nèi)部具有10 MHz 振蕩器。

通過配置CR1.D6 可以選擇內(nèi)置振蕩器的工作速度, 配置為(10±1)MHz 或(20±2)MHz。輸出方式也有2 種方式:二進(jìn)制輸出和補(bǔ)碼輸出。

在單通道輸入方式下則CR0.D3 = 0,CR1.D7 = 0; 采用軟件啟動方式則CR0.D7 = 1; 采用內(nèi)部時(shí)鐘源則CR0.D5 =0;內(nèi)部時(shí)鐘源振蕩頻率設(shè)置為20 MHz 則CR1.D6 = 1; 采用二進(jìn)制輸出方式,則CR1.D3 = 0。所以最終得到的控制寄存器控制字為:CR0 = 00C0H,CR1 = 0140H。在單通道軟件啟動時(shí),最初由WR 的上升沿啟動采樣,在RD 的上升沿發(fā)生采樣; 在采樣開始后的6 個(gè)時(shí)鐘周期后開始轉(zhuǎn)換,INT 方式時(shí),每次轉(zhuǎn)換后產(chǎn)生一個(gè)INT 脈沖;EOC 方式時(shí),轉(zhuǎn)換開始,EOC由高電平變至低電平,轉(zhuǎn)換結(jié)束后換回高電平。

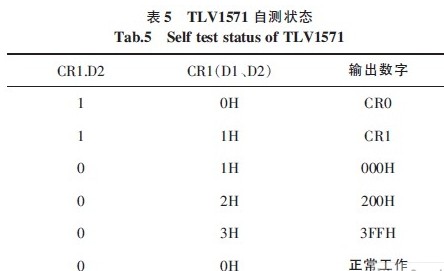

1.4 TLV1571 的自測:

TLV1571 提供了3 種自測方式。當(dāng)采用這些自測方式的時(shí)候,不用提供外部信號便可檢查A/D 轉(zhuǎn)換器本身工作是否正常。通過寫CR1(D1、D0)來控制這3 種自測方式,具體方法如表5 所示。另外當(dāng)CR1.D2 = 1, CR1(D1、D0) = 0 時(shí),此時(shí)回輸出寫入CR0 控制寄存器的控制字; 當(dāng)CR1.D2 = 1,CR1(D1、D0) = 1 時(shí),此時(shí)回輸出寫入CR1 控制寄存器的控制字,也可以用來測試和檢驗(yàn)控制字是否正確寫入控制寄存器及A/D 轉(zhuǎn)換器是否正常工作。

2 的接口連接及調(diào)試:

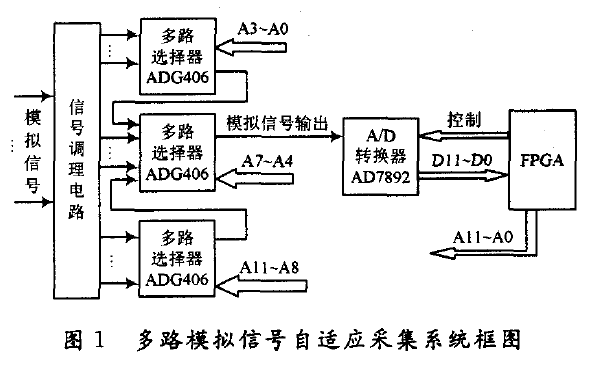

2.1 TLV1571 與TMS320VC5410 的接口:

TLV1571 與TMS320VC5410 的接口連接很簡單, 如圖2所示。這個(gè)系統(tǒng)中沒有采用硬件啟動采樣控制的方法,而是采用了軟件啟動的控制方法。時(shí)鐘信號也是采用A/D 轉(zhuǎn)換器的內(nèi)部時(shí)鐘。如果需要外部時(shí)鐘輸入,可以由DSP 提供一個(gè)精確而且可以根據(jù)需要控制變化的時(shí)鐘信號。本設(shè)計(jì)采用查詢方法來讀取轉(zhuǎn)換后的數(shù)據(jù)。另外在設(shè)計(jì)電路時(shí)要注意,當(dāng)供電電壓為3 V 時(shí),TLV1571 提供的采樣速度是625 ks/s,此時(shí)它的功耗為12 mW;當(dāng)供電電壓為5 V 時(shí),它提供的采樣速度是1.25 Ms/s,功耗為35 mW。

2.2 系統(tǒng)的調(diào)試:

在調(diào)試這個(gè)系統(tǒng)時(shí), 由于DSP 外部的I/O 空間的調(diào)試,基本上只涉及如何選通該空間,如何從外部空間取數(shù)據(jù)或讀數(shù)據(jù),如何和外部空間建立握手信號,但是要注意的是DSP與外圍器件時(shí)序上的配合。特別是對于數(shù)據(jù)線信號的讀取,當(dāng)系統(tǒng)中有多個(gè)器件共享DSP 數(shù)據(jù)線的時(shí)候,一定要處理好各個(gè)器件的時(shí)序配合。使處于非工作狀態(tài)的器件的數(shù)據(jù)線處于高阻狀態(tài), 以免影響正常工作的器件的數(shù)據(jù)讀寫。在對TLV1571 調(diào)試過程中需要注意以下問題:1)必須將TLV1571的2 個(gè)狀態(tài)字正確地寫入到A/D,可以在寫入后讀一次數(shù)據(jù)來確認(rèn)寫入數(shù)據(jù)的正確性,也可以采用循環(huán)寫入方式利用示波器觀察寫入的兩個(gè)脈沖信號, 另外也可以用讀出寫入CRO、CR1 控制寄存器控制字的方法來判斷控制字是否正確寫入了TLV1571 的控制寄存器內(nèi),也可以判斷器件是否正常工作;2)TMS320VC5410 的讀寫信號只有一根地址線, 所以需利用XF 引腳控制TLV1571 的讀信號,且必須在DSP 每次讀入數(shù)據(jù)后,用軟件控制XF 引腳輸出信號到TLV1571,否則A/D 將不再采樣。另外如果采用DSP 定時(shí)中斷來讀取數(shù)據(jù)的時(shí)候,在設(shè)置定時(shí)中斷時(shí),中斷間隔只要大于TLV1571 工作頻率所需采樣周期數(shù), 可以不用查詢的方法來讀取EOC 信號,而是直接讀取采樣數(shù)據(jù),然后控制XF 輸出信號使它進(jìn)行下一次采樣工作;3)TLV1571 不能采樣負(fù)的電壓信號, 如果必須采樣負(fù)的電壓信號,可以人為引入一個(gè)直流信號,將負(fù)電壓抬高到正電壓,而DSP 要在采樣信號中減去引入的直流信號;4) 為了驗(yàn)證采樣信號是否正確, 可以在CCS 下畫出所采樣數(shù)據(jù)的時(shí)域圖或頻域圖。

3 結(jié)束語:

實(shí)驗(yàn)證明該系統(tǒng)可以滿足一般高速實(shí)時(shí)信號的采樣和處理工作,驗(yàn)證了在單通道下該系統(tǒng)可以達(dá)到最高1.25 Ms/s的采樣速度,而且通過調(diào)整DSP 定時(shí)中斷時(shí)間可以方便的獲得在該系統(tǒng)最大采樣頻率(1.25 Mb/s)以下的各種采樣速度,可以靈活的滿足多種應(yīng)用。另外這個(gè)系統(tǒng)支持最多8 路的高速實(shí)時(shí)數(shù)據(jù)信號采集, 通過配置正確的A/D 轉(zhuǎn)換器控制字CR0、CR1 就可以方便的調(diào)整輸入信號的數(shù)量,而硬件電路不用改變。在實(shí)際的實(shí)驗(yàn)中,將這個(gè)系統(tǒng)制作成了一個(gè)最小系統(tǒng),通過修改加入所需要的器件,可以將這個(gè)系統(tǒng)制作成各種需要專用的數(shù)據(jù)采集系統(tǒng)。

-

電源

+關(guān)注

關(guān)注

184文章

17573瀏覽量

249483 -

dsp

+關(guān)注

關(guān)注

552文章

7962瀏覽量

348255 -

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8624瀏覽量

146861

發(fā)布評論請先 登錄

相關(guān)推薦

如何實(shí)現(xiàn)對模擬信號的采集 AD位數(shù)是如何影響信號幅值的

設(shè)計(jì)一個(gè) 8 路模擬信號,8 路開關(guān)信號的數(shù)據(jù)采集系統(tǒng)。

數(shù)字模擬信號的性能理念和設(shè)計(jì)資料

用NmyRIO-1900中的FPGA可以同時(shí)采集兩路模擬信號嗎?

兩片4通道AD芯片如何級聯(lián)實(shí)現(xiàn)8通道的模擬信號采集

stm32f103的ADC是如何去實(shí)現(xiàn)四路模擬信號采集的

模擬信號光纖傳輸系統(tǒng)實(shí)驗(yàn)

四路模擬信號采集隔離RS485/232輸出--ISO4014

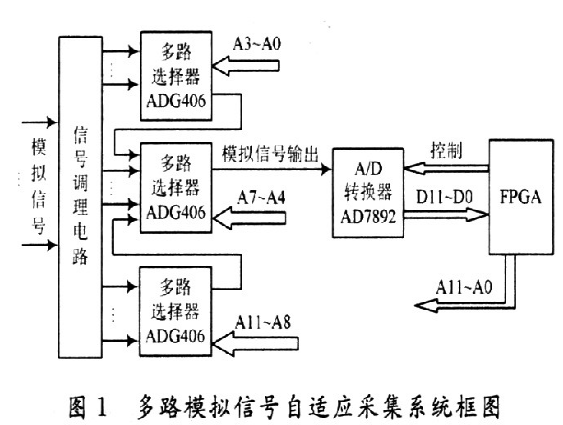

基于FPGA實(shí)現(xiàn)多路模擬信號自適應(yīng)采集系統(tǒng)

一種以FPGA為基礎(chǔ)的多路模擬信號自適應(yīng)采集系統(tǒng)設(shè)計(jì)

如何使用FPGA實(shí)現(xiàn)多路模擬信號自適應(yīng)采集系統(tǒng)

如何實(shí)現(xiàn)8路模擬信號采集系統(tǒng)設(shè)計(jì)

如何實(shí)現(xiàn)8路模擬信號采集系統(tǒng)設(shè)計(jì)

評論