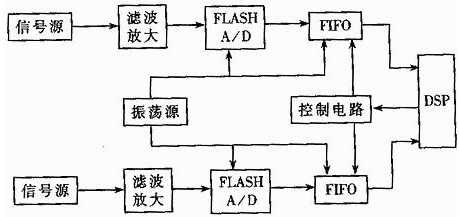

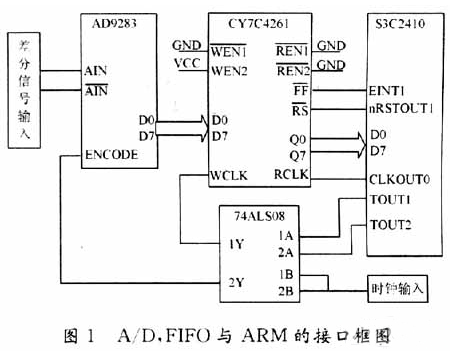

在科學技術高度發展的現代社會,超高速數據采集處理系統越來越廣泛地應用于雷達、通訊、圖像、軍工以及醫療化工等領域。本文介紹的是一種基于12位閃爍式模/數轉換器AD9224、大容量FIFO芯片UPD42280及高性能浮點型數字信號處理器TMS320C32的高速數據采集與處理系統。該系統能對兩路信號同時采樣,存入FIFO緩存器反再按需要由DSP控制進行分時處理。由于緩存的容量較大(256K字節),因此在高達33.3MHz的頻率下仍允許對信號連續采樣幾周波,以保證采樣的高度連續。其硬件原理圖如圖1所示。

1 高速A/D數據采集

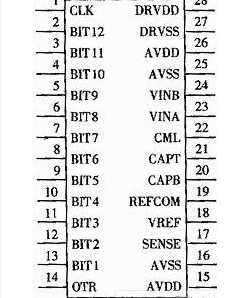

A/D變換器選用了AD公司的AD9224。圖2為其管腳圖,說明如下:

1(CLK) 時鐘輸入

2(BIT12) 數據輸出最低位LSB

3~12(BIT11~BIT2) 數據輸出

13(BIT1) 數據輸出最高位MSB

14(OTR) 數據溢出標志位

16、25(AVSS) 模擬地

17(SENSE) 參考選擇

18(VREF) 輸入參考選擇

19(REFCOM) 通用參考(AVSS)

20、21(CAPB、CAPT) 減噪管腳

22(CML) 共模方式

23(VINA) 模擬輸入(+)

24(VINB) 模擬輸入(-)

27(DRVSS) 數字地

28(DRVDD) 數字電源

AD9224是一種高性能、單電源+5V、最高采樣頻率為40MSPS的12位ADC。在本設計中,由于FIFO讀寫時間限制,A/D采樣頻率最高做到了33.3MHz。AD9224采用CMOS工藝制造,內部集成了基準電壓源、寬帶輸入采樣保持放大器等,并且采用四級流水線式結構,前三級每級包括一連接到開關電容器DAC、級間剩余放大器DMAC的閃爍式A/D,第四級只包括閃爍式A/D。閃爍式A/D是目前轉換速率最快的ADC。。AD9224采用CMOS工藝制造,內部集成了基準電壓源、寬帶輸入采樣保持放大器等,并且采用四級流水線式結構,前三級每級包括一個連接到開關電容器DAC、級間剩余放大器MDAC的閃爍式A/D,第四級只包括閃爍式A/D。閃爍式A/D是目前轉換速率最快的ADC。AD9224采用多級流水線結構對輸出錯誤進行邏輯糾正,以保證在整個工作范圍內不失碼,其數據以二進制形式輸出,并帶有信號溢出指示位。AD9224在+5V電源下功耗較低,為376mW。其微分非線性誤差為0.7LSB,信噪比和失真率為67.5dB。

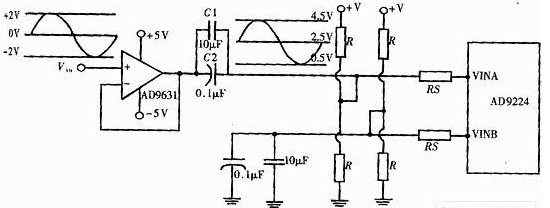

AD9224的輸入可以是單端或差分方式。本設計采用的是交流耦合單端輸入方式。信號經過由放大器AD9631和并聯電容組成的電路后被偏置為關于AVDD/2(2.5V)對稱的正弦波,C1和C2由0.1μF的陶瓷電容和10μF的鉭電容并聯,電容和電阻共同組成了一個高通濾波器。圖3所示為A/D部分的電路設計圖。

2 數據緩存

A/D采樣一點轉換一點。由于本系統的采樣速率高達幾十MSPS,如果存儲控制系統不能及時接收數據的話,則上次轉換的數據馬上就被下一個數據所覆蓋,很容易造成數據混亂。一般常用的DMA控制器所能達到的傳輸速率約為5Mb/s,即使是高性能的DSP芯片TMS320C32,其自帶的DMA通道所允許的A/D最高采樣速度也只達到15MSPS,并且受指令執行時間的限制,依然不能直接接受A/D數據線上的數據,因此必須采用高速緩存。目前常用的緩存多為FIFO(先入先出)、SRAM、及雙口RAM等。雙口RAM和SRAM一般存儲量較大,但必須用到復雜的地址發生器。FIFO芯片數據順序進出,且輸入輸出口獨立,在電路設計上相對簡單得多,但由于數據不能按址查詢,而是遵循先入先出的原則輸出,在軟件處理上要復雜一些。FIFO一般價格較貴,且存儲量不大。本設計所采用的FIFO是NEC公司生產的UPD42280,其容量為8位256K(實際是262224)字節,數據讀寫時間為30ns,是一種比較理想的FIFO芯片。該芯片內部采用動態RAM結構,能夠自動刷新,當讀寫完最后一個存儲單元后,又會自動回到第一個存儲單元。由于A/D有13條數據線(包括OTR位),所以每路用了兩片FIFO來接收數據。

3 DSP主處理器及控制電路

主處理器采用的是TI公司生產的TMS320C32PCM40。它是一種高性能的32位浮點型數字信號處理器,內部包括通用寄存器組、程序高速緩沖存儲器、專用輔助寄存器單元(ARAU)、兩個存儲器、兩個DMA通道。DSP所具有的高存儲空間(32位/16M)、多處理器接口、內部及外部產生的等待狀態、一個外部接口端口、兩個32位定時器、一個串行口以及多重中斷結構等,使其應用得到了很大的加強。

為了加快數據流的傳輸,克服瓶頸問題,DSP內部采用了哈佛總線結構(指令和數據有各自存儲空間,尋址或存取數據、指令有各自的傳輸總線)而不是通用處理器采用的馮諾依曼結構(指令和數據使用同一存儲空間,經由同一總線傳輸);為了進一步加快數據流的傳輸,DSP還采用了提高處理器的時鐘速度以及先進的處理方法(如流水線處理和并行處理)。這些都使得DSP的各項運算和處理能在一個時鐘周期內完成。DSP處理器的運算/處理功能單元要包括乘法器/乘加器(MAC)、算術運算單元(ALU)、移位器、數據地址發生器(DAG)。

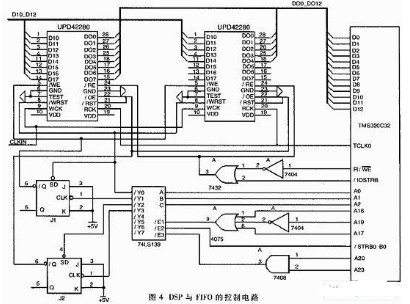

TMS320C32能與8/16/32位數據存儲器接口,并且可以進行8/16/32位程序引導,程序存儲器可以是16位或32位。它支持廣泛的系統尋址方式,實際上屬于間接尋址,是一種高效有用的尋址方式。另外,在尋址方式中TMS320C3X提供了一種循環尋址方式,可以在單周期內對整數或浮點數進行并行的乘法和算術邏輯單元(ALU)操作。圖4為本設計中一路FIFO與DSP的控制電路。

本設計中由于A/D有13條數據線(包括OTR位),所以每路用了兩片FIFO來接收數據。兩片FIFO的/WE管腳都連接到上路JK觸發器J1的/Q管腳上,以便由DSP控制使其同時接收數據。FIFO的讀片管腳/OE與讀復位管腳/RST接下路JK觸發器J2的/Q端,另一路接Q端以控制上下路選擇,FIFO的讀時鐘由DSP的定時器TCLK0給出。

系統工作過程如下:

上電后,AD9224加上時鐘信號即開始數據的轉換。寫數據時,DSP經過譯碼電路首先使/Y0輸出為低,則兩片FIFO的/WRST為低電平,FIFO垢寫指針位于0地址處;同時J1被預置,使/WE為低,兩片FIFO從0地址開始同步接收A/D轉換的數據。由于FIFO沒有存儲器寫滿標志,A/D沒有控制轉換起止標志,因此只能通過軟件控制,由DSP延時t(t為FIFO開始轉換到寫滿的時間)后,寫74LS138使/Y1為低,J1發生翻轉,/WE變為高,寫操作被禁止。讀數據時,在DSP控制下使/Y2為低,J2被置位,/Q為低,上路FIFO的/RST和/OE同時變低,讀指針處于0地址處并允許DSP對其進行讀操作。讀數據是通過對R/WE、/IOSTRB的共同操作完成的。DSP的處理完該路數據之后,再次寫譯碼器使/Y3為低,J2翻轉,/Q為高,上路FIFO的訪問被禁止;同時,Q變低,允許讀取下路FIFO的數據。

由于FIFO的讀烈軍屬時間所限,本設計的采樣時鐘沒有做到40MHz,而是采用了最高33.3MHz的時鐘。時鐘信號由66.6MHz的晶振振蕩器經過分頻后分別接到A/D的CLK端和FIFO的WCK端,以便使FIFO和AD9224采用同一時鐘源,保持時序的嚴格同步。

本設計為通用系統。采用高性能的12位模/數轉換器AD9224進行采樣,數據精度較高。盡管由于FIFO的讀取時間所限,最高采樣頻率只做到了33.3MHz,但是由于FIFO的容量較大,因此可以連續不同斷地采樣256k個點。這對于要求高速連續采樣的系統是非常適用的,而且省去了大容量的RAM,在一定程序上節省了硬件開支。

-

芯片

+關注

關注

453文章

50406瀏覽量

421835 -

轉換器

+關注

關注

27文章

8627瀏覽量

146869 -

濾波器

+關注

關注

160文章

7728瀏覽量

177685

發布評論請先 登錄

相關推薦

LTC1294單片12位數據采集系統

基于DSP和以太網的數據采集處理系統

基于DSP 和以太網的數據采集處理系統

基于SOPC的數據采集與處理系統設計

摩擦試驗機數據采集與處理系統設計

基于FIFO存儲器實現高速AD轉換器與ARM處理器的接口設計

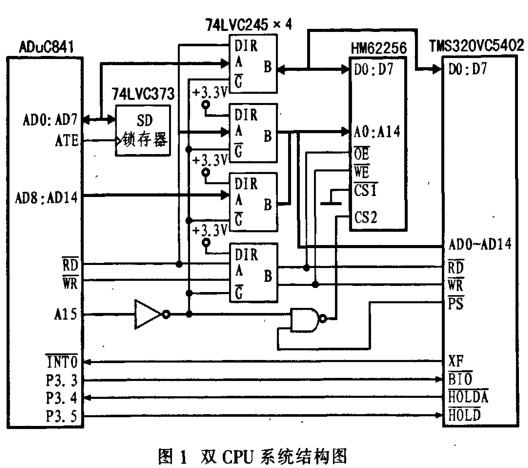

基于TMS320VC5402芯片和ADuC841轉換器實現數據采集處理系統的設計

基于12位模/數轉換器與FIFO芯片的數據采集處理系統

基于12位模/數轉換器與FIFO芯片的數據采集處理系統

評論