人的感覺器官中接受信息最多的是眼睛。為了存儲視覺信息,模擬視頻信號必須通過模擬/數(shù)字(A/D)轉(zhuǎn)換器轉(zhuǎn)變?yōu)閿?shù)字的"0"或"1",這個轉(zhuǎn)變過程就是所謂的視頻捕捉。

在數(shù)字圖像處理中,一般采用單片機控制芯片的I2C總線,而對數(shù)據(jù)的采集處理,則可以用專用的數(shù)字處理芯片DSP或FPGA進(jìn)行。隨著FPGA器件集成度的增長,完全有能力將ADV7183A的控制電路集成到FPGA內(nèi)部完成。這樣實現(xiàn)了設(shè)計的小型化、低功耗,并利用FPGA現(xiàn)場可編程特征充分發(fā)揮了ADV7183A的功能。

傳統(tǒng)上是利用I2C總線控制HS,VS和FIELD,并根據(jù)這3個信號的有效電平采集有效視頻,然而在不用I2C總線配置寄存器的情況下也可提取出有效視頻,因為在默認(rèn)配置下ADV7183A輸出的是8位BT656的YCrCb型4:2:2視頻數(shù)據(jù),可以根據(jù)BT656的標(biāo)準(zhǔn)提取有效視頻,這樣減少了編程工作,降低了FPGA與ADV7183A的連線,從而為FPGA控制其他芯片節(jié)約了引腳,提供了設(shè)計的靈活性。

1 設(shè)計方案

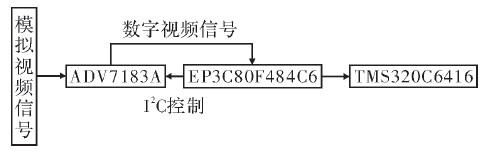

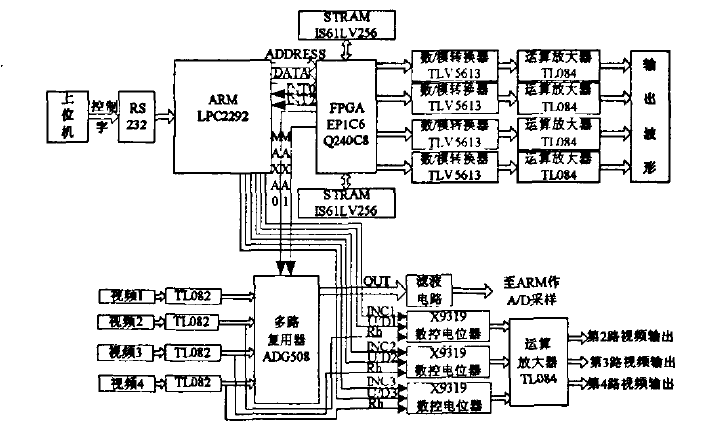

文中嵌入式數(shù)字圖像采集系統(tǒng)的硬件結(jié)構(gòu)如圖1所示。在此視頻采集系統(tǒng)中,采用Altera公司的Cyclone 3系列FPGA:EP3C80F484C6,AD公司的視頻解碼芯片ADV7183A,TI公司的TMS320C6416.模擬視頻信號PAL制輸入到ADV7183A中,由FPGA產(chǎn)生的I2C總線配置ADV7183A內(nèi)部的寄存器,控制ADV7183A輸出的像素時鐘頻率,行場復(fù)位起始位置、寬度以及數(shù)據(jù)寬度等。ADV7183A輸出的數(shù)字視頻信號經(jīng)過FPGA的預(yù)處理傳送到DSP,由DSP顯示圖像來驗證隔點采樣是否合理。

圖1 系統(tǒng)設(shè)計框圖

2 ADV7183A的設(shè)置

AD公司生產(chǎn)的ADV7183A是一款通用性強的視頻解碼芯片。芯片應(yīng)用的關(guān)鍵就是要設(shè)置ADV7183A內(nèi)部的一些寄存器,使ADV7183A能正常工作。而ADV7183A采用了I2C總線接口標(biāo)準(zhǔn),所以對該芯片的控制主要是通過I2C總線的數(shù)據(jù)傳輸。

對于本系統(tǒng)而言,取默認(rèn)配置,無需再對I2C總線進(jìn)行配置,當(dāng)ADV7183A正常工作后輸出8位BT656的YCrCb型4:2:2視頻數(shù)據(jù),只需320×256的灰度圖像,即取Y,而不要C,因此必須進(jìn)行隔點采樣。

(1)原理圖設(shè)計方案:給復(fù)位,使能和27 MHz的時鐘信號分別到RESET引腳,OE引腳,XTAL引腳,復(fù)位引腳和使能引腳都是低電平有效,通過FPGA控制這3個引腳來控制ADV7183A的工作。選擇模擬輸入通道AIN1,在AIN1引腳上輸入模擬信號。完成這些設(shè)置后,接上電源,ADV71 83就可以在默認(rèn)配置下正常工作,默認(rèn)配置為:輸入是PAL制的圖像。輸出是P8~P15的8位ITU-BT656的YCrCb型4:2:2視頻數(shù)據(jù),像素時鐘是LLCC1:27MHz。

(2)對于輸出的8位ITU-BT656,行數(shù)據(jù)由水平消隱,有效視頻開始定時信號,有效行數(shù)據(jù)以及有效視頻結(jié)束定時信號組成。幀數(shù)據(jù)由場消隱,第一場數(shù)據(jù),場消隱和第二場數(shù)據(jù)組成。場消隱和場數(shù)據(jù)分別由若干行數(shù)據(jù)組成,消隱數(shù)據(jù)為0X8010,即在水平消隱和場消隱時一律用16進(jìn)制的0X8010作為流數(shù)據(jù)。

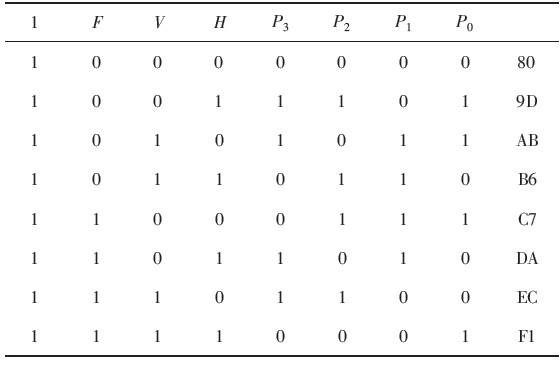

有效視頻開始(SAV)和有效視頻結(jié)束(EAV)為兩個定時基準(zhǔn)信號,每個定時基準(zhǔn)信號由FF 00 00 XY組成,前3個是固定前綴,第4個包含場標(biāo)識,場消隱和行消隱狀態(tài)的信息,其定義為:F為場同步信號,0其他情況,1表示場消隱;H為水平同步信號,0表示有效視頻開始,1表示有效視頻的結(jié)束,P0-P3稱為保護(hù)比特,它們的狀態(tài)取決于F,V,H的狀態(tài),如表1所示。

表1 保護(hù)比特狀態(tài)

(3)在此系統(tǒng)中沒有用HS,VS和F信號,即原理圖中沒有接這3個信號,而是根據(jù)ITU-BT656來截取需要的有效視頻數(shù)據(jù),依上文所述的有效視頻開始(SAV)和有效視頻結(jié)束(EAV)兩個定時基準(zhǔn)信號來截取圖像。

截取有效圖像:每幀分為奇場和偶場,兩場的圖像是一樣的,因此文中選擇只截取奇場。由表1可知FF 00 00 AB表示奇場場消隱的開始,F(xiàn)F 00 00 B6表示奇場場消隱的結(jié)束,F(xiàn)F 00 00 80表示奇場有效視頻的開始,F(xiàn)F 00 00 9D表示奇場有效視頻的結(jié)束,由于有效圖像總是先結(jié)束即EAV,然后開始SAV,因此首先檢測FF 00 00 AB,緊接著檢測第一個FF 00 00 9D,檢測到此認(rèn)為奇場場消隱已經(jīng)結(jié)束,再檢測FF 00 00 80表示奇場有效視頻的開始,再檢測FF 00 00 9D表示奇場有效視頻的結(jié)束,即需要的是FF 00 00 80和FF 00 00 9D之間的數(shù)據(jù),它們之間的數(shù)據(jù)為奇場的有效視頻數(shù)據(jù)。

隔點采樣:由8位ITU-BT656的格式可知,每幀的有效視頻數(shù)據(jù)為1 440×576,因此可知每行有1 440個數(shù)據(jù),包括Y和C,720個Y和720個C,C包括Cr和Cb.第一場即奇場為288行。隔點采樣方案,(1)行截取為:截取第一場的中間256行,即丟掉前后的各16行,由于截取有效視頻的時候包含了4個標(biāo)志位,即每行的數(shù)據(jù)為1 444,那么16行就是1 444×16個數(shù)據(jù),即在有效視頻開始后對于前面的1 444×16個數(shù)據(jù)進(jìn)行丟棄,而從第1 444×16個數(shù)據(jù)開始才是想要得到的數(shù)據(jù)。(2)列截取為:由于每行的Y為720個,而只需320個,因此隔點采樣,兩個時鐘取一個數(shù)據(jù),這樣的話是360個Y,同行截取一樣,取中間的320個Y,即丟掉前后各40個Y,由于每行還有C,因此每行開始丟掉40×2個數(shù)據(jù),從第40×2個開始,每兩個時鐘取一個數(shù)據(jù)進(jìn)行隔點取數(shù)據(jù)。直到達(dá)到想要的320×256個數(shù)據(jù),此時隔點采樣結(jié)束。

3 與DSP的傳輸

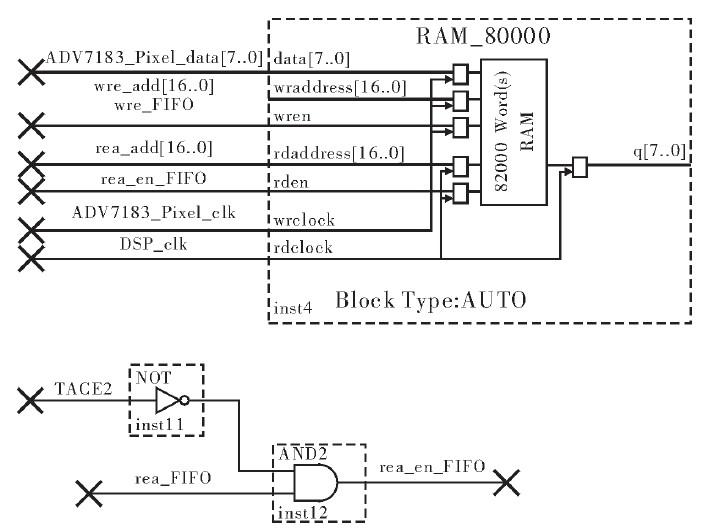

(1)將采樣得到的81 920個數(shù)據(jù)緩存到雙口RAM里面,再由DSP讀取,如圖2所示。

圖2 DSP與FPGA傳輸模塊

系統(tǒng)采用美國德州儀器公司推出的TMS320C6416.TMS320C6713是德州儀器公司推出的一款浮點型高性能DSP,開發(fā)工具為CCS,它與FPGA的傳輸主要通過中斷控制引腳GP5/.EXT-INT5,片選信號TACE2,AECLKOUT時鐘引腳,64位數(shù)據(jù)線,20位地址線,還有GPTO口。

設(shè)計方案中FPGA與DSP的傳輸選擇異步雙口RAM。

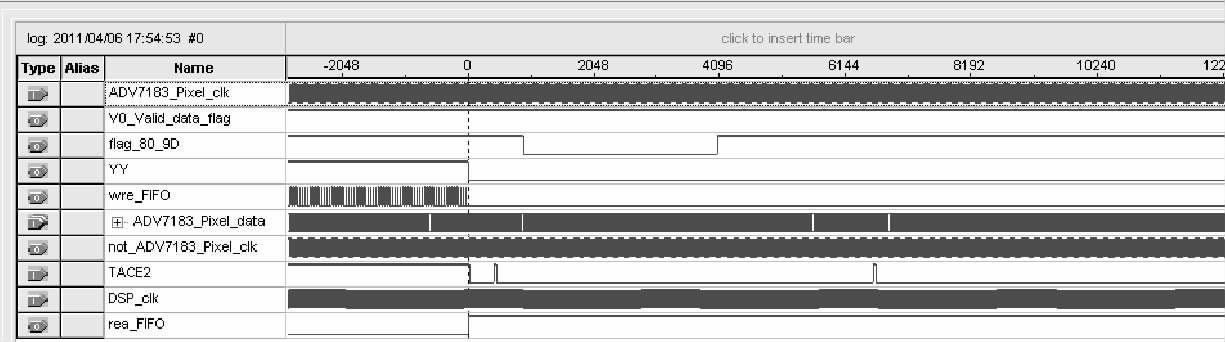

RAM設(shè)計:寫時鐘為LLCC1:27 MHz,寫使能為320×256有效數(shù)據(jù)期間,讀時鐘是DSP的時鐘,讀使能是寫完一幀圖像后開始讀,并由DSP的片選信號讀取,通過中斷來連接FPGA和DSP,寫完81 920個數(shù)據(jù)后給DSP的中斷控制引腳GP5/EXT-INT5發(fā)中斷,中斷可以是上升沿也可以為下降沿,此方案中選擇了下降沿,DSP在中斷控制引腳上檢測到下降沿后,DSP認(rèn)為收到中斷,開始讀數(shù)據(jù),片選信號TACE2有效,從收到中斷到TACE2有效,此期間會有一個延遲,但不影響讀數(shù)據(jù)。

DSP設(shè)計:數(shù)據(jù)線使用低8位,即AEDO-AED7,地址線不連接,與FPGA的通信設(shè)置為異步,設(shè)置讀取的數(shù)據(jù)為81 920,DSP在片選信號TACE2有效期間為DSP讀數(shù)據(jù),由于TACE2為低電平有效,而雙口RAM的讀使能是高電平有效,因此需要將片選信號取反后才能作為讀使能,DSP以100 MHz進(jìn)行讀數(shù),當(dāng)讀完后DSP的片選信號自動拉高。讀取數(shù)據(jù)結(jié)束,STP如圖3所示。

圖3 STP時序圖

(2)CCS可以根據(jù)圖像數(shù)據(jù)顯示圖像,因此把傳輸過來的數(shù)據(jù)進(jìn)行顯示,驗證采樣的正確與否。DSP讀完后顯示灰度圖像,相機拍出的原始圖像和隔點采樣后DSP顯示的圖像如圖4和圖5所示。

圖4 原始圖像

圖5 隔點采樣后

由圖中可以看出,采樣的數(shù)據(jù)可以很好地顯示攝像機所拍圖像,表明采樣方法是正確的。

4 結(jié)束語

本視頻采集系統(tǒng)利用FPGA對視頻解碼芯片進(jìn)行設(shè)置,具有小型化、低功耗、靈活性等特點,采用ADV7183A作為視頻解碼芯片。同時,作為視頻輸入前端,將彩色攝像頭的模擬視頻源轉(zhuǎn)換成8 bit的ITU-BT656的YCrCb型4:2:2視頻數(shù)據(jù),并進(jìn)行隔點采樣得到320×256的圖像,實現(xiàn)了FPGA與DSP的接口設(shè)計,將隔點采樣得到的數(shù)據(jù)傳輸給DSP,由DSP顯示圖像達(dá)到了設(shè)計要求,能夠為后來的去噪聲和背景抑制等濾波處理提供良好的數(shù)字視頻數(shù)據(jù)。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601864 -

芯片

+關(guān)注

關(guān)注

453文章

50406瀏覽量

421845 -

總線

+關(guān)注

關(guān)注

10文章

2867瀏覽量

87989

發(fā)布評論請先 登錄

相關(guān)推薦

基于FPGA和視頻解碼芯片的實時圖像采集系統(tǒng)設(shè)計

有關(guān)視頻解碼器ADV7183的知識速看

ADV611視頻編解碼芯片的原理與應(yīng)用

基于PCI Express實時視頻采集系統(tǒng)的設(shè)計

集成有10位ADC的增強型視頻解碼器ADV7183及其應(yīng)用

基于ADV7183A視頻采集系統(tǒng)的設(shè)計

如何使用FPGA和ARM設(shè)計和實現(xiàn)多路視頻采集系統(tǒng)

綜合視頻解碼器ADV7183的工作原理、特點及引腳功能分析

ADV7183A:多格式SDTV視頻解碼器數(shù)據(jù)Sheet

ADV7183:高級視頻解碼器,帶9位ADC,支持過時的組件輸入數(shù)據(jù)表

利用FPGA控制ADV7183A視頻解碼芯片進(jìn)行視頻采集系統(tǒng)的設(shè)計

利用FPGA控制ADV7183A視頻解碼芯片進(jìn)行視頻采集系統(tǒng)的設(shè)計

評論