引言

LDPC 碼最早于1962 年由Gallager提出,可以看成是一個具有稀疏校驗矩陣的線性分組碼。自從Mackay 和Neal發現LDPC 碼的性能非常接近香農限以后,LDPC 碼越來越受到人們的重視。基于準循環LDPC(QC-LDPC)碼結構特點,提出了一種支持多種碼率QC-LDPC 譯碼器的設計方法,并設計實現了一個能夠實時自適應支持三個不同H 陣的通用QC-LDPC 譯碼器。

1 QC-LDPC 碼簡介

QC-LDPC 碼的校驗矩陣Hqc是由c × t 個循環置換矩陣組成的,其中c,t均為整數,且c < t 。將QC-LDPC碼的校驗矩陣中每一個置換矩陣替換為相應的移位值,這樣得到了一個新的矩陣,稱為基本矩陣。基本矩陣與Η 陣是一一對應的。QC-LDPC 規則的結構使得其編譯碼在工程上易于實現,因此許多標準中的LDPC 碼都采用了QC-LDPC 碼。

2 譯碼算法簡介

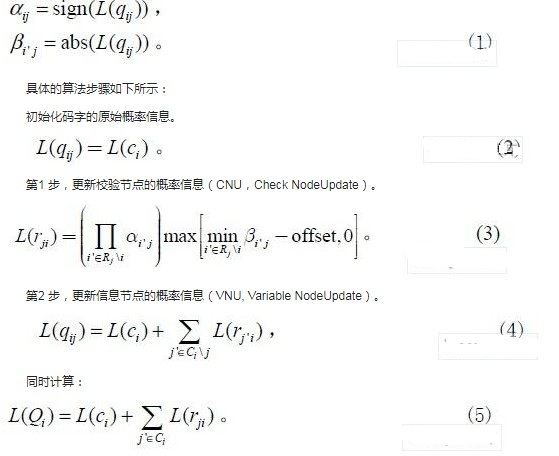

這里設計的譯碼器主要采用基于軟判決的偏移值最小和算法。偏移值最小和算法是在和積算法和最小和算法的基礎上改進而來,具有譯碼復雜度低,性能優異等特點。為了能夠較好地描述該算法,先對一些符號進行定義。

L(ci )表示輸入譯碼器變量節點i 的原始軟信息, L( rji) 表示由校驗節點j 傳遞給變量節點i 的信息, L(q ij )表示由變量節點i 傳遞給校驗節點j 的信息。而αij ,βi ' j 的意義如式1 所示:

L Q 進行硬判決,若( ) 0 i L Q > ,判決為0 否則為1。計算cHT 是否為0,或者已經達到設定的最大迭代次數,如果是轉第3 步,否則轉第1 步。

第3 步,輸出判決結果。

通過仿真,文中確定的譯碼器輸入定點化方案如下:量化位寬為6 bit,其中3 bit 表示整數位,2 bit 表示小數位。

3 多碼率LDPC 譯碼器設計

首先考慮下面3 種QC-LDPC 碼字作為參考,碼長8 064bit,碼率分別為7/8, 3/4, 1/2。其中,不同碼率的最小和譯碼算法所需的最佳偏移值((3)式中的offset 值)經仿真得到,分別為1, 0.7, 0.5。上述QC-LDPC 碼中所用到的碼型膨脹因子是112。

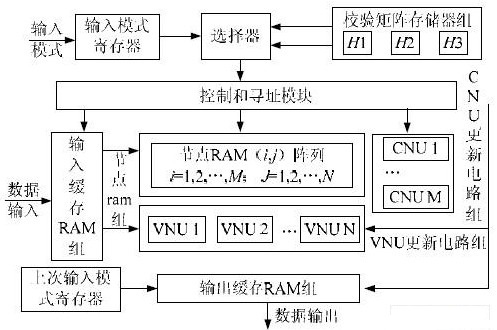

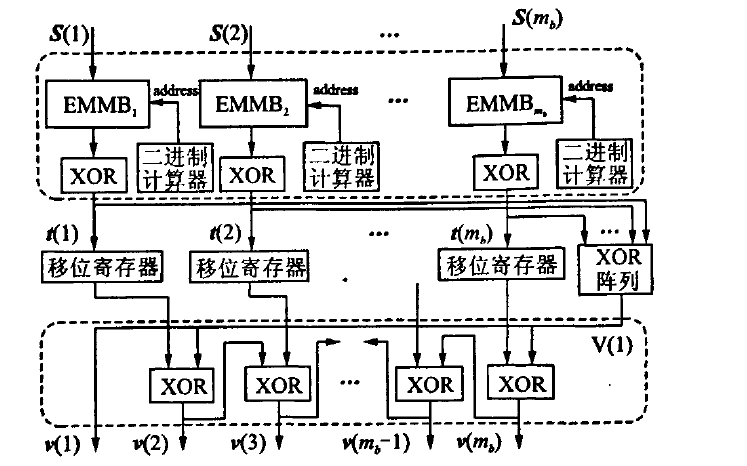

文中實現的LDPC 譯碼器基于部分并行的譯碼結構,對譯碼器進行了輸入輸出雙緩沖處理,支持數據連續處理,總體的結構如圖1 所示。

圖 1 譯碼器的總體結構

由于要支持三個不同H 陣的LDPC 碼,所以需要有一個模式端口,告知譯碼器當前數據塊是屬于哪個碼型。輸入模式寄存器控制選擇器選擇不同的H 陣來配置控制和尋址模塊,使其能選擇需要更新的節點RAM 和需要更新的校驗節點單元(CNU),變量節點單元(VNU)的電路套數。

輸入數據首先輸入到輸入緩存RAM 組中,輸入緩存RAM 組按照基本矩陣的列數分成N 塊對數據進行緩存,其中N 可配置,文中用到的N 是72。數據存滿一幀編碼塊后,就輸入到節點RAM 組中。節點RAM 組的作用是對算法迭代更新時的中間信息進行存儲。由于基本矩陣中有較多的零矩陣,所以實際生成的節點RAM個數遠小于M × N 個。

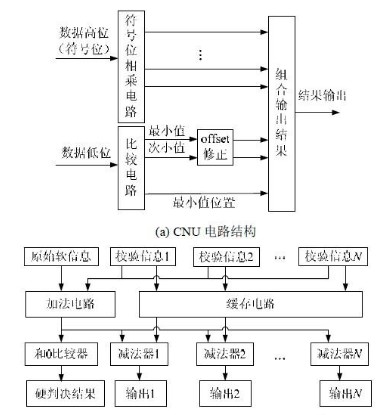

CNU 電路的用途是做校驗節點概率更新,完成式(3)的計算。實現結構如圖2(a)所示。VNU 電路的用途是做變量節點概率更新,同時計算硬判決結果,完成式(4)和式(5)的計算。

具體結構如圖2(b)所示。

圖2 CNU 和VNU 電路的結構

輸出緩存RAM 組用來存儲和輸出譯碼結果,同樣也采取了乒乓操作,支持數據塊連續的輸入輸出。控制和尋址模塊是譯碼器的核心模塊,它為譯碼器提供各種控制信號和讀寫RAM 的尋址信號。尋址模塊分為CNU 地址產生模塊和VNU 地址產生模塊兩部分,CNU 地址產生模塊的起始地址都是其偏移值;而VNU 地址產生的地址則都是從0 到Z。

由于采用了輸入輸出雙緩沖,所以譯碼器中最多可以存在三塊數據塊,同時這三塊數據塊可以是不同碼率的數據塊,這就實現了對連續輸入的不同碼率數據塊自適應譯碼的功能。

4 FPGA 實現以及性能測試:

根據以上設計方案,選用Verilog HDL 進行設計,同時采用了Modelsim 6.1b 進行了仿真驗證,最后在Stratix IIEP2S180F1020I4 芯片上進行了測試。具體見表1 所示。

表1 資源占用情況

表1 中同時也列出了一個單碼率譯碼器的資源占用(7/8碼率)。可以看出,該多碼率譯碼器在資源占用不超過2 種碼率譯碼器資源之和的前提下能夠有效支持3 種碼率。

同時,還針對每種碼率都測試了其吞吐率和運行的最高時鐘,其中三種碼率(1/2,3/4,7/8)工作最高時鐘均為110 MHz,最高吞吐率分別為110 Mb/s、165 Mb/s 和192.5 Mb/s。從該測試結果可以看出,該多碼率譯碼器吞吐率也在110 Mb/s以上,說明其在滿足自適應多碼率應用需求的同時,仍然保持了很高的譯碼吞吐率。

5 結語

針對QC-LDPC 碼特點,提出了一種多碼率QC-LDPC譯碼器實現方法,并用FPGA實現了此通用的多碼率譯碼器,可支持至少三種不同碼型的QC-LDPC 碼。此多碼率QC-LDPC 譯碼器的輸入輸出參數可以根據所需支持的碼型靈活配置,最終實現的譯碼吞吐率對任何碼率都可超過110 Mb/s,兼顧了多碼率譯碼器所需的靈活性和高吞吐量。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602043 -

芯片

+關注

關注

454文章

50460瀏覽量

421980 -

譯碼器

+關注

關注

4文章

310瀏覽量

50285

發布評論請先 登錄

相關推薦

一種通用的低成本QC-LDPC碼譯碼結構

大圍數QC_LDPC碼的譯碼器該怎么設計?

怎么實現RS編譯碼器的設計?

基于FPGA 的(3,6)LDPC 碼并行譯碼器設計與實現

最新LDPC譯碼器結構論文合集

IEEE 802.16e中LDPC譯碼器的實現

高碼率LDPC碼譯碼器的優化設計與實現

WIMAX LDPC碼譯碼器的FPGA實現

一種基于距離圖的QC-LDPC構造算法

基于FPGA 的LDPC 碼編譯碼器聯合設計

大列重低復雜度的QC-LDPC碼構造

如何使用FPGA實現結構化LDPC碼的高速編譯碼器

如何使用FPGA實現跳頻系統中的Turbo碼譯碼器

采用FPGA芯片實現多碼率QC-LDPC譯碼器的設計與測試

采用FPGA芯片實現多碼率QC-LDPC譯碼器的設計與測試

評論