-越來越多的消費應用開始在設計中集成流式視頻,結果引入了許多標準和專有的加密算法。但是加密方案以及實現方法不統一導致視頻接收設備在設計和支持方面存在巨大的挑戰。DeviceDNA作為FPGA的一項新功能,可保證視頻接收機的設計安全,同時還可為測試和驗證流程提供支持,從而提供成本經濟的高質量安全解決方案,支持多種不同的視頻流加密協議。

視頻越來越多地應用在我們生活中,除了在電視上的應用,還被應用在計算機、汽車、PDA/PMP、iPod和手機上。現在,甚至冰箱上可能也應用視頻!

消費者希望能夠隨時隨地享有視頻所帶來的便利,但是如此廣泛的視頻需求產生了大量不同的流式視頻壓縮標準,以滿足對不同屏幕尺寸分辨率以及高帶寬的要求。

要為這么多不同種類的設備提供視頻內容支持,因此在傳統有線電視和衛星供應商之外又誕生了許多新的視頻流提供源(以及相應的廠商)。電話線、因特網和無線通信,在支持流式視頻發展的同時也為流式視頻帶來了明顯的安全問題。為了解決這一問題,不同的流式視頻源引入并采用了越來越多的標準和專有加密算法。然而,不同廠商間加密方案以及實現方法不統一導致視頻接收設備在設計和支持方面存在巨大的挑戰。

FPGA提供靈活的解決方案

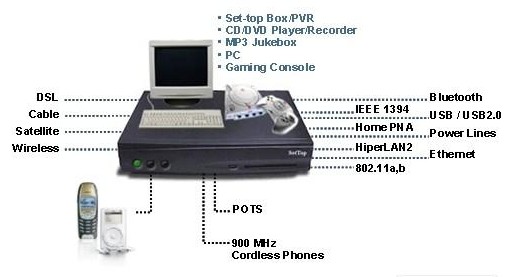

多年來,低成本FPGA器件已經成為機頂盒和視頻網關的關鍵器件,可提供視頻增強、丟失像素替換、視頻轉換、產品靈活性以及產品差異等功能。此外,這些器件還允許生產商方便地支持不同的技術和協議,如圖2所示。

FPGA平臺的傳統靈活性以及專用的算法功能是解決多種不斷變化的標準和專有加密算法的理想解決方案。器件重配置能力可以根據需要方便地改變解密算法。通過FPGA器件重配置,設計可利用更少的邏輯門和更少的器件,從而以更低的總體成本支持更多算法。現場可升級能力能夠快速方便地應對新算法和算法變化,因此可保證產品是未來適用的(future-proofing),并且不必進行昂貴的現場更換即可延長現有產品的壽命。

硬件安全問題

視頻源提供商的擔心已經不僅局限于視頻流本身的安全性,而是已經擴展到接收硬件的安全性。有些視頻源提供商正在設法將其許可和視頻流限定范圍定為能夠提供安全視頻接收機的系統。這需要很多企業尋求減少支持的數量并提高器件級的安全性,以進一步提高總體設計的安全水平。可編程邏輯器件生產商賽靈思公司提供的FPGA平臺則可解決這一問題。該平臺的DeviceDNA技術可提供支持多種解密算法的能力和更高的器件級安全性。

DeviceDNA允許設備生產商將一個獨一無二的非易失工廠序列號直接寫入到FPGA器件中。每個器件的ID都不同,因此可以將設計綁定到特定的FPGA器件中。DeviceDNA可以作為接收設備的獨特序列號,一個唯一的許可代碼,或者與用戶定義的寫在FPGA構造中的認證算法配合使用,從而將特定的設計與特定FPGA器件緊密綁定在一起。如果某些人試圖克隆或拷貝認證過的設計,或者將位流寫入另一片不同的FPGA器件,那么由于器件的ID號碼變化,設計就不會通過認證。DeviceDNA是一個57位長的序列號,可以通過器件內部的邏輯構造讀取。

DeviceDNA與用戶定義認證算法緊密結合能夠以合理的系統成本實現所需要的安全度。在采用認證算法的方法中,安全性的關鍵是算法本身。在本方法中,安全過程中必須有某些部分要保密,在本案例中則是用戶定義的算法本身。由于算法在PPGA邏輯構造中實現,因此成為FPGA數百萬配置位中的少數位。除非知道這些位如何組合在一起,或者知道算法本身,否則參于任何試圖拷貝設計的人來說,看起來都僅僅是一堆數字。

用戶定義的算法可以如系統所需要的一樣簡單或復雜 - 例如:可以是簡單的哈希算法,或者更為復雜的三次DES、AES6?、128或256位,甚至是完全定制的算法。同時還可以將用戶定義的認證算法集成到接收器的認證流程內部。這樣可以進一步將接收單元與視頻流系統、設計與特定的接收單元捆綁在一起,從而進一步提高抵抗克隆的安全能力。此外,算法可以改變以支持不同的視頻解密協議配置,甚至在不同型號或不同代產品間采用不同的算法,從而進一步保證安全性。

安全性提高對生產的影響

硬件安全性問題同樣適用于生產流程,特別是板級測試和驗證。因此,設計中經常將JTAG功能移除,因為JTAG功能易使設計導致反向工程。許多企業都采用JTAG來縮短測試時間并提高測量和驗證流程中的系統測試覆蓋范圍。然而,沒有JTAG,就需要更多的測試,特別是系統級測試來保證一定的測試覆蓋范圍。不使用JTAG技術會提高生產成本,并最終影響到系統總成本。

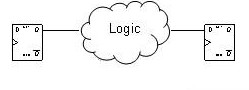

JTAG的問題在于INTEST命令,用于檢查設計的內部邏輯功能。反向工程時,這一命令可用來判斷設計的功能。圖3給出了一個簡單的例子,其中數據移入寄存器,執行INTEST命令,這樣數據會在時鐘作用下移入邏輯構造,進入下一寄存器,結果可以被讀出。由于可將總體設計的復雜度縮小到更小的邏輯模塊,因此這一命令可使反向工程的工作更容易。

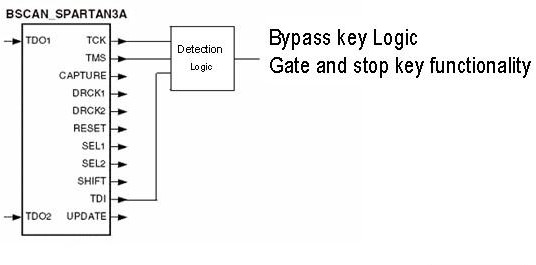

一些FPGA平臺可幫助防止發生這一過程,同時仍然允許生產商完成其管腳至管腳(pin-to-pin)功能。例如,在Xilinx? Spartan?-3A 平臺中, 可在設計中使用BSCAN_SPARTAN3A宏模塊,其檢測邏輯可監控FPGA構造中的JTAG控制信號,如圖4所示。如果檢測到JTAG控制信號的活動,用戶在設計可以立即繞過關鍵邏輯或關斷關鍵功能,不再執行正確的功能。這樣反向工程人員讀到的將是不正確的功能模塊,在不能完成預期功能的解決方案上浪費時間和資源。

支持DeviceDNA的FPGA平臺可保證視頻接收機的設計安全,同時還可為測試和驗證流程提供支持,從而能夠提供成本經濟的高質量安全解決方案,支持多種不同的視頻流加密協議。

-

FPGA

+關注

關注

1626文章

21670瀏覽量

601875 -

視頻

+關注

關注

6文章

1934瀏覽量

72814 -

計算機

+關注

關注

19文章

7424瀏覽量

87719

發布評論請先 登錄

相關推薦

為DTV地面廣播接收機選擇高質量的解調解碼芯片

ARM核在GPS接收機的解決方案

R&S監測接收機開展5G測量的應用文檔

漢威智慧安全綜合服務解決方案為安全生產高質量發展保駕護航

AC/DC電源模塊:高質量的電力轉換解決方案

視頻接收機的高質量安全解決方案

視頻接收機的高質量安全解決方案

評論