采用基于現場可編程門陣列(FPGA)的原型的驗證團隊面臨的最大挑戰之一在于當原型系統未能發揮期望的性能時了解原型系統的內部行為。分析和調試這些設計的一個關鍵因素是難以觀察內部信號。

目前的頂級FPGA在容量和性能方面均提供巨大的能力。例如,Xilinx Virtex-5家族成員包含成千上萬可以配置成邏輯、RAM或移位寄存器的邏輯單元。此外,這種可編程邏輯可與硬IP塊搭配使用,如工作頻率全部高達550MHz的兆位RAM以及數百個25×18乘法器/DSP功能。

這些可能還包含多個硬和/或軟處理器內核和相關外圍器件的設備可以用作ASIC和片上系統(SoC)元器件的功能強大的原型平臺。

新工具、改進的方法以及更高的抽象級正在幫助工程師實踐不同的宏架構和微架構,并幫助他們提高其總設計生產力。

對于驗證而言,這些設計的絕對規模和復雜度再加上大幅增加的軟件內容使得FPGA原型對于通過硬件加速提高驗證吞吐能力以及提供一個早期的軟件開發平臺都是一個極具吸引力的選擇方案。但是,成功的原型要求當設備無法按預期工作時對發生的狀況和工程師必須調試的對象予以應有的考慮。

如上文所述,分析和調試原型設計的關鍵因素在于難以觀察內部信號。問題在于可能有成千上萬個這樣的信號,但是這些信號可能僅通過設備上的有限個輸入/輸出(I/O)引腳暴露在外界。

此外,觀察內部信號的操作會影響設計和驗證。選擇要監視的合適信號是一個并不瑣細的任務,修改設計以觀察這些信號會耗費工程和FPGA資源。同樣,捕獲、轉出和記錄要觀察的信號值也要花時間。

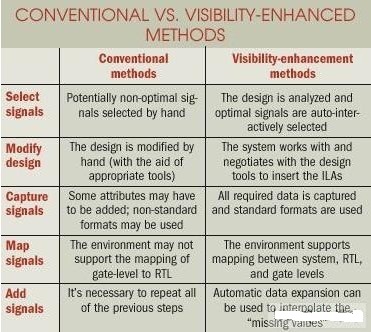

訪問和分析FPGA內部信號的任務復雜、繁瑣而耗時,這取決于所用的方法。話雖如此,不過總過程也可以分成五個主要步驟:1. 確定一組要觀察的信號;2. 修改設計,以觀察所選的信號;3. 當FPGA在原位工作時觀察并找回數據;4. 將找回的數據映射至最初的RTL表示法;5. 計算不在最初觀察的信號組中的其它信號的數據。

本文首先討論與執行這些活動有關的現有技術的局限性。然后介紹新興的可視性增強技術;這種新的技術包括一組縮減的要觀察的信號的自動交互選擇以及填充“遺漏片段”(未觀察到的信號值)的“數據擴展”技術。

傳統技術的局限性

就像剛才提到的,采用傳統技術定位、分析和調試FPGA中的問題可能極其繁瑣和耗時。其中的原因可以簡單地進行總結。

這個過程的第一步是決定哪些信號需要進行觀察(捕獲和轉出)。但是要觀察的信號量的增加會增加捕獲信號所需的邏輯資源以及將其數據值傳達給外界所用的時間。由于這些原因,因此可能只能在特定時間(即特定的驗證運行)觀察有限個信號。

這里的問題在于選擇要監視的最佳信號是一個并不瑣細的任務。例如,看起來是監視的最佳選擇的寄存器可能實際上只能為設計的操作提供有限的可視性。相比之下,表面上無害的寄存器可能為設計提供極高的可視性。

一旦選定一組要監視的信號,必須對設計進行修改以便允許直接觀察信號,或者允許捕獲信號并將其轉出到外界。廣義上講,這叫可調試性設計(Design-for-Debug,DFD)。在以前的技術案例中,設計可以通過多路復用器和控制邏輯進行擴展,多路復用器和控制邏輯可以用來通過主要輸出引腳來將所選的內部信號呈現到外界。一般而言,這種技術實現往往是一種內部的專門技術,這些實現需要大量工作來有限地了解芯片內部正在發生的狀況。

替代技術是采用內部邏輯分析儀(ILA)。這些分析儀可能是內部技術,但是FPGA供應商或專業的第三方供應商一般都提供這些分析儀(以及相應的配置應用)。每個ILA都是采用可配置邏輯單元和RAM區塊的組合而構造的。ILA的控制邏輯被設計成允許特定的觸發條件(或組合的觸發條件)開始捕獲一個或更多特定信號并將與這些信號相關的屬性(如數據值和時間戳記)存儲在片上內存中。在某個階段,這些值必須被轉出到外界。這種情況下的一般技術是采用芯片的JTAG端口。

設計你自己的ILA不僅耗時而且費力。事實上很難確定是自動調試設計的還是ILA在調試設計。甚至在使用FPGA供應商的經過驗證的魯棒ILA時,每次選定要監視的一組新的信號時仍然需要對設計進行重新編譯。重新編譯的工作可能要花幾個小時,因此最好最大限度地減少需要執行這個任務的次數。

在設計修改和設計重新編譯階段之后,進行驗證運行,并捕獲來自內部信號的數據。為了讓這些數據可用于下游調試工具,數據必須包含特定的屬性。除了數據本身的邏輯值之外,數據必須包含信號的完整分層實例名以及每個數據轉換的相對操作時間(時間戳記)。此外,轉出數據的文件格式應為工業標準,如VCD或FSDB。

在專有解決方案案例中,有必要將這些屬性添加到信號數據流和/或將內部格式轉換成其對應的工業標準格式。幸運的是,FPGA供應商和專業供應商提供的ILA一般捕獲必需的數據并使用工業標準格式。

從ILA收集的數據通常與FPGA的門級視圖有關。但是設計工程師更熟悉設計的RTL表示法。因此,為了為調試過程提供便利,有必要將門級實例映射成RTL視圖。這并不像聽起來那樣簡單,因為大多數情況下,門級實例和RTL視圖之間并沒有一一對應關系。許多傳統的內部解決方案都無法提供這種能力。

驗證運行之后,訪問和分析其它信號以對問題進行跟蹤始終都是有必要的。當采用傳統設計流程時,設計工程師必須返回上述五個步驟中的第一步。即,他們必須選擇一組新的信號、修改設計并對其進行重新編譯、執行新的驗證運行、將新數據映射至RTL,然后分析結果。這個過程必須重復多次。

可視性增強技術

為了解決傳統FPGA原型調試環境的局限性,出現了一種為設計的內部工作提供增強可視性的技術。為了達到完全的效果,可視性增強工具和技術必須應用于流程中的每一個步驟。

如上所述,過程中的第一步是確定哪些信號需要觀察。根據系統展示的不正確輸出,設計工程師通常對相關的一個或多個功能區塊有“感覺”。例如,內存控制器和/或總線仲裁器區塊。

作為單靠經驗和實踐的方法,你需要能夠觀察區塊(通常為寄存器、內部內存定位和區塊的主要輸入/輸出)內部大約15%的信號。這將在本小節后面討論的自動數據擴展技術環境中提供95%~100%的可視性。

遺憾的是,資源限制不允許捕獲所有這些信號。在這種情況下,選擇為振動提供最佳碰撞的信號顯然是更可取的。因此,可視性增強信號選擇包括“影響能力”的概念,即每個信號影響的下游邏輯的量。為了確定調試所選區塊所需的基本信號最小陣容,你將必須分析斷言、RTL或門級網表代碼,有時這三項都需要關注以*估影響能力。例如,為了調試斷言故障,可視性增強信號選擇將分析設計和所選的斷言,以抽取調試每個斷言所需的最小的一組信號。

此外,如果設計工程師對他們希望觀察的一組信號進行了明確的定義(這樣的選擇可以在RTL和/或門級網表中進行),可視性增強信號選擇工具將自動識別任何寄存器、內存元件以及觀察指定的內部信號所必須捕獲的主要I/O。

一旦選定一組要監視的信號,可視性增強環境將自動與FPGA和/或第三方工具供應商溝通,以通過增加適當的ILA來修改設計。在沒有足夠的資源捕獲所有所需信號的情況下,可視性增強環境將以被認為具有更多上述影響能力的信號作為其選擇的基礎。

在執行驗證運行時,可視性增強環境將自動記錄和/或提供下游分析和調試環境所需的所有信息;該信息將包括邏輯值、信號的完整分層實例名以及數據轉換的相對操作時間。此外,轉出數據文件的格式將為工業標準格式,如VCD或FSDB。

正如上文指出的,從ILA收集的數據通常與FPGA的門級視圖有關。為了了解這種門級邏輯中發生的狀況,工程師必須使門級數據與設計的RTL表示法相互關聯,甚至與系統級描述相互關聯。

但是,由于合成和優化的原因,并非門級表示法中的每個信號均有RTL表示法的相應信號。為了解決這個問題,可視性增強環境必須以某種方式地方化信號相關性。其中一個方法是自動生成結構依賴圖像并采用近似的圖像匹配算法。這個方法模仿人類使用的過程,人類通常通過查看扇入區和扇出區中的寄存器來定位相應區域。

或許可視性增強最重要的方面在于其動態數據擴展能力。但是這種能力依賴于所有上述要點,特別是可視性增強信號選擇。選擇要觀察的信號的宗旨就是為了便于自動數據擴展。

以下是數據擴展的思路。通常,設計工程師可能希望顯示和分析不在被捕獲的信號組中的信號。較可取的做法是插入遺漏的數據,而不傾向于修改設計和執行新的驗證運行。因此,可視性增強環境將通過數據擴展來填充捕獲數據中遺漏的間隙。

特別地,這種數據擴展可以填充位于信號被捕獲的寄存器之間的組合邏輯區塊內部的信號。為了最大限度地提高性能,只對進行試驗的邏輯進行動態的數據擴展,而不是對所有設計邏輯進行靜態的數據擴展。傳統設計環境與其可視性增強環境的對比如表所示。

可視性增強技術可以極大地加快定位、隔離和了解基于FPGA的原型中的錯誤癥狀原因的過程(類似的技術可以應用于基于FPGA的仿真和軟件仿真中)。

在一般的設計中,寄存器約占信號的20%。采用可視性增強技術允許設計工程師將這些信號作為確定余下80%信號的值的基礎,這相當于可視性提高了大約五倍。而據使用這種技術的用戶報告,調試時間減少了四倍。換言之,在不使用可視性增強技術的情況下調試所用的每一個小時在使用該技術之后都可以縮短至僅15分鐘。

就未來而言,可視性增強環境提供的數據擴展能力為將內部FPGA信號數據與一般只在軟件仿真環境下考慮的先進調試技術搭配使用提供了基礎。例如,如果設備包含復雜的內部總線,擴展的數據可能會在事務級被查看,從而使了解設備的操作更加容易。在調試器環境中謹慎地集成數據擴展技術可以同時縮短驗證運行時間和最終的捕獲數據文件大小。這種環境將實現自動化向導調試以及先進的分析和跟蹤能力。

本文小結

使用基于FPGA的原型的設計和驗證團隊所面臨的最大挑戰之一是當系統未能按期望執行時了解系統的內部行為。可視性增強驗證和調試環境通過以下方式解決了這個問題:幫助選擇要觀察的信號;與其它工具配合工作(和協商),從而對設計進行修改以捕獲所選的信號;捕獲所有驅動下游工具必需的數據和屬性;使用先進的技術在系統、RTL和門級視圖之間自動映射;執行數據擴展以填充未被捕獲的信號的值。

-

處理器

+關注

關注

68文章

19178瀏覽量

229200 -

FPGA

+關注

關注

1626文章

21678瀏覽量

602018 -

寄存器

+關注

關注

31文章

5325瀏覽量

120052

發布評論請先 登錄

相關推薦

解鎖SoC “調試”挑戰,開啟高效原型驗證之路

微通道反應器目前的局限性

工業無線化解決方案的產品構建及特點(MWB524F網橋+FBG1000邊界網關)

FPGA的優勢及潛在局限性介紹

一種用于化學和生物材料識別的便攜式拉曼光譜解決方案

高光譜成像技術如何改善現有遙感技術的局限性?

超導材料在輸電領域的應用前景、優勢和局限性

什么是FPGA原型驗證?FPGA原型設計的好處是什么?

淺析FPGA的調試-內嵌邏輯分析儀(SignalTap)原理及實例

FPGA原型調試環境局限性的解決方案分析

FPGA原型調試環境局限性的解決方案分析

評論