1 引言

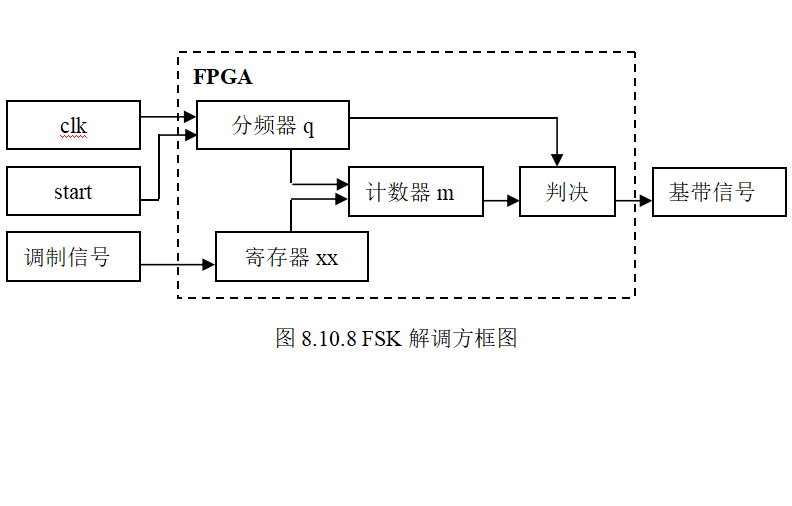

脈沖編碼調制(Pulse Code Modulation,簡稱PCM)是一種概念簡單、理論完善的編碼系統,其最大特征是把連續的輸入信號變換成在時間和振幅上都是離散量,然后再變換為代碼傳輸。信息為數字信號,在遠距離再生中繼傳輸中不積累噪聲,從而提高了通信系統的有效性、可靠性和保密性。利用現場可編程門陣列(FPGA)和VHDL 語言實現了PCM碼的解調,這樣在不改變硬件電路的情況下,能夠適應PCM碼傳輸速率和幀結構變化,從而正確解調數據。

2 硬件電路設計

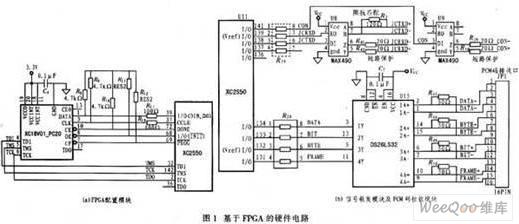

圖1給出基于FPGA的硬件電路。其中,圖1(a)為FPGA配置模塊;圖1(b)為信號收發模塊及PCM碼接收模塊。

該系統設計中FPGA選取Xilinx公司的Spartan系列XC2S50器件。該器件有4種工作模式,分別為主串模式、從串模式、邊界掃描和從并模式。將M0,M1,M2接地,使其工作在主串模式下。FPGA由存儲在片內RAM中的程序設置其工作狀態,工作時需要編程設置片內的RAM。用戶可根據不同的配置模式,采用相應的編程方式。上電時,FPGA將EPROM中的數據寫入片內編程RAM,配置完成后,FPGA進人工作狀態。掉電后,FPGA內部邏輯消失,恢復成白片。因此,FPGA能夠反復使用且無需專用的編程器,采用通用EPROM,PROM編程器即可實現。當需要修改FPGA功能時,只需換一片EPROM。同一FPGA根據不同的編程數據能夠產生不同的電路功能。該系統在發送方接收到請求信號后則開始發送數據。PCM碼解調模塊在移位脈沖同步下接收數據,并將串行數據轉換為并行數據存人FIFO中。每接收到一次請求脈沖發送一幀數據,每幀數據以146FH為結束標志字,EB90為子幀同步字,當PCM碼解調模塊檢測到幀尾后停止解調,并停止向FIFO寫人數據。PCM碼解調模塊由硬件描述語言編寫并集成于FPGA中。

3 PCM碼解調程序模塊

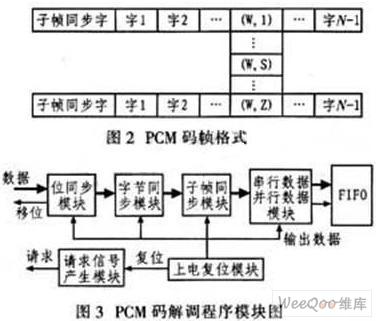

圖2給出PCM碼幀格式。其中N為子幀中的字數,最大值為1 024;Z為一幀所含子幀個數,最大值為256。子幀同步字字長為16~32 bit,字長度為4~16 bit。在遙測系統中,依照PCM碼幀格式,將所要測控的參數放在格柵中自定義位,同時定義子幀同步字和字長。當發送請求信號,同步接收一幀數據,即使一幀數據接收錯誤,也不影響下一幀數據解調的正確性,進一步減小誤碼率。檢測子幀同步字時,先找到一個子幀同步字后,每隔N個字節判斷移位數據是否為子幀同步字,對每一個子幀都進行判斷,即使第一次誤判,或當PCM發送中斷后再重發,也不會影響后續正確解調數據。可根據子幀同步字、幀尾標志字和請求信號的順序由該解調數據模塊進行自我糾正,從而大大降低了誤碼率。圖3為PCM碼解調程序模塊圖。

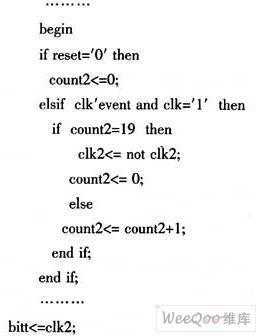

3.1 移位脈沖產生程序

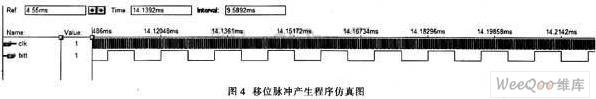

系統設計要求移位脈沖頻率為80 kHz,對時鐘脈沖進行40分頻。移位脈沖產生程序仿真圖如圖4所示。其中,bitt為位同步移位脈沖。

3.2 字節同步信號產生程序

設b為一個標志位,當b為‘1’時,表示檢測到請求信號的上升沿且尚未結束一幀傳輸,該進程的byte為字節同步信號,用來標志一個字節接收完畢。字節同步信號產生程序仿真圖如圖5所示。

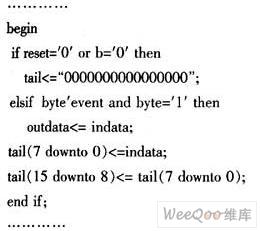

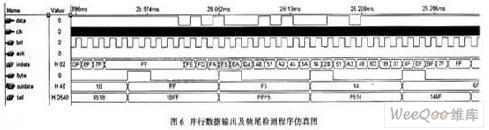

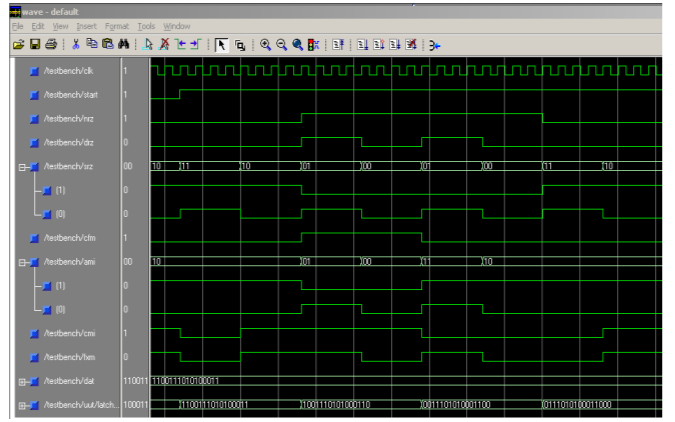

3.3 并行數據輸出及幀尾檢測程序

并行數據在字節同步信號byte的上升沿輸出,outdata為并行數據輸出端,同時將并行數據賦值給幀尾標志tail的低8位,將tail的低8位給其高8位,當tail的值為146F時,即表示一幀結束。并行數據輸出及幀尾檢測程序仿真圖見圖6。

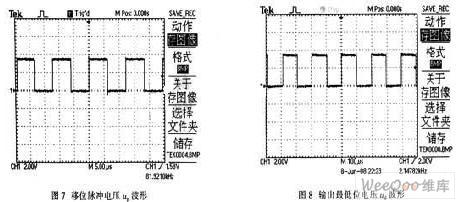

4 調試結果

所發送數據是以00H為起始遞增的一串數據,該數據字長200,結尾以146F為標記。調試過程中,南示波器觀察波形,可以看到請求信號的頻率及脈寬、移位脈沖的頻率均符合要求,解調出的并行數據與數據源的數據相吻合。圖7和圖8分別給出移位脈沖電壓up波形和輸出最低位電壓ud波形。

5 結語

基于FPGA的PCM碼解調電路VHDL程序模塊設計,可使電路在發出請求脈沖后,在移位脈沖的作用下,同步接收PCM數據,并輸出8位并行數據,在幀尾處結束解調。通過仿真及最終電路調試驗證了該系統設計能夠實現PCM碼解調系統功能。

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601895 -

vhdl

+關注

關注

30文章

816瀏覽量

128078 -

PMC

+關注

關注

0文章

89瀏覽量

14886

發布評論請先 登錄

相關推薦

FPGA的VHDL程序基本結構是怎樣的?FPGA的VHDL程序設計單元關系圖

基于VHDL方式實現了QPSK數字調制解調電路的設計

可編程GOLD碼的VHDL實現

基于VHDL的QPSK調制解調系統設計與仿真

實現PCM碼解調系統的VHDL程序模塊設計

實現PCM碼解調系統的VHDL程序模塊設計

評論