1 引言

近年來,多通道面陣 CCD相機(jī)在氣象觀測、環(huán)境檢測、海洋遙感和資源調(diào)查等領(lǐng)域獲得了廣泛的應(yīng)用。而在 CCD的應(yīng)用技術(shù)中,尤其是高速、多通道 CCD的應(yīng)用中, CCD驅(qū)動時序的產(chǎn)生和信號的實時輸出是兩個非常關(guān)鍵的問題[1]。高速、多通道 CCD器件的驅(qū)動時序通常是一組周期性且關(guān)系比較復(fù)雜的脈沖信號,它是影響 CCD器件性能的一個重要因素;而產(chǎn)生的多組像元信號如何正確的轉(zhuǎn)換成一幀完整圖像,也必須根據(jù)實際的硬件要求而采取不同的設(shè)計方案。

本文在分析了 Sarnoff公司的 VCCD512H型幀轉(zhuǎn)移面陣 CCD芯片的特性和工作過程后,結(jié)合整個 CCD相機(jī)電子系統(tǒng)的要求,完成了基于 FPGA技術(shù)的驅(qū)動時序發(fā)生器與數(shù)據(jù)緩存器的一體化設(shè)計,即在一塊 FPGA芯片上實現(xiàn)對時序與數(shù)據(jù)緩存系統(tǒng)的控制。昀后針對 Xilinx公司的 FPGA器件 XQ2V3000對設(shè)計進(jìn)行了配置及仿真,從而驗證了該設(shè)計方案的可行性。 2 驅(qū)動時序發(fā)生器與數(shù)據(jù)緩存器一體化設(shè)計原理

2.1 CCD器件結(jié)構(gòu)及工作原理

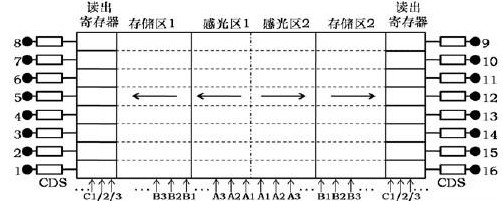

美國 Sarnoff公司的 VCCD512H是背照型幀轉(zhuǎn)移面陣CCD,它由兩個感光區(qū)、兩個存儲區(qū)和讀出寄存器構(gòu)成。每個感光區(qū)(或存儲區(qū))包含 8個子陣列,每個子陣列含有 256(行)×64(列)個有效像元,整個像面則由16個子陣列,共 512×512個有效像元構(gòu)成,我們在應(yīng)用中,對像元做了水平方向‘二合一’處理,使得整個像面共由 512x256個有效像元構(gòu)成,昀終 16路信號并行輸出。

電荷移動方向如圖1中箭頭所示,先由感光區(qū)轉(zhuǎn)移到存儲區(qū)(A1,A2,A3為幀轉(zhuǎn)移控制信號),再由存儲區(qū)轉(zhuǎn)移到讀出寄存器(B1,B2,B3為行轉(zhuǎn)移控制信號),而后在讀出控制信號(C1,C2,C3為像元轉(zhuǎn)移控制信號)的作用下順序讀出。16個子陣列有各自獨立的讀出寄存器和 CDS放大器。信號的輸出方式是 16個端口并行輸出,送到后續(xù)的模擬、數(shù)字信號處理電路[2]。

2.2 驅(qū)動時序分析

由芯片結(jié)構(gòu)可知,CCD的一個工作周期分兩個階段:感光階段和轉(zhuǎn)移階段。在感光階段,感光陣列接受外界光源照射產(chǎn)生電荷,幀轉(zhuǎn)移控制信號 A不變,感光陣列和幀存儲區(qū)之間為阻斷態(tài),不會發(fā)生電荷轉(zhuǎn)移現(xiàn)象;同時由行轉(zhuǎn)移控制信號 B控制,存儲區(qū)中的電荷逐行轉(zhuǎn)移到轉(zhuǎn)移寄存器;行轉(zhuǎn)移時,像元轉(zhuǎn)移控制信號 C不變,無像元信號輸出;每行信號中,各像元電荷逐次經(jīng)過輸出放大器輸出,每讀出一行信號,進(jìn)行一次行轉(zhuǎn)移。三相 CCD中,電荷的轉(zhuǎn)移是通過三相控制電壓按一定順序依次變化來實現(xiàn)的。此處,進(jìn)行電荷轉(zhuǎn)移時,三相控制時序依次變化;三相信號不變時,為阻斷態(tài)。為保證信號電荷的完整轉(zhuǎn)移,各相時序間必須保證一定的電平交疊[3]。

在幀轉(zhuǎn)移階段,幀轉(zhuǎn)移控制信號 A與行轉(zhuǎn)移控制信號 B相同,且一直有效。同時像元控制信號 C也一直有效,但輸出數(shù)據(jù)無效。進(jìn)入感光階段,首先進(jìn)行一次行轉(zhuǎn)移,開始信號的輸出,同時感光區(qū)像元進(jìn)入電荷積累。為保證信號讀出的完整性,整幀轉(zhuǎn)移的行數(shù)、輸出的行數(shù)、像元數(shù)都進(jìn)行了一定的冗余設(shè)置[4]。

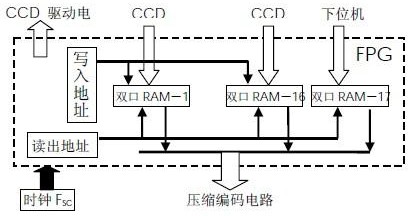

2.3 數(shù)據(jù)緩存器工作原理 如圖 2所示,CCD傳感器為 16路并行輸出,每路為 256×32×12bit,即8192×12 bit,現(xiàn)采用 VHDL硬件描述語言,設(shè)計實現(xiàn)了一種基于片上集成的雙口 RAM緩存器。

本設(shè)計中選用的控制器件FPGA為Xilinx公司XQ2V3000,其片內(nèi)的共有96個雙口 RAM,每個 RAM的深度為16K,而在該系統(tǒng)中為了實現(xiàn)幀緩存的功能,在設(shè)計中采用了兩個雙口 RAM并行連接的方式,從而組合成了 16K×16bit的雙口 RAM緩存單元,共占用 RAM資源34個。雙口 RAM的寫入地址為 14位,由寫入地址發(fā)生器統(tǒng)一提供,與 CCD的驅(qū)動波形相配合 [5]。具體實現(xiàn)時是將雙口RAM 分成上下兩區(qū)(每個緩沖區(qū)共有 64x266個像元),前一幀周期左邊寫上半?yún)^(qū),右邊讀下半?yún)^(qū);后一幀周期,左邊寫下半?yún)^(qū)時,右邊讀上半?yún)^(qū)。其寫入過程為:首先由A 、B三相驅(qū)動脈沖(共 266個波形)配合,完成 A->B的電荷轉(zhuǎn)移;然后用 B波形完成兩次 B->C轉(zhuǎn)移(兩行合并),再用 C波形完成72次串出,其中僅有 64個有效(第 3-66像元),其余為過掃描,用于行箝位。這一過程重復(fù) 133次,(前 5次丟棄)。 因為圖像數(shù)據(jù)的讀出要按預(yù)定順序,即 512行從上到下,每行 256個像元從左到右。為此,將 17個雙口 RAM的輸出作為一個整體來考慮,其存儲量為(512×256+128)×12 bit,即131,200×12 bit,需要18 位地址,該讀出地址的形成可以用一個18 位計數(shù)器和一個譯碼器完成 [6]。

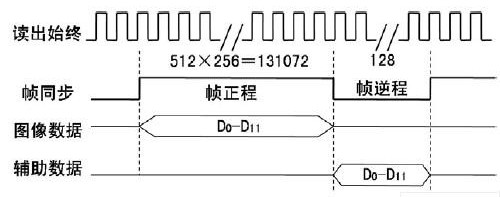

如圖 3所示,在幀正程期間,從數(shù)據(jù)緩存讀出 512 × 256 × 12bit的圖像數(shù)據(jù),在幀逆程期間,緩存器中的輔助數(shù)據(jù)緊隨其后被讀出。

3 一體化設(shè)計的 FPGA實現(xiàn)及仿真結(jié)果

3.1 現(xiàn)場可編程門陣列(FPGA)

系統(tǒng)中采用容量比較大的FPGA,利用 VHDL硬件描述語言完成 CCD驅(qū)動時序的設(shè)計和數(shù)據(jù)的高速讀寫。這種實現(xiàn)方法可以使采集系統(tǒng)靈活、簡單、方便,具有很強(qiáng)的可擴(kuò)展性,可根據(jù)需要設(shè)計為不同數(shù)據(jù)寬度、不同容量的數(shù)字系統(tǒng),接口電路簡潔且不占用系統(tǒng)地址資源,系統(tǒng)移植或升級換代方便,而且控制簡單,易于實現(xiàn)[7]。

3.2 時序仿真結(jié)果

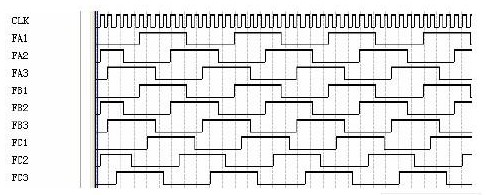

在編程軟件 Quartus II集成設(shè)計環(huán)境下,用 VHDL語言以自上而下的方式,對 CCD驅(qū)動時序和數(shù)據(jù)緩存系統(tǒng)進(jìn)行了描述,仿真后得到部分結(jié)果如下圖所示。

圖 4為在幀轉(zhuǎn)移過程中,通過對時鐘 CLK的計數(shù)而產(chǎn)生了頻率相同、相位不同的A、B驅(qū)動脈沖信號,并且通過后續(xù)的示波器檢測得知電平交疊達(dá)到了75%以上,滿足技術(shù)手冊的要求。

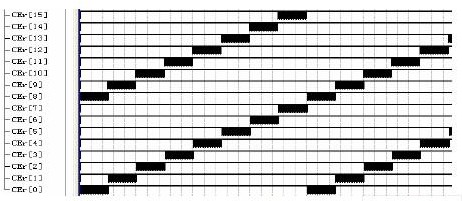

圖 5為 RAM選擇地址仿真圖。系統(tǒng)總共有 17個 RAM緩存器,并且把每個 RAM分為了上、下兩個半?yún)^(qū)。設(shè)CEr為 16位用來選擇 RAM的位置,其中高8位為上半?yún)^(qū),低 8位為下半?yún)^(qū),并且交替選擇(上半?yún)^(qū)讀出時,下半?yún)^(qū)為寫入,反之亦然)。從昀終的仿真圖中可以看出,時序復(fù)合設(shè)計要求。

4 結(jié)束語

本文的創(chuàng)新點在于采用了 FPGA技術(shù)設(shè)計 CCD驅(qū)動時序和緩存器電路,使原來復(fù)雜的電路設(shè)計變成只需 1片 FPGA就能完成。同時它能夠很好地滿足 CCD應(yīng)用向高速、小型化、智能化、低功耗發(fā)展的需求,從而提高了系統(tǒng)的集成度。從時序仿真結(jié)果來看,該一體化的設(shè)計能夠較好的產(chǎn)生器件所需的時序脈沖及緩存器所需的讀/寫地址,并且由于使用了延遲量小的 FPGA使得系統(tǒng)可以工作在百兆赫茲的工作頻段,從而增強(qiáng)了電路的抗干擾能力,提高了系統(tǒng)的可靠性與穩(wěn)定性。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21670瀏覽量

601877 -

寄存器

+關(guān)注

關(guān)注

31文章

5321瀏覽量

120016 -

發(fā)生器

+關(guān)注

關(guān)注

4文章

1363瀏覽量

61623

發(fā)布評論請先 登錄

相關(guān)推薦

智慧園區(qū)一體化管理平臺的功能應(yīng)用

物聯(lián)網(wǎng)水肥一體化系統(tǒng)方案

TBJ-150 一體化聲光報警器環(huán)境溫度采用什么模式

一體化機(jī)芯技術(shù)解析:鏡頭、傳感器與電路板的完美融合

《嵌入式機(jī)電一體化系統(tǒng)設(shè)計與實現(xiàn)》讀后感

智慧園區(qū)一體化管理平臺功能

安消一體化平臺建設(shè)方案

一體化高頻高壓發(fā)生器輸出模式——每日了解電力知識

什么是機(jī)電一體化?它有哪些應(yīng)用?

電機(jī)電驅(qū)一體化設(shè)計的優(yōu)勢與應(yīng)用解析

什么是通感算一體化?通感算一體化的應(yīng)用場景

乘用車一體化電池的發(fā)展現(xiàn)狀和未來趨勢

鴻蒙原生應(yīng)用/元服務(wù)開發(fā)-新版本端云一體化模板體驗反饋

物聯(lián)網(wǎng)農(nóng)業(yè)一體化灌溉泵站

基于FPGA與的VHDL語言驅(qū)動時序發(fā)生器與數(shù)據(jù)緩存器的一體化設(shè)計

基于FPGA與的VHDL語言驅(qū)動時序發(fā)生器與數(shù)據(jù)緩存器的一體化設(shè)計

評論