引言

隨著集成電路(IC)技術進入深亞微米時代,片上系統SoC(System-on-a-Chip)以其顯著的優勢成為當代IC設計的熱點。基于軟硬件協同設計及IP復用技術的片上系統具有功能強大、高集成度和低功耗等優點,可顯著降低系統體積和成本,縮短產品上市的時間。IP核是SoC設計的一個重要組成部分,已成為目前微電子設計的熱點和主要方向。

UART 核以其可靠性、傳送距離遠的特點被廣泛應該到通信系統和嵌入式微處理器上。利用傳統的EDA工具通過對RTL代碼仿真、驗證、綜合、布局布線后生成網表,下載到FPGA中實現,這樣做成的核主要用于驗證的,不適合用來做掩膜。在ASIC/SoC技術日漸成熟的今天,設計商更希望得到能夠做掩膜的IP核,從而便于嵌入到ASIC/SoC設計中。本文描述的UART核采用SYNOPSYS軟件的設計流程,在RTL級上進行優化,解決了綜合優化中碰到的一些常見問題。利用VCS 仿真、編寫測試激勵來驗證,最后用design compile 綜合優化做成的IP核可以滿足此要求,應用到ASIC/SoC設計中將產生巨大的效益。

為滿足未來移動通信標準的需要,在算法鏈路上Gbps系統采用時分雙工(TDD)、多天線(MIMO)、空時編碼、正交頻分復用(OFDM)、高階調制和LDPC編碼等高性能物理層傳輸技術,以實現Gbps系統所需的高數據速率業務傳輸和高頻譜效率。以頻分、時分為主的多址方式實現,能夠在多天線環境下對無線資源進行靈活調配,在兼顧實時話音傳輸的同時,最大程度上滿足分組數據傳輸的需要。

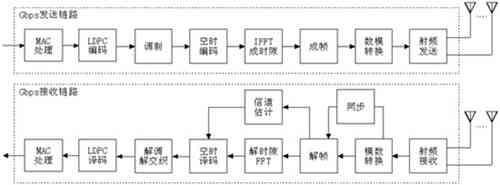

具體而言,Gbps系統使用3.4GHz頻段,實際帶寬100MHz,移動臺采用2發4收的天線,基站采用4發8收的天線,OFDM子載波數為2048子載波,有效為1664子載波。圖1是Gbps無線傳輸系統的算法鏈路示意圖。

圖1Gbps無線傳輸系統算法鏈路

Gbps基站系統的設計實現考慮

移動通信基站往往在一個站址上同時有GSM、TD-SCDMA等多種標準的基站,越來越多地呈現多標準共存的局面,基站研發應當著眼于降低建設、運營維護和升級成本。對此,Gbps無線通信基站應當采用可重配置方式,在支持Gbps無線傳輸的同時能夠兼容未來的LTE-A、IMT-Advanced標準,實現平滑演進。

從實現技術上看,實現信號處理算法并支持可重配置需要可編程的處理器件,現代基站系統廣泛采用的可編程處理器以DSP和FPGA為主。盡管高端多核DSP的工作時鐘頻率已經提升到1.2GHz,在TD-SCDMA基站中得到廣泛應用,但還是無法滿足Gbps系統中同步、MIMO、LDPC等算法對信號處理復雜度和實時性的要求。因此,Gbps項目需要采用大容量的高性能FPGA來作為復雜算法的承載平臺。

從基站系統的互連與數據傳輸機制上看,互連連接所有的無線接口、網絡接口和計算資源,傳輸代表計算任務的數據,是使基站系統成為整體、協調運行的關鍵要素。由于MIMO算法需要多天線輸入數據到多基帶處理芯片的傳輸,應當采用以交換式互連網絡和分組數據傳輸機制,更好滿足未來基站系統中MIMO、并行處理、動態可重配置、計算資源動態調度等的需要。

綜合以上設計實現考慮,經過綜合調研考察,Gbps項目決定采用Xilinx公司Virtex-5系列FPGA構架硬件系統平臺[4],承載復雜的信號處理算法,采用串行RapidIO[5]技術作為板間高性能互連,采用千兆以太網(GE)連接業務服務器及LMT計算機。

Virtex-5FPGA介紹

Virtex-5系列FPGA是Xilinx率先發布和量產的65nm平臺FPGA,目前包括LX、LXT、SXT、FXT及TXT等面向不同應用的多個子系列。

Virtex-5系列FPGA最高工作時鐘可以達到550MHz,總邏輯單元數多達330,000個。提供了高達11.6Mbit的靈活嵌入式BlockRAM,能有效地存儲和緩沖各種運算數據。多達640個

增強型嵌入式DSP48Eslice塊,可以滿足高性能DSP算法加速的需要,實現352GMACs的性能。Virtex-5FXT系列FPGA提供多達兩個標準的PowerPC 440處理器模塊,每個處理器在550 MHz時鐘頻率下可提供1,100 DMIPS 的性能。利用PowerPC 440嵌入式處理器模塊,可快速方便地實現Gbps基站中復雜的控制和通信協議處理。

Virtex-5系列FPGA集成100Mbps–6.5Gbps的高性能收發器,配合FPGA內部編程實現的串行RapidIO邏輯層模塊可以實現芯片間和板間高性能的數據交換互連。集成符合IEEE802.3標準的10/100/1000Mbps以太網MAC硬核,連接外部GEPHY或直接使用FPGA本身的GTP/GTX,就可以實現高性能的千兆以太網接口。

算法對資源的需求及FPGA型號的確定

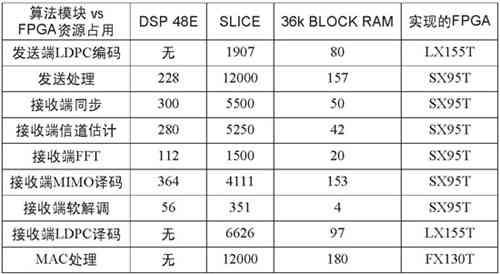

分析Gbps算法鏈路中各算法的不同實現特點并對運算量以及使用的主要資源進行估計,可以確定所需要使用的FPGA。表1是資源需求估計與FPGA選擇的結果,表2是目標FPGA內部資源情況的總結。

表1Gbps無線通信基站系統算法鏈路對FPGA資源的需求

其中,發送端的LDPC編碼和接收端的LDPC譯碼,主要是邏輯運算,無需乘法器資源,因此采用Virtex-5中的LXT實現。同步、FFT/IFFT、調制/解調、空時譯碼等算法需要消耗大量的乘法器資源,采用集成大量DSP48E模塊的SXT系列實現。MAC處理及網絡接口采用FXT系列FPGA中的2個PowerPC440處理器以及內嵌的千兆以太網硬核實現。采用FPGA片內的PowerPC處理器,可以大大地降低外部電路設計的復雜度,降低物理層與MAC層間數據交換的復雜性,降低系統傳輸延遲,而且可以利用PowerPC處理器應用處理加速單元(APU)實現定制的指令,極大地提高MAC處理的效率。

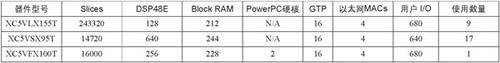

表2基站中使用的Virtex-5FPGA資源及數量統計

基于Virtex-5FPGA設計的Gbps無線通信基站

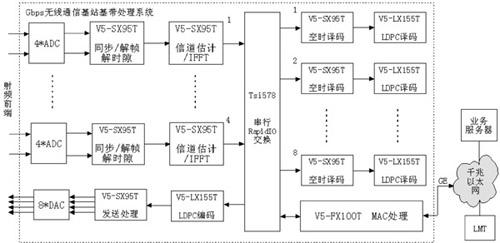

圖2Gbps無線通信基站基帶處理系統硬件實現框圖

根據算法需求分析的結果,Gbps基站系統最終以9片LX155T、17片SX95T、1片FX100TFPGA為中心構建。其中用4片SX95T實現8天線的接收同步/解幀/解時隙,每片FPGA處理2天線;用4片SX95T完成全部8天線的OFDM接收的IFFT及信道估計;用8片SX95T完成4發8收的MIMO空時譯碼處理,用8片LX155T完成解調、解交織及LDPC譯碼;FX100T中的PowerPC440處理器完成MAC層收發數據處理;1片LX155T完成發送的LDPC編碼。所有FPGA均采用FF1136封裝,由于Virtex-5FPGA采用管腳兼容設計,SXT、LXT和FXT可以直接替換,降低了PCB設計的工作量,增加了系統應用的靈活性。

ADC使用TI公司的11bit的ADS62P15,DAC使用ADI公司AD9779A,ADC、DAC采樣時鐘及FPGA工作時鐘頻率為122.88MHz。

Gbps基站系統的互連設計如下:ADC與同步FPGA間采用差分LVDS連接;各組同步/解幀/解時隙與信道估計/IFFT的FPGA以及空時譯碼與LDPC譯碼FPGA之間直接采用48對差分LVDS連接;其余FPGA互連采用14端口SerialRapdIO交換機實現。Gbps基站系統的結構和接口整體采用高級電信計算架構(ATCA)和SerialRapidIO構建,模塊化的結構和基于交換的互連使得系統可以方便地增加基帶處理板卡的數量或擴展新的功能模塊。

結論

本文利用SYNOPSYS軟件設計IP核,更適合用于ASIC/SoC設計,而采用傳統的EDA軟件實現的則適合用在FPGA上,不適合用來做掩膜生成ASIC/SoC。本UART核的邏輯設計采用VerilogHDL語言,用狀態機和移位寄存器設計使整個設計的時序清晰,同時減少了接收模塊停止位的判斷,通過對RTL級優化避免了毛刺、亞穩態、多時鐘等問題,仿真和驗證采用的是SYNOPSYS軟件的VCS,通過對時序、功耗、面積的綜合考慮,最后通過SYNOPSYS軟件的design compile 綜合優化完成的IP 核可成功應用到ASIC/SoC 設計上。

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601923 -

soc

+關注

關注

38文章

4122瀏覽量

217952 -

無線通信

+關注

關注

58文章

4521瀏覽量

143421

發布評論請先 登錄

相關推薦

如何利用Virtex-5 FPGA設計Gbps無線通信基站?

如何采用Virtex-5 FPGA設計Gbps無線通信基站?

如何利用Virtex-5 FPGA設計Gbps無線通信技術基站?

Xilinx Virtex-5 FXT FPGA開發方案

Virtex-5FPGA設計Gbps無線通信技術設計計算

基于Virtex-5 FPGA的Gbps無線通信基站設計

基于Virtex-5的串行傳輸系統的實現

基于Virtex-5的3.125G串行傳輸系統的設計

WWP248 - 移植到Virtex-5 FPGA的指南

WP245 - 使用Virtex-5系列FPGA獲得更高系統性能

Virtex-5系列FPGA CLB芯片的數據手冊免費下載

采用VerilogHDL語言和Virtex-5系列FPGA實現Gbps無線通信基站的設計

采用VerilogHDL語言和Virtex-5系列FPGA實現Gbps無線通信基站的設計

評論