1、引言

目標(biāo)識(shí)別作為現(xiàn)代雷達(dá)的重要發(fā)展方向之一,成為未來(lái)武器系統(tǒng)中的一個(gè)重要組成部分和當(dāng)前國(guó)內(nèi)外關(guān)注的熱點(diǎn),具有廣泛的民用和軍事應(yīng)用價(jià)值。根據(jù)雷達(dá)的探測(cè)手段及應(yīng)用背景的不同,出現(xiàn)了多種識(shí)別方法,其中雷達(dá)成像識(shí)別技術(shù)作為雷達(dá)目標(biāo)識(shí)別的一種新技術(shù)正在日趨成熟。而與二維成像雷達(dá)相比,易于實(shí)現(xiàn)的一維成像雷達(dá)(高距離分辨率雷達(dá))在目標(biāo)識(shí)別方面有著廣闊的前景。

文獻(xiàn)[1]對(duì)基于一維距離像的子空間方法進(jìn)行了廣泛而深入的研究,在普通特征子空間的基礎(chǔ)上,提出了正則子空間法、修正特征子空間法、綜合子空間法、子空間串法等多種子空間法,在對(duì)仿真與實(shí)測(cè)數(shù)據(jù)的識(shí)別中均取得較好的效果。其中部分算法的FPGA實(shí)現(xiàn)研究正是本文研究的主要任務(wù)。

CORDIC算法(The Coordinate Rotation Digital Com-puter)是Voider等人于1959年在美國(guó)航空控制系統(tǒng)的設(shè)計(jì)中提出來(lái)的,他是一種用于計(jì)算一些常用的基本運(yùn)算函數(shù)和算術(shù)操作的循環(huán)迭代算法,其基本思想是用一系列與運(yùn)算基數(shù)相關(guān)的角度的不斷偏擺從而逼近所需旋轉(zhuǎn)的角度。本質(zhì)上講他是一個(gè)數(shù)值性計(jì)算逼近的方法,由于這些固定的角度與計(jì)算基數(shù)有關(guān),運(yùn)算只有移位和加減。可用該算法來(lái)計(jì)算的函數(shù)包括乘、除、平方根、正弦、余弦、反正切、向量旋轉(zhuǎn)(既復(fù)數(shù)乘法)以及指數(shù)運(yùn)算等。1971年,J.S.Walther提出了統(tǒng)一的CORDIC算法形式,把圓周旋轉(zhuǎn)、雙曲旋轉(zhuǎn)和直線旋轉(zhuǎn)統(tǒng)一到同一個(gè)CORDIC迭代方程里。為同一硬件實(shí)現(xiàn)多功能提供了前提,隨著VLSI技術(shù)的發(fā)展,CORDIC算法越來(lái)越受到研究與應(yīng)用人員的重視,Xilinx公司于2002年發(fā)布了其CORDIC的IP核,由于IP核技術(shù)的可重用特性,可以使CORDIC算法獲得更廣泛的應(yīng)用。

2、CORDIC原理

CORDIC算法的原始思想一經(jīng)提出,就受到了人們的普遍關(guān)注,隨著FPGA技術(shù)的發(fā)展,CORDIC獲得了愈來(lái)愈廣泛的應(yīng)用,CORDIC算法可以分解為一些簡(jiǎn)單的且在硬件中容易實(shí)現(xiàn)的基本算法,如加法、移位等,使得這些算法在硬件上可以得到較好的實(shí)現(xiàn)。又因?yàn)樵撍惴ㄊ且环N規(guī)則化的算法,他滿(mǎn)足了硬件對(duì)算法的模塊化、規(guī)則化的要求,因此CORDIC算法可以充分發(fā)揮硬件的優(yōu)勢(shì),利用硬件的資源從而實(shí)現(xiàn)硬件與資源相結(jié)合的一種優(yōu)化方案,下面簡(jiǎn)要介紹其基本原理。

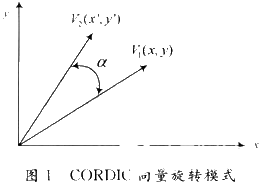

若將向量[z,y]T沿逆時(shí)針?lè)较蛐D(zhuǎn)角度a如圖1所示,初始向量V1經(jīng)旋轉(zhuǎn)a角以后得到向量V2。

![]()

也即:

![]()

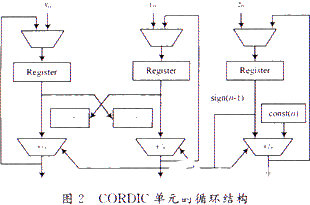

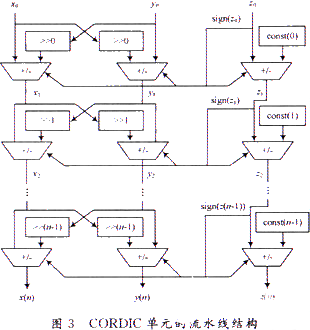

在應(yīng)用過(guò)程中,CORDIC的實(shí)現(xiàn)方式我們主要討論循環(huán)結(jié)構(gòu)(圖2)以及流水線結(jié)構(gòu)(圖3)。圖2采用的是并行的數(shù)據(jù)格式,由于其大的扇人量,不適合在單個(gè)邏輯單元扇入量有限的FPGA上實(shí)現(xiàn)。如果在FPGA上實(shí)現(xiàn)將會(huì)占用大量的邏輯塊,浪費(fèi)資源,而且路徑的拉長(zhǎng)會(huì)導(dǎo)致其速度的降低。在圖3所示的流水線結(jié)構(gòu)中,每一個(gè)移位器都是固定的深度,而且旋轉(zhuǎn)角度集的各個(gè)值作為常數(shù)值直接連到角累加器件上面,不需要存取空間和讀取時(shí)間。在FPGA器件中每個(gè)細(xì)胞元都有寄存器,便于采用流水線技術(shù)。

3、實(shí)現(xiàn)技術(shù)中的IP核的應(yīng)用

在實(shí)際的設(shè)計(jì)中,我們采用了Xilinx系列芯片中的IP核來(lái)完成設(shè)計(jì),這樣做的目的主要是為了充分利用芯片的內(nèi)部資源,實(shí)現(xiàn)內(nèi)部結(jié)構(gòu)的優(yōu)化設(shè)計(jì),IP核生成工具可以是各種類(lèi)型、功能的模塊。這些IP核是根據(jù)Xilinx的FP-GA器件特點(diǎn)和結(jié)構(gòu)而設(shè)計(jì),直接用Xilinx FPGA底層硬件原語(yǔ)進(jìn)行描述,可充分將FPGA的性能發(fā)揮出來(lái),其實(shí)現(xiàn)結(jié)果在面積和速度上都能達(dá)到令人滿(mǎn)意的效果。

4、數(shù)值精度問(wèn)題

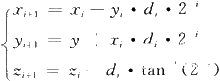

在應(yīng)用每一個(gè)數(shù)值實(shí)現(xiàn)方法時(shí),他的數(shù)值精度是我們不得不考慮的問(wèn)題,CORDIC算法也不例外。WaltherHu、Kota都對(duì)他進(jìn)行了深入的研究,分別對(duì)其定點(diǎn)和浮點(diǎn)實(shí)現(xiàn)方式的數(shù)值精度給出了定量描述或在數(shù)學(xué)上進(jìn)行了分析,不同的算法模式不同的操作模式有著不同的結(jié)果。CORDIC的誤差主要來(lái)自?xún)煞矫妫阂环矫妫谟眯D(zhuǎn)角度集來(lái)表示角度時(shí),有限子集產(chǎn)生了截?cái)嗾`差;另一方面由于有限字長(zhǎng)的限制,在數(shù)據(jù)表示和移位運(yùn)算中產(chǎn)生了舍人誤差。由于CORDIC的3個(gè)方程之間相互作用,這為分析CORDIC的誤差帶來(lái)了很大的難度。以旋轉(zhuǎn)模式的誤差分析為例,我們以x,y,z表示有限精度下的計(jì)算值,xi,yi,zi表示無(wú)誤差的精確值,z,y,z表示數(shù)學(xué)意義上得到的值,旋轉(zhuǎn)模式時(shí)的迭代方程為:

其中:

![]()

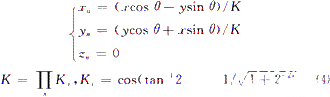

經(jīng)n次迭代后得到:

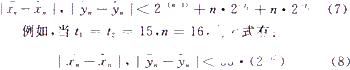

對(duì)于x,y分量來(lái)說(shuō),若假定z分量對(duì)他們的作用因子di是精確的,則他們主要是受舍入誤差的影響,設(shè)x,y由t1位表示,且均為小數(shù)位,則有限精度下的x,y分量經(jīng)過(guò)n次迭代后將產(chǎn)生大約log2n位的舍入誤差。對(duì)于z分量來(lái)說(shuō),其誤差主要來(lái)自?xún)煞矫妫阂环矫媸墙財(cái)嗾`差,設(shè)為ezl,由CORDIC收斂性可知:

![]()

另一方面是舍人誤差ez2,若假定用t2來(lái)表示z分量則│ez2│《2-t2,假定θ為精確值,a為計(jì)算值,則:

![]()

綜上有:

從上面結(jié)果中,我們發(fā)現(xiàn)只要在算法內(nèi)部數(shù)據(jù)中增加log332Δ5位長(zhǎng)度的保護(hù)位,則可以校正誤差,在輸出結(jié)果中獲得15位的精度。

5、 仿真實(shí)驗(yàn)

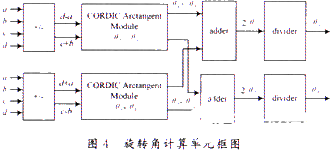

在實(shí)現(xiàn)了各種處理單元以后,我們可以很方便地將其應(yīng)用于陣列中來(lái)計(jì)算矩陣的奇異值分解。一個(gè)2×2矩陣的SVD實(shí)際上就是一個(gè)旋轉(zhuǎn)角計(jì)算單元與雙邊旋轉(zhuǎn)計(jì)算單元的組合,結(jié)構(gòu)框圖如圖4所示。

旋轉(zhuǎn)角計(jì)算主要按照直接2-角方法,分別計(jì)算出θr+θt和θr-θt,通過(guò)加法器和減法器以及除法器,得到θr和θt。一個(gè)2×2矩陣的雙邊旋轉(zhuǎn)為:

![]()

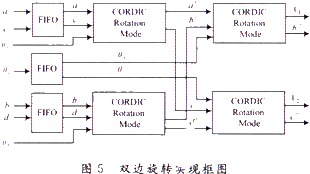

在設(shè)計(jì)中,我們注意到角θr要等到θt,旋轉(zhuǎn)完成后才輸入到旋轉(zhuǎn)器中,我們通過(guò)添加FIFO做為延時(shí)控制單元,通過(guò)控制FIFO的深度來(lái)完成數(shù)據(jù)的同步,獲得同時(shí)鐘頻率一樣高的數(shù)據(jù)流量。雙邊旋轉(zhuǎn)實(shí)現(xiàn)框圖如圖5所示。

使用VHDL語(yǔ)言進(jìn)行模塊功能描述,在Xilinx仿真平臺(tái)ISE 7.1以及Modelsim SE 5.7d環(huán)境下的仿真結(jié)果如圖6所示,系統(tǒng)工作的時(shí)鐘頻率為50 MHz,在選用高端的Virtcx4系列芯片進(jìn)行算法的時(shí)序仿真時(shí),資源的占用都是比較少的。這為下一步的高階子空間算法的實(shí)現(xiàn)奠定了比較好的基礎(chǔ)。

6 、結(jié) 語(yǔ)

本文在基于Xilinx的軟硬件開(kāi)發(fā)平臺(tái)上,對(duì)用FPGA實(shí)現(xiàn)用于雷達(dá)一維像目標(biāo)識(shí)別的特征子空間方法進(jìn)行了一系列的探討與研究,深入研究了CORDIC理論在數(shù)值精度、操作模式上的各種應(yīng)用,并且用于FPGA設(shè)計(jì)實(shí)現(xiàn)二維子空間的研究并且成功地進(jìn)行了硬件仿真實(shí)現(xiàn),下面的工作是結(jié)合并行雅可比方法采用Systolic陣列結(jié)構(gòu)進(jìn)行高階子空間分解的FPGA實(shí)現(xiàn),這部分工作將在后面的研究中完成。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1626文章

21671瀏覽量

601902 -

Xilinx

+關(guān)注

關(guān)注

71文章

2164瀏覽量

121015 -

雷達(dá)

+關(guān)注

關(guān)注

50文章

2903瀏覽量

117335

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

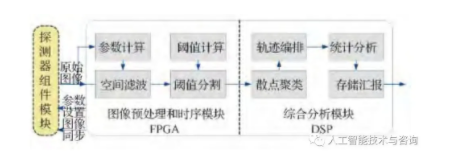

基于DSP和FPGA組合的嵌入式圖像處理平臺(tái)的實(shí)時(shí)多目標(biāo)識(shí)別算法

開(kāi)發(fā)者手機(jī) AI - 目標(biāo)識(shí)別 demo

RCS目標(biāo)識(shí)別

【PYNQ-Z2申請(qǐng)】圖像目標(biāo)識(shí)別FPGA硬件加速

感知起源招聘FPGA工程師(坐標(biāo)北京)

一種適用于空間觀測(cè)任務(wù)的實(shí)時(shí)多目標(biāo)識(shí)別算法分享

基于DSP的毫米波主被動(dòng)復(fù)合探測(cè)器目標(biāo)識(shí)別系統(tǒng)設(shè)計(jì)【回映分享】

改進(jìn)最優(yōu)聚類(lèi)中心雷達(dá)目標(biāo)識(shí)別法

基于USB和目標(biāo)識(shí)別的圖像采集系統(tǒng)的設(shè)計(jì)實(shí)現(xiàn)

紅外目標(biāo)識(shí)別跟蹤系統(tǒng)的DSP+FPGA實(shí)現(xiàn)

Xilinx與IBM通過(guò)SuperVesselOpenPOWER開(kāi)發(fā)云平臺(tái)實(shí)現(xiàn) FPGA加速

紅外動(dòng)目標(biāo)識(shí)別跟蹤系統(tǒng)的實(shí)現(xiàn)方案

Arbe將開(kāi)發(fā)基于成像雷達(dá)開(kāi)發(fā)平臺(tái)的新一代雷達(dá)系統(tǒng)

基于三維激光點(diǎn)云的目標(biāo)識(shí)別與跟蹤研究

基于三維激光點(diǎn)云的目標(biāo)識(shí)別與跟蹤研究

基于Xilinx開(kāi)發(fā)平臺(tái)和FPGA器件實(shí)現(xiàn)一維成像雷達(dá)目標(biāo)識(shí)別

基于Xilinx開(kāi)發(fā)平臺(tái)和FPGA器件實(shí)現(xiàn)一維成像雷達(dá)目標(biāo)識(shí)別

評(píng)論