嵌入式系統設計中,軟件和硬件的接口問題經常困擾軟件開發工程師。正確理解接口在處理器與高級語言開發環境方面的約束條件,可以加速整個系統設計,并為改進系統的質量、性能和可靠性以及縮短開發周期和減少成本提供保證,本文從兩個設計實例的比較入手,介紹了嵌入式系統的設計原則以及關于寄存器及其域的種種考慮。

嵌入式系統設計通常分為兩個部分:硬件設計和軟件開發。這兩部分任務通常由不同的設計小組負責,相互間很少有覆蓋的地方。由于軟件小組很少涉足前面的硬件設計,采用這種方式進行開發經常會遇到問題,特別是硬件與軟件開發環境之間的接口性能較差時,會導致系統開發時間延長、開發成本提高,最終推遲產品的上市。

最理想的解決方案是軟件小組參與硬件設計,但是在時間安排、資金和人員方面往往又是不實際的。一種變通的方法是創建一套硬件接口規范來加速軟件開發流程。從軟件開發者的角度來理解最優化的硬件接口設計能有效地防止軟件開發中出現不必要的硬件問題,這種方法對硬件設計流程造成的影響也很小。

嵌入式系統的核心部件是各種類型的嵌入式處理器,目前據不完全統計,全世界嵌入式處理器的品種總量已經超過1000多種,流行體系結構有30幾個系列。但與全球PC市場不同的是沒有一種微處理器和微處理器公司可以主導嵌入式系統,僅以32位的CPU而言,就有100種以上嵌入式微處理器。由于嵌入式系統設計的差異性極大,因此選擇是多樣化的。設計者在選擇處理器時要考慮的主要因素有:(1) 調查上市的CPU供應商。(2) 處理器的處理速度。(3) 技術指標。(4) 處理器的低工耗。(5) 處理器的軟件支持工具。(6) 處理器是否內置調試工具。(7) 處理器供應商是否提供評估板。

盡管嵌入式系統有著無比廣闊的市場需求和發展前景,但嵌入式系統的發展多年來卻經歷了一個曲折和痛苦的歷程。隨著微處理器的產生,價格低廉、結構小巧的CPU和外設連接提供了穩定可靠的硬件架構,那么限制嵌入式系統發展的瓶頸就突出表現在了軟件方面。從八十年代末開始,陸續出現了一些嵌入式操作系統,比較著名的有Tornado/VxWorkx、pSOSystem、Neculeus和Windowss CE、QNX、VRTX,以及沸沸揚揚的“女媧計劃”,中國人自己的嵌入式操作系統HOPEN和現在談論最多的嵌入式Linux操作系統等等。可用于嵌入式系統軟件開發的操作系統很多,但關鍵是如何選擇一個適合你所開發項目的操作系統,我們認為應該從以下幾點進行考慮:(1) 操作系統提供那些開發工具。(2) 操作系統向硬件接口移植的難度。(3) 操作系統的內存要求。(4)開發人員是否熟悉此操作系統及其提供的API。(5)操作系統是否有提供硬件的驅動程序,如網卡等。(6)操作系統是否具有可剪裁性,即能否根據實際需要進行系統功能的剪裁。(7) 操作系統的實時性。實時性分為:軟實時和硬實時。有些嵌入式操作系統只能提供軟實時,如WindowsCE。

嵌入式系統結構的一般模型

從系統角度看,嵌入式系統是多種系統要素之間的很多接口的集合,這里羅列的主要資源是系統處理器。處理器接口可以分成兩大類,分別標識為本地總線和硬件總線。值得注意的是,本文中的總線是根據處理器利用資源時的訪問類型單獨定義的,與具體的硬件連接沒有對應關系。

本地總線是資源與處理器之間的接口總線,它允許無限制的連續訪問。無限制訪問意味著處理器能夠利用其內部數據類型訪問一個資源的所有要素;連續訪問是指所有資源要素占用的資源地址空間是連續的,中間沒有任何間隔。RAM和EPROM就是與本地總線接口的常見范例。

系統定義的實例

這里考慮兩種不同的硬件實現方式。該系統是處理器控制的三軸伺服系統,本部分的系統設計僅限于位置反饋控制的設計,因此有助于我們專注于硬件接口的實現。

該系統的兩種實現方式都實現了處理器與用戶ASIC的接口,從而為三軸伺服提供驅動與反饋信息。每個系統中的ASIC必須利用32位數據總線使處理器與三套驅動/反饋資源連接。每種資源包含有一個帶符號的10位驅動寄存器、一個帶符號的8位位置寄存器和一個3位的錯誤狀態寄存器,任何一個位置位都表示一種錯誤狀態,由它產生軸驅動的關閉信息。

圖1和圖2表示了一種寄存器接口的可能實現方式,分別標識為系統實現A和系統實現B。為了描述方便,后文以系統A和系統B分別指代這兩種實現。

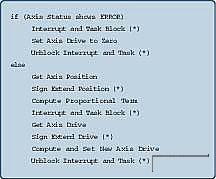

表1所示的偽隨機碼為軸驅動程序,可用于A、B兩個系統。偽隨機碼設計用于基于先進處理器的系統實現,并運行于實時操作系統,以通用軸控制程序的三份獨立挎貝(或任務實例)實現軸的控制。當使用系統A中定義的接口時只需偽隨機碼中那些帶星號的代碼行。

即使在代碼原型階段系統B所需的代碼也比系統A少很多。系統B中的硬件設計要稍微復雜一些,但能減輕軟件開發的負擔。后文將回顧這兩個實例系統和偽隨機碼。

為了滿足項目要求,對整個系統結構進行優化時需要在硬件與軟件實現之間作出折衷,現實中是沒有項目能滿足這里提到的所有理想軟件接口要求的。對理想狀態的認識有助于硬件設計工程師識別并消除影響軟件設計的一些障礙。

設計原則

1. 采用標準總線訪問

有效的嵌入式硬件接口設計的一般原則是:對軟件設計工程師來說,硬件設計應確保對硬件資源的訪問盡可能透明。處理器使用所有標準的讀寫指令可以實現透明訪問,而不用考慮前面的訪問內容或時序。

通常不可避免要采用一些特殊總線,但需要慎重考慮特殊訪問空間的使用選擇,因為這種情況會給系統軟件設計帶來一定的困難。系統A采用了只寫寄存器,因此要求系統軟件提供“影子”內存(Shadow memory)來保存寫入到資源的數據。而系統B由于允許所有的寄存器都可讀寫,因此沒有這種限制。

2. 開發基于處理器的資源接口

硬件設計工程師習慣于從下至上分析資源接口問題以及與系統總線的連接,而通過分析處理器在系統中對資源的訪問過程則更好。

“處理器與資源”間的接口常常是最重要的接口,在硬件設計流程中它的效率應是最優先考慮的對象。統一規劃整個系統的資源訪問對于正確理解由硬件設計選擇所引起的訪問限制很重要。

3. 系統內存映射的創建與維護

對于一個好的系統設計來說,所有資源的存儲器映射都非常重要。如前所述,存儲器映射的設計應考慮到具體處理器要求,而不是簡單地說明一個資源所解碼的地址線類型。如果采用的是寄存器可配置資源,如PCI總線,硬件設計工程師應在存儲器映射中配置所有與該資源有關的配置寄存器,并提供用以創建硬件驗證所需的靜態映射的配置寄存器初始化值。

隨著系統的不斷成熟,存儲器映射也必須不斷完善,并隨著軟硬件開發的進展不斷改進。

4. 統一的訪問模式

當前的嵌入式系統由于復雜度的提高,通常由多人共同合作進行設計。每個硬件部件的設計必須與整體一致,這樣才能開發出統一的資源訪問模式。如果不同功能模塊的訪問不一致的話,在軟件開發期間就會產生潛在的訪問限制錯誤,從而可能需要為每個子系統設計專門的軟件驅動程序。對不同邏輯塊的不一致訪問也會使硬件集成和驗證變得困難重重。

如設計工程師在調試器上編輯4個十六進制數字并不能保證處理器會使用一個16位的讀/寫周期,評估仿真器處理多個限制性訪問地址空間的能力就非常有用,特別是在用“限制外”訪問方式觸發總線故障的處理器結構中。

寄存器設計

既然硬件設計工程師的重點已經從邏輯門和總線轉移到了系統設計,我們再來審視一下任何處理器系統中最常用到的寄存器設計。寄存器接口允許高速訪問資源,其訪問的效率對系統的性能有很大的影響。

寄存器的結構與訪問

設計工程師應該精心選擇硬件寄存器大小,使處理器能最有效地進行硬件訪問。一般來說,總是采用系統內部整數訪問方式。任何可寫的寄存器也應該是以同樣的格式可讀,這樣可以避免使用本地存儲器來緩存這些寄存器值。

控制一個子系統的寄存器應該以相同的結構形式在一起分組,使軟件能使用通用的驅動程序對它們進行訪問。當設計中需要多個同一類型的子系統時這點尤其重要。

寄存器復位內容

系統A不控制驅動寄存器的復位內容,需要代碼的介入來將所有三個軸的驅動寄存器設置為零。這種結構會產生嚴重的系統設計問題,因為處理器通常是保持在復位狀態,直到FPGA和ASIC加電并得到配置后處理器才正常工作。如果開發人員使用仿真器,那么在集成過程中系統A還會出現另外的問題:被仿真器控制的處理器在系統加電后可能需要很長的初始化時間才能正常工作。

系統B在加電后會將所有軸驅動寄存器設為零,它對軸驅動設置的控制并不依賴于啟動時間。因為系統B沒有隱藏的狀態機,因此在本設計中沒有必要考慮增加額外的軟件復位寄存器。

寄存器域設計

大多數資源接口所包含的數據項并不正好適合一個寄存器。這種情況下,硬件設計工程師必須將一個寄存器分成若干域。合理的域結構對系統性能來說非常重要,與寄存器接口設計有相似的影響。有效的域接口設計規則類似于寄存器設計規則,但設計工程師還需要特別注意域的順序與放置,還要對寄存器中未用到一些字節作一定的處理。

1. 寄存器的域

域被定義為寄存器中若干位的子集,主要用于報告或控制資源的一個功能要素。在硬件設計中最常用的域類型有:1. 布爾域:真或假,通常是一位;2. 多位狀態域和控制域:多位用于報告或控制內部相關功能;3. 列舉狀態域和控制域:多個位的集合,其中每個位代表了一種不同的硬件狀態;4. 數字域:多個位組合在一起用來代表一定的數量值。

從軟件使用者角度看,最有效的域結構是每個寄存器只用一個域。這種理想的軟件結構可能導致硬件實現效率低,因此一個好的系統設計需要在軟硬件設計之間作出折衷,在每個寄存器中應放置多個域。

2. 域結構

前文提到的用于寄存器的結構概念同樣也適合于寄存器內部的域。一個寄存器應該只包含屬于設計中同一功能要素的域,并且該寄存器中的所有可寫域都應該是可讀的。

由于系統A將屬于不相關功能的多個域組合放在一個寄存器中,因此它需要使用特殊的驅動程序。而系統B則遵循“單個寄存器內的域按任務進行組織”的原則,將每個域放置在屬于自己的專用寄存器中,因此能高效地訪問資源中的每個軸參數。

3. 十六進制數字對齊

硬件設計工程師還應該明白針對處理器和軟件開發環境進行對齊約束。如果將域放置在錯誤的地址上而超出字的邊界,將迫使軟件設計工程師只能按塊訪問每個域。在調試過程中,用零值填充域是非常有用的,可以使每個域的最低位對齊十六進制數字(4位)的邊界:當在邏輯分析儀、調試儀或仿真器上顯示寄存器情況時,十六進制數字對齊會有助于域值的可視化提取。由于控制域沒有對齊,在查錯時屏蔽測試輸入也十分困難。而系統B的所有域都是按十六進制偶數數字對齊,因此通過寄存器讀可以很容易地確定每個域的狀態,并且能方便地將某個域設為指定值。

4. 域位置的分配與順序

寄存器內域的設置也會嚴重影響軟件實現的效率。布爾域和多位域通常與位置無關,但當列舉域和數字域被放置在寄存器的最低位(LSB)時對它們的訪問效率通常是最高的(LSB的實際位數取決于處理器類型,位0不一定是LSB)。將域配置在寄存器的LSB中可以有效地消除對域內容屏蔽后的移位操作,也使測試設備或進行可視化檢查的調試儀訪問寄存器時能更容易地識別域值。

系統A中用于軸2和軸3的域值在使用前必須要求軟件進行屏蔽和移位。而系統B則將所有數字域配置在寄存器的LSB中,從而能完成更有效的訪問。系統B的集成性也更好,資源寄存器的十六進制數據能真正分離成正確的域值。

5. 未用數據位

寄存器中的未用位同樣也會影響軟件實現的效率。所有未用位應回歸為零,并且寫入操作時無需對它們作特殊的處理,這樣可以避免不必要的屏蔽與清除操作。在這種情況下,使硬件實現符號將域的MSB擴展到未用位就非常有用。以這種方式擴展的數字域能夠被處理器直接訪問,因為帶符號的數值無需軟件符號的擴展。當對特殊的數字域變量的訪問速度嚴重影響整體系統性能時,將該類型的域與“單個寄存器單個域”結合起來考慮將非常有用。由于無需屏蔽或符號擴展,這些域能以內部數據訪問的方式直接訪問。

當系統A中需要從寄存器提取域值時,要求軟件對每個數字域值進行符號擴展,而系統B允許通過對寄存器的內部整數訪問直接訪問域值。

6. 域類型選擇

域類型的正確選擇也能極大地提高軟件實現效率。在打開或關閉獨立資源功能時布爾域是最有效的。要注意的是,只有當寄存器是可讀寫時單位域才容易編碼。如果硬件寄存器對域的訪問有限制,就需要專門的緩沖器(有可能再加上一個專門的驅動程序)來保存當前的內容。限制性訪問同時也會限制一些編程構造的使用,如位域(bit field),從而影響系統代碼的可讀性,且無助于減少編程錯誤。

當表達資源狀態的數據需要占用一定范圍的值時數字域就很有用。當一個域能保持正值和負值使用時,帶符號的表達式通常需要更多的軟件工作。另外,還要避免在數字域中對其它數據進行編碼(如利用域符號表示一個不相關的資源狀態)。

系統A中對軸驅動域的“只寫”訪問使軟件對目標域的訪問效率很低,必須用RAM保存寫過程中不作修改的過去的軸內容。系統B中由于每個寄存器都只有一個域并允許讀寫操作,因此不存在這樣的問題。

實例系統的性能評估

為了評估最終系統軟件的性能,將列表1中的偽隨機碼正確轉換成C代碼并同時用于A、B系統中,然后利用內部存儲器中的結構模擬每個系統的硬件接口。代碼中應避免使用位域,因為標準C實現不能在限制性訪問的地址空間上正確工作。系統代碼模擬運行于PowerPC,編譯工具采用的是Green Hills MultiC,目標操作系統是VxWorks,編譯器設置在中級優化度(目的是幫助調試,并允許設計工程師把每條匯編指令與每一行C代碼聯系起來)。

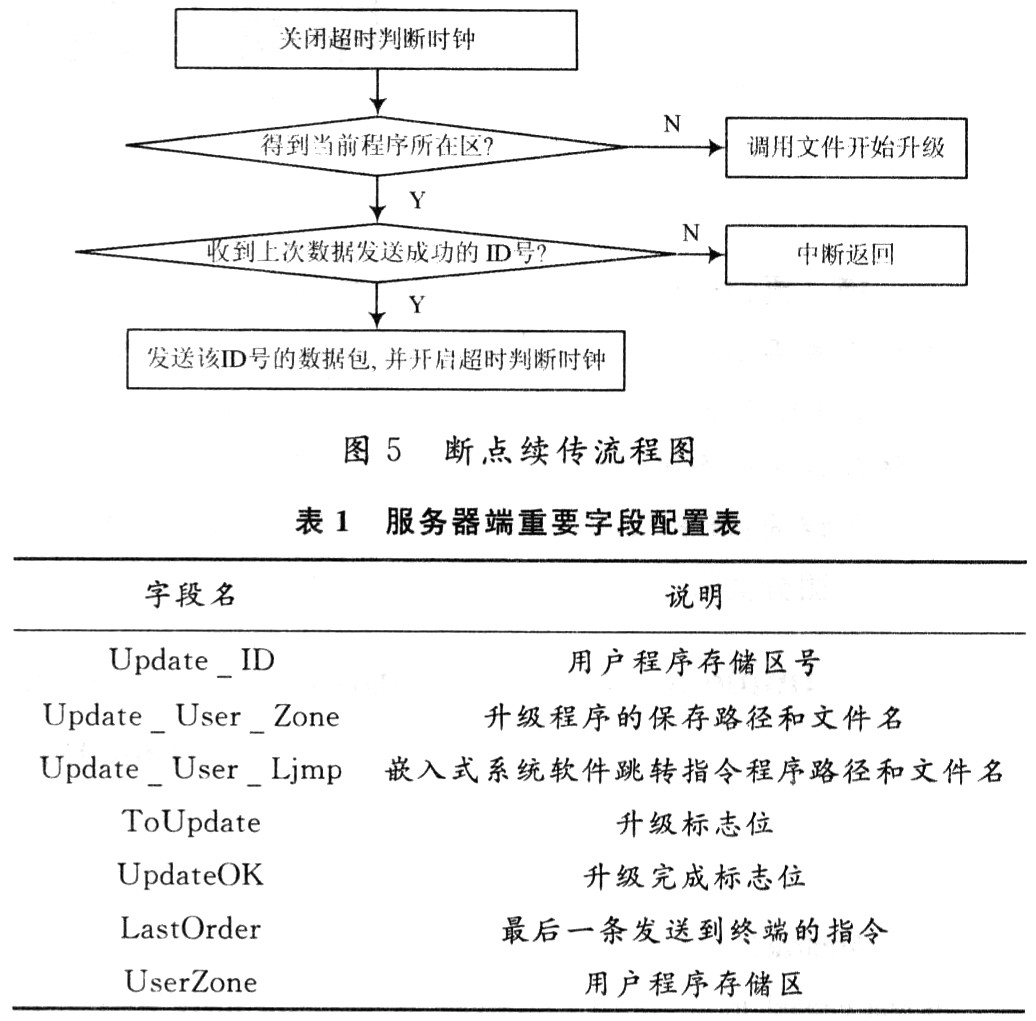

表1列出了偽隨機碼的每一行,并給出了每個系統實現所用到的匯編指令與功能調用數量。另外還對兩個實現所用的代碼執行速度進行測試。子程序升級系統B軸的速度要比系統A快5.3倍,這主要歸功于任務阻塞與去阻塞功能調用的去除。要注意的是實際系統中的加速效果可能并不明顯,因為實際的硬件訪問時間對總的執行時間影響最大。

在實驗中要提升兩個實現所用編譯器的優化度,結果發現優化度的提高對系統B無效,對系統A來說只是減少了很少的代碼,并且速度卻稍有降低。這樣的結果表明,系統B的硬件接口在軸域的資源訪問上非常接近內部訪問的效能。

仔細考察這兩個設計發現,系統B所用的額外資源中最主要的驅動源是組合型軸尋址方案。為了驗證這一結果,重新組織寄存器映射,以便將每個軸作為一個獨立資源使用,單個軸映射按地址位邊界對齊。這一變通的實現方式保留了系統B的所有軟件接口優點,同時減少了整體硬件器件的使用,Virtex系列器件的片利用率能降低2.3%,9500系列的利用率能降低22%。

硬件設計會極大地影響系統軟件實現的復雜性和質量。一個好的硬件設計要求設計人員能根據硬件實現與最終軟件設計環境的復雜性做出決定,正確理解硬件接口設計對軟件開發流程的影響能極大地改進系統質量、性能和可靠性,同時減少系統開發的周期與成本。

-

處理器

+關注

關注

68文章

18927瀏覽量

227252 -

嵌入式

+關注

關注

5046文章

18821瀏覽量

298627 -

操作系統

+關注

關注

37文章

6545瀏覽量

122753

發布評論請先 登錄

相關推薦

基于GPRS的嵌入式系統軟件的遠程在線升級

基于RTOS的嵌入式系統軟件的設計講解

應用于嵌入式系統軟件和硬件接口問題的設計

應用于嵌入式系統軟件和硬件接口問題的設計

評論