基于FPGA設計數字日歷可以實現以軟件方式設計硬件的目的,無需購買專用數字芯片,從而克服了傳統利用多片數字集成電路設計數字日歷存在焊接麻煩、調試繁瑣、成本較高等問題。而且,基于FPGA的數字日歷與傳統系統相比,在設計靈活、開發速度、降低成本、計時精度、功能實現上都得到大幅度提升,能夠更好地滿足人們日常生活的需要。

本文介紹如何利用VHDL硬件描述語言設計一個具有年、月、日、星期、時、分、秒計時顯示功能,時間調整功能和整點報時功能的數字日歷。在QuartusⅡ開發環境下,采用自頂向下的設計方法,建立各個基本模塊,再構建成一個完整的基于FPGA設計的數字日歷的頂層模塊,然后對其進行編譯、仿真、引腳鎖定,最終下載到可編程邏輯器件上進行結果驗證。

1數字日歷整體設計方案

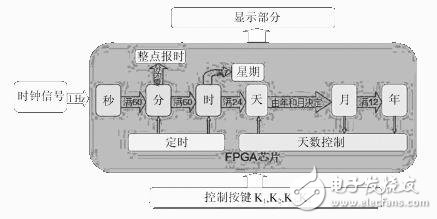

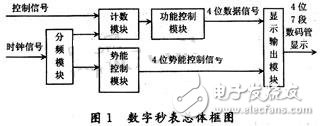

基于FPGA的數字日歷設計分為硬件設計和軟件設計兩大部分。其原理框圖如圖1所示。整個數字日歷由六個部分組成:顯示控制部分,時分秒部分,年月日部分,定時與整點報時部分,星期部分,調整控制部分。秒、分、時分別由兩個60進制的計數器和一個24進制的計數器組成。當個計數器達到進位的條件時向下一計數器進位。同樣日、月、年也是由不同的計數器組成,當達到所需進位的條件時向下一計數器進位,各計數器在進位的同時分別把各自的結果輸出給顯示部分進行實時顯示。

圖1數字日歷原理框圖

2數字日歷的工作原理

首先由外部振蕩器產生穩定的高頻脈沖信號,作為數字日歷的時間基準,然后經過分頻器輸出標準秒脈沖,輸入到FPGA的CLOCK端,實現計數。當秒計數器滿60后向分計數器進位,分計數器滿60后向小時計數器進位,小時計數器按照“24進1”規律計數。計滿后各計數器清零,重新計數。日部分由于日有28天、29天、30天、31天4種情況,故日由年和月共同判斷其天數,日計滿后向月進位,月滿后向年進位。計數器的輸出分別經譯碼器送數碼管顯示。計時出現誤差時,可以用校時電路校時、校分、校秒和校年、校月、校日。

設計中用到了6個按鍵K1,K2,K3,K4,ZHENG,NAO.其中K1用于切換顯示,剛開始時顯示日期,按兩次K1顯示星期+時間,再按兩次K1顯示定時時間,再按兩次重新顯示日期,以此循環。K2、K3和K4配合進行調節:開始正常顯示不進行調節;當按兩下K2鍵切換到對分鐘進行調節,此時每按兩下K3鍵分鐘加1;再按兩下K2鍵切換到對小時進行調節,此時每按兩下K3鍵小時加1;依照分鐘→小時→星期→天→月→年→定時→正常→分鐘的次序循環調節,每按兩下K2鍵切換到調節相應顯示,此時每按下K3鍵兩次,對應顯示加1;當切換到定時調節時,每按兩下K3鍵,定時的分鐘加1,此時按兩下K4鍵,切換到定時小時調節,每按兩下K3鍵,定時的小時加1.按鍵ZHENG和NAO為整點報時和定時鬧鐘的使能端(低電平有效)。

3軟件設計

軟件設計分為秒分時、年月日、按鍵調整、控制顯示、鬧鐘等幾大模塊。設計好各子模塊,然后在原理圖編輯窗口創建頂層原理圖文件shuzirili.bdf,將各子模塊按照邏輯關系連接起來得到數字日歷電路核心部分的原理圖。下面對各子模塊設計及仿真進行介紹。

3.1時分秒模塊

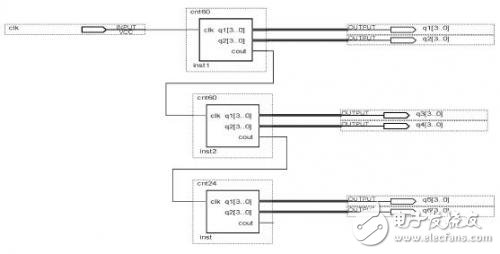

分和秒都是60進制的計數器,小時則是24進制的計數器,先對各個子模塊進行設計編譯,驗證無誤后再將其組織到一起。外部時鐘信號通過秒模塊的clk輸入,產生的進位信號輸送到分模塊的clk,分模塊產生的進位信號輸送到小時模塊的clk,構成時分秒模塊。其結構圖如圖2所示。

圖2時分秒原理圖

3.2星期模塊

星期模塊為七進制計數器。其計數時鐘信號來自于調時電路產生的星期進位脈沖信號,計數至6瞬間,計星期模塊返回0重新開始計數。

3.3年月日模塊

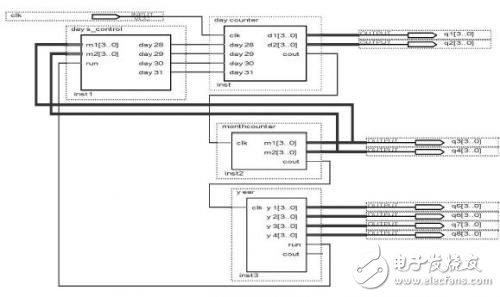

年月日模塊有daycounter模塊、days-control模塊、monthcounter模塊、yearcounter模塊組成,具有大小月判斷和閏年判斷功能,其結構圖如圖3所示。

圖3年月日連接框圖

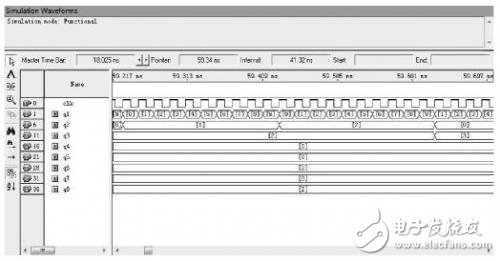

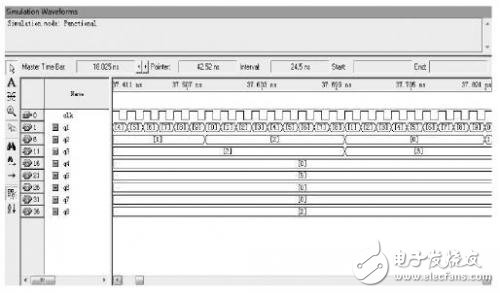

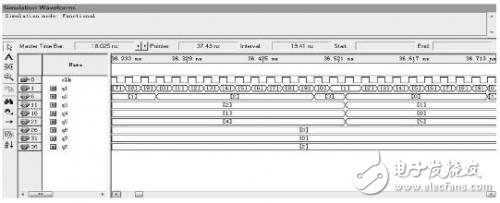

下面以年月日模塊為例,連接好之后進行編譯并仿真,閏/平年的2月仿真結果如圖4,圖5所示,年進位如圖6所示。

圖4仿真結果(2008年2月)

圖5仿真結果(2005年2月)

圖6仿真結果(2004年12月)

年月日模塊計數設定為2000年~2999年,從圖4中可以看出2008年2月,計數到29天;從圖5得到2005年2月計數到28天;從圖6看出2004年12月計數到31天,設計正確。

3.4定時模塊

定時模塊通過按鍵K4來切換調節定時的分鐘和小時,調整功能由調時模塊的按鍵K3來完成,每按兩下K3對應的顯示加1.

3.5調時模塊

調時模塊設計思想是:通過把整個設計中的上一個模塊(比如:分的上一個模塊是秒;年的上一個模塊是月,等等)的進位輸出接到本模塊的輸入in,out接到下一個模塊的時鐘輸入。正常狀態下sout=fin,fout=hin,hout=din,dout=min,mout=yin,win=hout;當每按下兩次K2鍵,產生一個上升沿分別對fin,hin,win,din,min,yin,dingshi調節,調節信號由K3給出。其中定義一個信號w,計數到7返0,對應正常狀態,fin,hin,win,din,min,yin,dingshi 7個狀態。

當K2每來一個上升沿時,分別對分,時,星期,天,月,年以及定時調整,調整信號由K3給出,經仿真調時模塊結果與系統設計要求符合。

3.6控制模塊

控制模塊通過K1按鍵進行切換顯示調整,起初顯示年月日,按下2次K1顯示時間,再按下2次顯示定時時間。

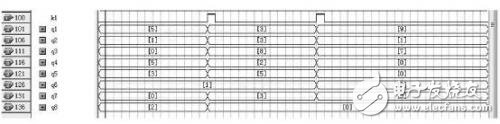

若仿真參數設置數值為:2013年05月15日,星期三,15:28(33 s),定時為07:19.仿真后結果如圖7所示。

從圖7可以看出,通過K1按鍵控制顯示,開始顯示年月日:20130515,當按下K1兩下,顯示星期+時間:03152833;再按兩下顯示定時時間:00000719.仿真結果與預期設計一致,設計正確。

圖7仿真結果

3.7鬧鐘模塊

鬧鐘模塊設計為當定時時間到或者整點時鬧鈴響,分別有ZHENG,NAO兩個控制端子控制,低電平有效。經驗證,定時和整點報時仿真結果均符合設計要求。

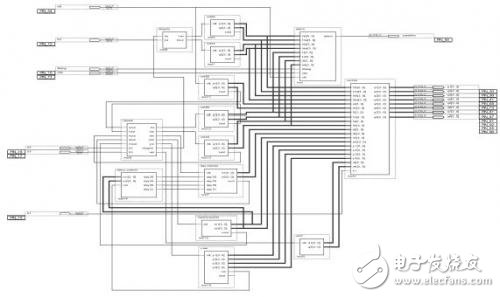

3.8頂層模塊

將各個子模塊設計好之后,并創建各自文件的圖元,以供原理圖設計文件中調用。然后在原理圖編輯窗口創建頂層原理圖文件shuzirili.bdf,即將各圖元的引線端子按照邏輯關系連接起來,得到如圖8所示的完整原理圖,也即頂層模塊。

對頂層文件分別進行時間、日期、鬧鈴功能的波形仿真,得到的仿真結果和預想設計一致,表明設計正確。

圖8頂層原理圖

4硬件驗證

在QuartusⅡ開發環境中完成上述軟件設計及仿真后,最后還需將程序下載到FPGA器件中進行硬件測試,以進一步驗證所設計程序是否正確。硬件驗證時,還需對頂層文件進行管腳分配、并編譯,然后將編譯好的目標文件通過下載電纜下載到FPGA開發板中進行驗證和調試。

采用GW48-SPOC/EDA實驗開發系統并設置在工作模式0來驗證設計結果。下面僅給出部分驗證結果。剛完成下載,數碼管顯示20000000,按兩下K1切換到時間顯示,才剛剛開始計數,同時揚聲器發出“滴答滴答”的頻率為1 Hz的響聲(為整點報時)60 s,然后通過按鍵8(K1)、鍵7(K2)、鍵6(K3)、鍵5(K4)對各個功能進行驗證。首先調整時間,按兩下K2鍵切換到分的調整,此時每按兩下K3鍵,分鐘加1,驗證過程中看到加到59就變為00;再按兩下K2鍵切換到小時的調整,此時每按兩下K3鍵,分鐘加1;用同樣的方法調整星期,天,月,年以及定時的分鐘和小時。

調整日期為2013年7月31號,當再調整天時,就變為2013年7月1號,結果如圖9所示。其他月份實驗結果也符合生活規律,與設計要求一致。

其他的測試結果,數碼管能夠正確顯示計時時間,定時驗證及時間調節、整點報時均能夠正常工作,實驗結果符合設計要求。

圖9實際電路驗證

5結語

本文基于FPGA環境設計了一個具有年、月、日、星期、時、分、秒計時顯示功能,時間調整功能和整點報時功能的數字日歷系統,并將之下載到FPGA芯片EP1C3T144-3上進行結果驗證,實驗驗證表明:數碼管能夠正確顯示計時時間,能夠通過按鍵調整時間,能夠設定時間并調整,整點報時能夠正常工作,實驗結果符合設計要求。由于設計中利用硬件描述語言和FPGA芯片相結合進行數字日歷的研究,即利用EDA技術在一定程度上實現了硬件設計軟件化,使設計過程變得相對簡單,易于修改。

另外,隨著電子技術的發展,數字日歷的功能會更加多樣化,諸如增加農歷顯示;加入溫度采集系統,能夠顯示每時每刻的環境溫度;加入節氣、節日提醒及顯示功能,提醒人們農耕及休息時間;還可以加入語音識別,方便人們不動手實現對數字日歷的調節等等。相信功能日趨完善多樣化的數字日歷將能更好地滿足人們的各種需要,為人類服務。

-

FPGA

+關注

關注

1626文章

21675瀏覽量

601944 -

芯片

+關注

關注

454文章

50442瀏覽量

421920 -

vhdl

+關注

關注

30文章

816瀏覽量

128081

發布評論請先 登錄

相關推薦

FPGA的VHDL有哪些優點?怎么理解VHDL?

基于CPLD和FPGA的VHDL語言電路優化設計

怎么設計優化VHDL語言電路?

怎么利用CPLD/FPGA的VHDL語言優化電路?

如何利用FPGA和VHDL語言實現PCM碼的解調?

淺析嵌入式FPGA與HDL硬件描述語言

VHDL語言在FPGA/CPLD開發中的應用?

采用CPLD/FPGA的VHDL語言電路優化原理設計

基于CPLD的VHDL語言數字鐘(含秒表)設計

利用VHDL語言與FPGA器件設計數字日歷

利用VHDL語言與FPGA器件設計數字日歷

評論