在數字信號處理領域,濾波器無疑是個非常重要的環節。而在數字濾波器中,有限脈沖響應(FIR)濾波器因為其線性相位的特點,應用尤為廣泛。實際應用中FIR濾波器分為常系數FIR濾波器和變系數FIR濾波器。常系數FIR濾波器的系數固定不變,可根據其特點采用分布式算法進行設計,故實現起來速度快,消耗的資源少。變系數FIR濾波器的系數是不斷變化的。當前含有變系數FIR濾波環節的芯片普遍存在速度與處理級數的矛盾,有效解決此問題具有重要的現實意義。

隨著片上系統(SOC)時代的到來,可編程邏輯器件不僅為FIR濾波器的設計提供了一條可行而高效的方法,而且更被廣泛地使用于數字信號處理的各個領域。采用INMOS公司的IMS A100級聯型信號處理器為模板,以FIR濾波器設計為核心,用FPGA技術開發設計級聯型信號處理器,能夠應用于數字FIR濾波、高速自適應濾波、相關和卷積、離散傅里葉變換、脈沖壓縮、線性預測編碼語音處理、高速定點矩陣乘法等,有較好的應用前景和發展空間。

1 FIR濾波器結構設計

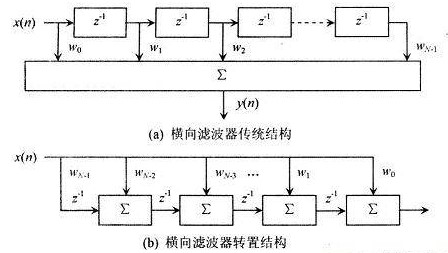

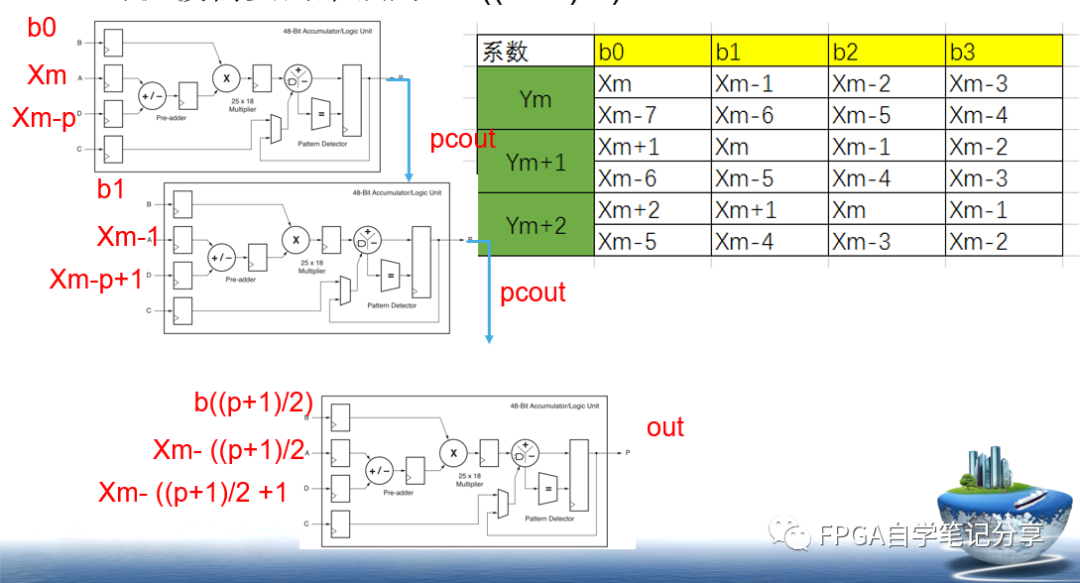

傳統的FIR濾波器橫向結構如圖1(a)所示,為提高系統處理速度,求和單元∑可采用流水線結構。圖中的N階濾波器從系統開始工作到第一個輸出數據有效,需經過N個周期,系統最大速度是由一次乘法和N個乘法結果求和運算消耗的時間決定,因而運算速度很低。采用流水線結構后,運算速度則由一次乘法運算決定,運算速度得到提高。為了系統結構的有效設計,根據FIR濾波器結構的可逆性,可采用圖1(b)所示的轉置結構。

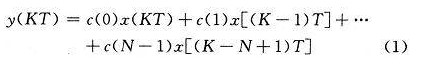

在橫向濾波器的轉置結構中,N個相同的處理單元級聯就組成了濾波器,因此系統能在保證計算結果不溢出的前提下,只改變級聯處理單元的數目就能方便地調整濾波器的級數。在t=KT時,濾波器的輸出為:

實際應用中常常會用到高階FIR濾波器,但一塊芯片的資源和容量畢竟有限,不能很好地滿足設計要求。從圖1(b)所示的結構可以看出,多片FIR濾波器可以級聯起來,構成高階FIR濾波器,無需任何附加邏輯,也不會降低運算速度,同時保持運算精度,故對比后優先選擇圖1(b)的濾波器轉置結構。

考慮到FIR濾波器系數的對稱性,在橫向濾波器的轉置結構中再加入一條反向相加、延時支路,把單片FIR濾波器的級數由N擴展到2N,適合于階數M為N<M≤2N的濾波器使用。系統只需用一個信號便可實現對芯片級聯使用或單片使用的控制,具體實現結構如圖2所示。

為了讓設計的信號處理器能用于自適應信號處理、快速傅里葉變換等領域,還必須使系統能根據用戶的要求實時改變當前系數。一般有兩種方案可以實現:一是通過一個寫入端口直接修改當前系數;二是準備多組備用系數,并可以在與系統工作時鐘異步的情況下對這些備用系數進行修改。方案一可以節省一定的系統資源,但對一組當前系數的修改需要較長時間,且此段時間內系統無法正常工作,故實時性較差;方案二雖然消耗了較多的系統資源,但系統能在準備系數(即修改備用系數)時正常工作,修改當前系數只需將當前系數和備用系數交換,交換系數的過程只需一個時鐘節拍即可完成。綜合考慮各方面因素,方案二具備更好的系統性能,故優先選擇方案二。

2 系統設計與FPGA實現

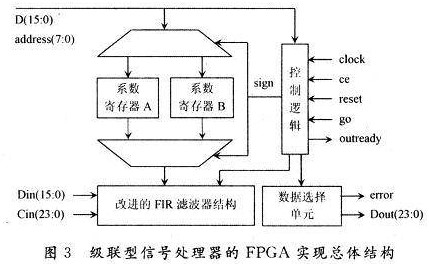

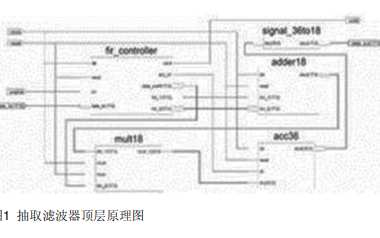

圖2的FIR濾波器結構是高速、高精度的數字式橫向濾波器結構,在數字信號處理應用中可作為功能塊,完成高速離散傅里葉變換、卷積和相關,以及濾波功能。級聯型信號處理器的設計正是基于此結構,其FPGA實現的總體結構如圖3所示。

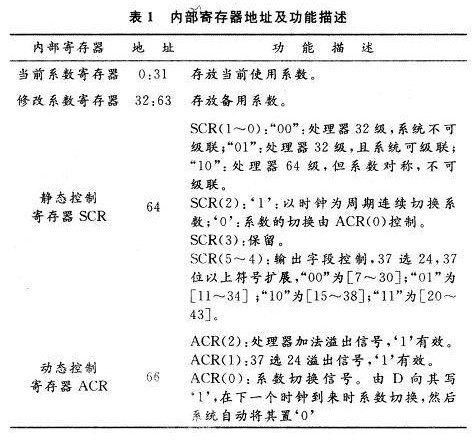

此級聯型信號處理器的外部輸入數據Din字長16位,系數字長16位,輸入數據和系數均采用二進制補碼方式。內部有A,B兩組系數寄存器,一個存儲當前系數,另一個存儲修改系數,用戶可通過數據線D在與系統時鐘異步的情況下對系數進行修改,也可使A,B兩組系數在系統工作的過程中相互“交換”。系統具有用戶控制切換和系統自動切換兩種系數切換方式。為了保持完整的數據精度,對于延時、乘法和相加鏈的中間結果是以滿精度進行運算的,若N=2K,則系統的滿精度為31+K位,考慮到單片使用時N級可擴展到2N級,所以應選用的滿精度為32+K位,本系統采用32階濾波器設計,故滿精度為37位。在延時、乘法和相加鏈的輸出端,設計一個可編程的桶形移位器(即數據選擇單元),它可從四組24位數據字段[7~30],[11~34],[15~38]和[20~43]字段中任選一種,這四組字段從FIR濾波器輸出的37位結果[0~36]中得到,所選的24位在輸出前需進行舍入或符號擴展,至于如何選擇,則根據實際應用而定。另外,本系統還為用戶提供了系統復位(reset)、工作許可(go)、狀態監測(error,out-ready)等常用握手信號。用戶可以讀寫控制邏輯中的狀態控制寄存器來切換當前系數,選擇輸出字段和設置系統工作模式(單片或級聯,當系統課用于級聯時,Cin為級聯輸入),其內部寄存器的詳細描述見表1。

用戶還可以通過數據線D、地址信號address、讀寫控制信號W、系統使能信號Ce、片選信號Cs等對系數寄存器A,B以及狀態控制寄存器進行讀寫。

3 FPGA仿真

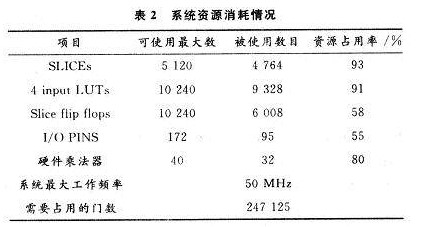

系統利用FPGA實現了一個32階的級聯型信號處理器,選用的FPGA芯片是XILINX公司的集成了18×18位硬件乘法器的VirtexⅡ系列的XC2V1000-5-FG256,其資源消耗情況如表2所示。

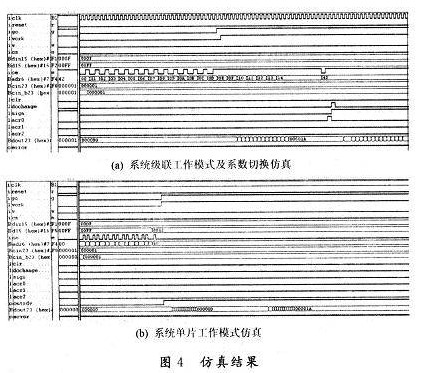

為了方便仿真和結果觀察,選用固定值輸入,圖4(a)和圖4(b)分別是系統級聯型工作模式及系數切換仿真和系統單片工作模式仿真結果。

從圖4(a)和圖4(b)可以看出,系數寄存器和內部控制寄存器可以正確讀寫,當輸入系數切換指令后,系數正常交換,整個系統工作正常。

4 性能分析

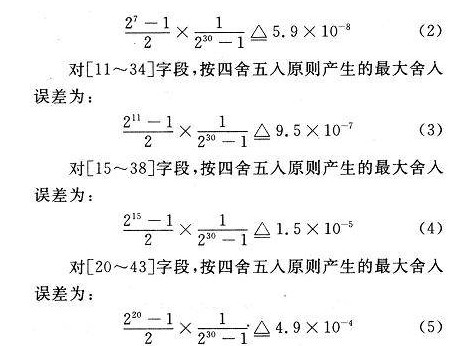

系統的輸入數據和系數都是16位的二進制補碼,所以中間結果的[0~30]字段對應著-1~+1。而系統的中間結果是以滿精度運算的,所以系統輸出的誤差產生于數據選擇單元,四組字段會產生不同的誤差。

對[7~30]字段,按四舍五入原則產生的最大舍入誤差為:

系統的仿真結果和性能分析都表明,系統可正常工作,且最高工作時鐘可達到50 MHz。

5 結語

討論了級聯型信號處理器的FPGA高效實現,通過系統論證、仿真和硬件調試證明,設計方法正確有效,系統功能實現正常且穩定,為FIR濾波、快速傅里葉變換、自適應濾波等應用提供了一條可行之路,其性能可以隨著可編程邏輯器件的發展而不斷提高。

-

FPGA

+關注

關注

1626文章

21666瀏覽量

601833 -

濾波器

+關注

關注

160文章

7728瀏覽量

177676 -

soc

+關注

關注

38文章

4122瀏覽量

217935

發布評論請先 登錄

相關推薦

基于FPGA的FIR濾波器設計與實現

并行FIR濾波器Verilog設計

串行結構的FIR濾波器設計 (含有代碼 文檔資料)

基于FPGA的硬件加速器的FIR流水結構濾波器實現、設計及驗證

基于FIR濾波器結構實現級聯型信號處理器FPGA的設計

基于FIR濾波器結構實現級聯型信號處理器FPGA的設計

評論