自由立體顯示器是一種無需佩戴輔助裝置就能觀看三維立體效果的顯示器。由于立體顯示器能夠真實還原三維信息,因此在軍事、商業、醫療等領域有著廣闊的發展前景。

隨著立體顯示器研究的不斷發展,自由立體顯示技術日趨成熟,不斷涌現出各種新型的立體顯示技術。其中基于視差的立體圖像顯示技術以實現方便和技術成熟的優點被廣泛應用。傳統的立體圖像源通常不能直接用于新型立體顯示器顯示,為立體顯示器提供合適的圖像源成為立體顯示研究的一個重要環節。本文介紹一種基于視差原理的立體顯示器的視頻轉換系統,它能夠將已有的立體視頻格式轉換成所需的視頻格式。

基于視差的立體顯示器需要在屏幕上同時顯示一對立體圖像,因此顯示器所需的圖像格式也不同于平面顯示器。本文將以輸入左右格式(Side-by-Side)的視頻信號為例,詳細描述該信號格式轉換為一種液晶立體顯示器格式的設計與實現。該系統以FPGA為核心,采用全數字的數字視頻口DVI(Digital Visual Interface)作為液晶顯示器的視頻接口,并且使用一片DDR SDRAM構建了高速的幀緩存系統,保證了數據的實時處理。系統可以工作在2D和3D模式下,實現顯示器的平面/立體兼容,在1 280×1024@60 Hz的19寸立體顯示器上工作穩定,滿足系統要求,通用性很好。

1 系統設計

1.1 目標視頻格式

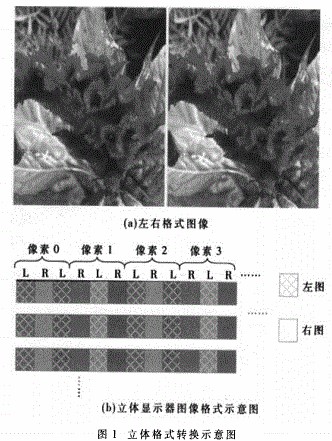

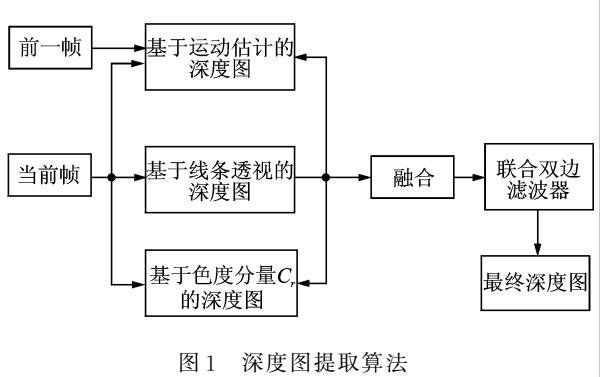

目前存在大量左右格式的立體圖像和視頻。所謂的左右格式,就是在一幅完整的圖像上,將一對立體圖像平行放置在圖像的左半邊和右半邊,如圖1(a)所示。觀看者左眼只看到左邊的圖像,右眼只看到右邊的圖像時就能看到立體圖像。一種基于液晶和視差原理的自由立體顯示器,將左右圖像分別放在亞像素列的偶數列和奇數列。以屏幕分辨率為1280×1024為例,原圖第0“639列為左圖,640”1279為右圖,則第0列和第640列像素組成變換后圖像的第0列和第1列;第1列和第641列組合為第2第3列……依次類推。組合的方式為交換對應像素的綠色分量。合成后的效果如圖1(b)所示,左右圖像的亞像素在水平方向間隔排列。

1.2 硬件系統設計

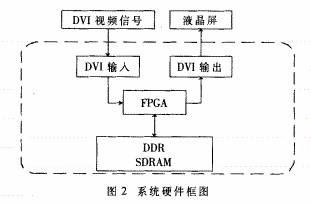

系統的硬件框圖如圖2所示。該系統采用DVI作為視頻輸入輸出接口。DVI作為一種全數字的接口標準,已經成為液晶顯示器必備的一種接口。與VGA相比,它的優點在于采用數字信號傳輸,沒有A/D、D/A二次轉換帶來的信號損失。其中輸入輸出分別采用TI公司的TFP401和TFP410芯片,該芯片支持最高165 MHz的像素時鐘,即對應1600×1200@60 Hz的分辨率。FPGA芯片采用Xilinx公司的Spartan3E系列的XC3S1600E,該芯片具有較為豐富的資源,并且成本較低。為了滿足視頻數據存儲的需要,該系統還配備了一組位寬為32 bit、容量為64 MB的DDR SDRAM存儲芯片。當系統工作在2D模式時,FPGA采集由DVI輸入的視頻數據,經SDRAM緩存后發送給DVI輸出芯片;當系統工作在3D模式時,FPGA先對讀入的數據實時進行格式轉換后再寫入SDRAM,然后從SDRAM讀出轉換好的數據發送給DVI輸出芯片,立體顯示器接收到的即是對應的立體格式的數據。該設計利用DVI輸入輸出時序上的特點,分時利用一組SDRAM實現了類似“乒乓操作”的幀緩存功能,充分利用了系統資源。

2 FPGA邏輯設計

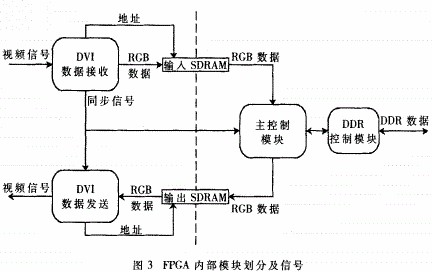

系統設計的主要任務是完成FPGA對各個模塊的控制,包括DVI數據的輸入輸出、SDRAM的讀寫控制、數據的緩存以及各模塊之間的協調等。其中,數據的緩存是整個系統設計的關鍵。FPGA內部的模塊劃分如圖3所示,虛線左邊的模塊采用視頻的像素時鐘作為工作時鐘,頻率取決于分辨率;右邊的模塊采用系統自身生成的時鐘作為工作時鐘,頻率最高為166 MHz。

2.1 DVI輸入輸出

DVI輸入輸出控制,一方面根據同步信號采集視頻數據;另一方面要根據輸入信號生成輸出信號,包括行同步(HSYNC)、場同步(VSYNC)、數據有效信號(DE)等。以輸入視頻信號1 280×1 024@60Hz為例,根據VESA(Video Electronics Standards Association)標準,此時像素時鐘fp=108 MHz,每一行信號期間,當DE信號為高電平時,數據有效。于是可以在檢測到DE信號的上升沿后開始采集數據,而在DE轉為低電平后停止數據的采集。采集的數據寫入SRAM,SRAM地址由同步信號解碼產生。

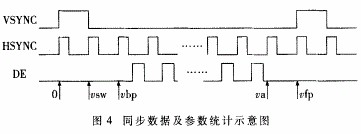

為了精確生成輸出DVI的同步信號,需要在采集DVI輸入數據的同時統計輸入信號各個特征脈沖維持的時鐘數。圖4所示為以行為單位統計場同步信號的參數。輸出端在根據統計參數生成DVI同步信號的同時,當輸出信號的DE為高電平時,從輸出SRAM讀取相應的數據送到數據總線。

2.2 數據緩沖

數據緩沖是整個設計的關鍵。數據的存儲緩沖是信號處理中通常會遇到的問題。視頻信號的緩沖,由于其數據量大,使得對存儲器的容量和速度都提出了比較高的要求。當系統工作在1 600×1 200@60 Hz的最大分辨率時,存儲一幀數據所需的容量是d0=1 600×1 200×3 B=5.49 MB,此時的數據率為d=d0×60=329.59 MB/s,這要求存儲器具有大容量和足夠快的速度。常用的數據緩沖方法有FIFO、雙端口RAM和乒乓操作3種。

FIFO的使用非常簡單,缺點是只能順序讀寫,并且容量較小。雙端口RAM可以做隨機存取,且速度很快,然而SRAM的價格昂貴,容量通常在幾百Kbit到幾Mbit大小,所以也不適合做大容量的存儲。而SDRAM有容量大且速度較快的優點,所以采用SDRAM的乒乓操作既可以滿足視頻數據大容量的要求,又能滿足速度上的要求,是一種較好的方案。

綜合以上方案,同時根據輸入輸出數據時序上的相似性特點,本文提出了一種時分復用單片SDRAM的方案。該方案用一組SDRAM實現類似“乒乓操作”的幀緩沖效果。

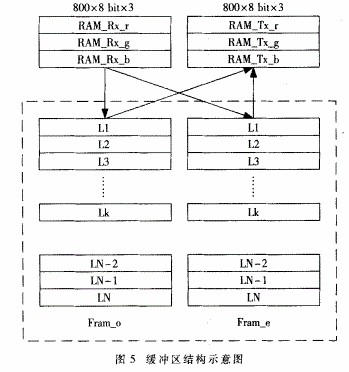

整個存儲緩沖的結構如圖5所示。輸入輸出均采用兩級緩存的方式。其中第一級緩存可以存儲一行數據,采用FPGA片內雙端口SRAM實現;二級緩存是可以存放完整兩幀數據的DDR SDRAM,作為主存儲器。

當某一幀數據到來時,輸入端的數據不停地從雙端口RAM的一個端口寫入SRAM_Rx。每當檢測到DE的下降沿,說明已經有一行的數據寫入完畢,則從另外一個端口將SRAM_Rx的數據寫入DDR用于保存當前幀數據的存儲區。寫入一行結束時,輸入端要等到下一個DE下降沿到來才會再次有讀寫SDRAM的需求。也就是說SDRAM此時處于空閑期,于是馬上從之前保存好的上一幀數據中讀出相應的一行數據寫入SRAM_Tx,輸出端則在寫入SRAM_Tx一行完畢后從SRAM_Tx的另一個端口讀出數據。這樣一直到一幀結束。當下一幀數據到來時,交換讀寫所指向的幀存儲區,這樣保證了原視頻信號的幀率不變。

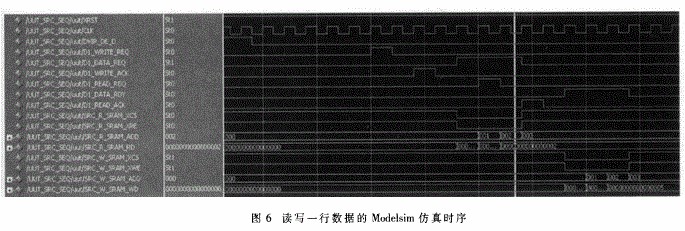

為了使設計簡單,DDR控制器模塊DDR_IF使DDR工作在BL(Burst Length)即數據突發長度等于2的狀態,并且以行為單位完成一次讀寫流程。每次要寫入或者讀出一行數據時,主控制模塊MAIN_CTL向DDR_IF發送讀寫請求,然后發送一行數據所需要傳送的突發長度的數量BL_CNT,以及該行數據要存入DDR的bank地址、行起始地址、列起始地址。之后,MAIN_CTL和DDR_IF進入讀寫流程。一行數據讀寫操作的Modelsim時序仿真如圖6所示,圖中以一行數據有3個像素為例。

根據以上分析,DDR在一行數據的時間內被復用,理論上只要滿足寫入一行加讀出一行數據的時間小于一行數據的持續時間Th即可。在1 600×1 200@60 Hz的分辨率下,行周期Th=13.3,當DDR工作在165 MHz時,其讀一行數據加寫一行數據的時間為:Tl=1 600×2/165 M×2=9.7<Th。即使考慮到DDR在讀寫之外的其他操作上花費的額外時間,也能夠滿足要求。

2.3 格式轉換

2.3.1 3D模式

2.3.2 2D模式

對于本文設計的系統,對程序稍作修改即可實現2D/3D兼容。只須在輸入端,第k個像素到達時,各分量分別存入地址addr=k即可。

本文介紹的立體視頻轉換系統能夠在不影響幀率的情況下進行實時轉換,并且滿足2D/3D兼容的需要。該系統目前已應用于立體顯示器格式轉換。DVI接口的使用,使得該系統有著廣泛的兼容性。此外,系統用一片SDRAM實現了幀緩沖的功能,在充分利用系統資源的同時,使得整個系統的設計更為簡潔,有利于減小體積和降低成本。同時,該系統實際上構建了一個通用的視頻處理架構,具有很好的擴展性,程序只需稍作修改即可用于其他尺寸、其他格式視頻源(如上下格式、時分格式)、其他立體實現方式(如按行或者按列分割左右圖像)的立體顯示器。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601846 -

顯示器

+關注

關注

21文章

4948瀏覽量

139823 -

視頻

+關注

關注

6文章

1933瀏覽量

72811

發布評論請先 登錄

相關推薦

采用FPGA技術實現立體顯示器的視頻轉換系統的設計

采用FPGA技術實現立體顯示器的視頻轉換系統的設計

評論