將無線功能集成到SoC 中要特別注意分區和架構的決策,而這些決策一般沒有明確答案。

要 點

市場的需求驅動將RF 電路集成到SoC (單片系統)中。

保持RF電路做在單獨芯片上仍有一些令人信服的理由。

無線電架構的選擇,特別是接收器,還遠遠沒有定論。

架構師必須從整個系統考慮,而不能只局限于單個芯片。

無線鏈路在電子系統中的應用越來越普遍。WiMax 及3G蜂窩網絡主導著高速數據傳輸的無線連接領域,而像ZigBee 及Wibree 等標準則占據了低速數據傳輸與低能耗市場。但不論哪種情況,市場經濟及消費者都期望系統架構師至少能將無線電硬件集成到SoC (單片系統)中。

圍繞這一要求出現了一些關鍵問題。首先,單芯片是最佳方式嗎?或許將無線電隔離在單獨芯片上更適合應用?其次,給出了這些問題的答案后,那么哪種架構最適合接收器和發射器?在這些答案背后還有其它問題:架構師能否系統地進行決策?或者他們必須不僅逐個進行決策,而且要采用逐個決策處理的流程?

某些廠商,特別是手機廠商,似乎覺得除了將無線電完全集成到SoC中外,其它都像電子管調諧器一樣過時了。然而, 是采用RF 工藝將無線電在單獨芯片上實施 ,還是至少以vanilla-CMOS-logic 工藝將部分RF 電路實施到SoC上 ,這一決定并不容易。系統架構師必須考慮市場期望、壽命周期成本、性能需求及項目風險等問題。架構師需要全面分析所有這些因素,才能做出明智的決策。

首先列出的是情感,而不是客觀的判斷。特別是消費類移動設備市場,成本和形式因素的影響極大,通常的觀念是只有單芯片方式可以接受。Broadcom? 無線電技術工程部的高級總監Maryam Rofougaran說:“問題是實施單芯片方案很困難,所以需要采用數字CMOS,”“再說RF-CMOS 工藝的成本也非常高,所以我們把目標對準了數字CMOS 工藝。”

其它經營手機業務的廠商,至少是市場份額較大的廠商,都同意這種觀點。Staccato Communications的首席技術官Robert Aiello認為,“對我們來說,單芯片僅僅是一種業務考慮,我們只針對單芯片解決方案開展業務。” “因此,我們必須建立一個有大規模生產集成無線電經驗的團隊。”

Texas Instruments(TI)或許是這種方式最堅定的支持者,他們已經將其CMOS單芯片無線電架構作為品牌產品DRP (數字射頻處理器)推出。“單芯片方案具有明顯的優勢,” TI無線終端業務首席技術官Bill Krenik解釋道,“如今,用于低成本應用的無線電芯片已能采用數字工藝大量地制造了,” Krenik還說:“單芯片架構的設計復雜,開發成本大,因此這種設計需要大的市場以及有著良好預期的市場份額。市場份額較小的產品,如高檔手機,不適合采用單芯片架構。”

另一種不容忽視的觀點并非來自于客戶,而是風險投資界。“如果你是當今的創業者,不管你認為是否合適,你的投資方都會督促你采用數字CMOS進行單芯片設計,”IBM客戶經理Teddy O’Connell說,“但是在做出決策前,還是需要考慮某些非常重要的問題。”

許多問題都與方案的成本相關。O’Connell 和其他人指出,在多芯片封裝成為主流的情況下, 單芯片相對于多芯片設計的經濟性已經有所改變。雙芯片組裝的預算成本可能比單個封裝芯片大,但這種差異只是均差的開始。“單芯片只有20% 的部分為RF電路,成品率明顯低于數字部分,”O’Connell 指出,“隨著設計轉向更精細的幾何尺寸, RF 部分將會增大而不是縮小。而且,對RF 性能的要求會推動整個設計邁向更先進的數字工藝節點,而如果采用單個RF 及數字芯片是無法實現的。”

然而成本均差難以捉摸。選擇單芯片還是多芯片策略會影響無線電架構的選擇,這又對無線電所需外部無源元件的數量和質量產生重大影響。除去元件、空間、插入及測試等成本,這些無源元件會對系統總成本產生較大的影響。

性能要求和設計風險也相互關聯。理論上,65nm 或90nm CMOS邏輯工藝最適合RF。“就在幾年前,千兆赫范圍的RF要采用GaAs(砷化鎵) 工藝加工的昂貴晶體管。”Analog Devices的業務開發總監Doug Grant評論說,“但工藝尺寸減小導致寄生電容降低、傳輸路徑縮短以及晶體管預算增加,所有這些都對RF 設計師有利。”

采用這種工藝的晶體管截止頻率對于90nm工藝而言能夠高于40GHz,采用65nm 工藝的晶體管截止頻率還要高。小型器件中較低的串聯電阻意味著較低的噪聲本底,能稍稍補償較低的工作電壓,其線性度也不錯。IBM公司的O’Connell說道:“CMOS中的三階交調截距要勝過SiGe(硅鍺)”。只要電路不要求較高的Q值,就可以制造相當不錯的螺旋電感。

既然如此,為什么還有人認為性能是在單獨芯片上采用專用RF工藝的理由呢?原因是多方面的。

工藝和性能

一個合理的原因是頻率。“管理需求促使超寬帶射頻鏈路向更高波段發展。這種壓力要求我們設計的產品在10 GHz 的頻率上運行”, Alereon工程與運營副總裁David Shoemaker說,“在該頻率下,CMOS的 快速運行特性非常合適。但是,這些頻率即使沒有大的波動也會對CMOS造成嚴重問題。例如, VCO(壓控振蕩器) 容易變得不穩定,并伴有增益平坦度的問題。”分析這些問題后,Alereon 選擇了以SiGe 工藝實施RF 前端,這樣可以遷移到CMOS。“我們可以選擇遷移電路,但目前這種做法不會大量節約成本。”Shoemaker 說道。

除了增益外,架構師們采用CMOS工藝實施 RF還需要考慮線性度問題。無線電對非線性的敏感度取決于應用和調制方案。“標準對于能否以特定的技術制造無線電有很大影響,”Staccato公司的Aiello表示,“例如,我們使用QPSK (正交相位偏移鍵控)而不是64-QAM (正交調幅),從而可降低對RF 部分線性度的要求。”

另一個采用數字CMOS 的大問題是模型。 數字CMOS器件通常采用高頻數字模型,而更少或不涉及小信號模型。 “對于早期的RF 用戶,不論是否采用CMOS工藝,模型總是個問題,”Cypress Semiconductor的首席系統架構師Dave Wright說,“我們應用于無線USB 產品的BiCMOS 工藝,最初也是為高速通信電路設計,而不是專為RF設計的。 它有很好的特性,但我們采用了多個運行點而不是一個運行點。”

晶體管模型并不是唯一的問題。噪聲模型,特別是通過電源及襯底傳播噪聲的性能良好的模型非常關鍵。運行電壓較低的任何RF 設計通常會產生噪音。而在諸如具有片上功率放大器的收發器這樣的系統中,及出現多個互不相關RF 信號的多天線設計中,情況也是如此。即使模型本身很完善,你會對工藝工程師致力實現大型數字設計的良好成品率牽腸掛肚。他們沒有必要注意小信號RF模型參數,而是將他們的工藝集中關注于門電路和SRAM 單元。因此,采用數字CMOS的設計團隊,有責任實現自己的模型組并與代工廠建立緊密的關系來校準其模型。

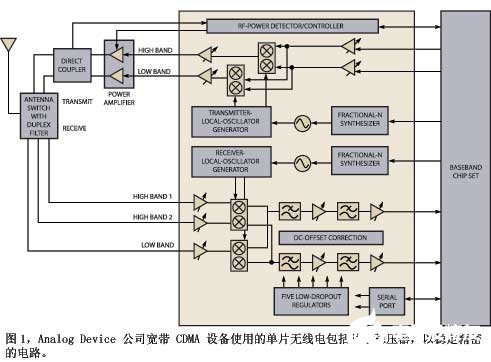

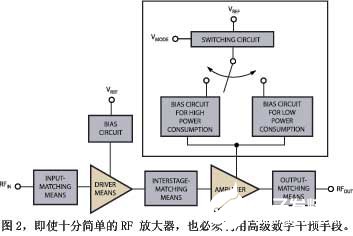

模型的不確定性增加了難于量化的設計風險。 盡管存在這樣的困難,設計師們必須在決策中考慮這些風險。 如果不能接受設計存在一種或三種貌似有理的風險,那么有兩種選擇:一是依賴成功的設計團隊和成熟的RF 工藝,二是依賴數字校準RF 電路來補償模型或變化量的不確定性。 “基本上對于缺少信心的模型我們都會進行補償。”Analog Devices的Grant說。ADI 設計師為了在工作溫度范圍內穩定CMOS信號路徑,有時在簡單的偏置發生器中使用20個或30個額外晶體管,這并不是什么稀罕事。 Analog Devices有時在精密的RF 電路 (圖1)旁邊增加低壓差穩壓器來控制CMOS 芯片中的電壓變量。 設計師有時也會采用數字技術: 使用 ADC 來快速測量電路的運行點及計算補償參數,同時加載DAC 來調整偏壓電流或補償電流 (圖 2)。 有些設計師甚至開玩笑地說他們正轉向一種將 DAC 輸出附加在每個RF 晶體管引腳上的設計風格。

“毫無疑問實現無線電的可升級性是一種數字密集型工藝,”TI的 Krenik說,“例如,線性度問題就是一個基本的挑戰。傳統的設計要求極高線性度的高壓前端。但采用現今的工藝已經可以忽略這個問題。現在,我們使用精密的數字控制偏置電流與其它參數,從而實現性能較差電路的線性化。”

但這種級別的控制本身又會引發單芯片/雙芯片的爭論。“功耗是最重要的參數之一,” NextWave Wireless的產品研發部高級副總裁Adam Gould說,“通常,人們認為較老的工藝所消耗的功耗更多。但是在CMOS中,功耗可實現線性度。例如,WiMax中功耗預算最大的問題之一就是實現功率放大器足夠的線性度。如今,優化的RF 工藝可以更好地降低功耗。”

所以選擇單芯片還是多芯片不可一概而論。某些市場不提供任何實際的選擇方案:市場期望單芯片方式,成本限制需要單芯片方式。這些市場中典型的應用恐怕要說基帶數字CMOS SoC 集成無線電。而在其它市場中,設計團隊 也可以采取多芯片封裝,這主要取決于性能和功耗要求、無線電架構的選擇、穩定模型的可用性及團隊的經驗。“如今在寬帶CDMA 中既可以看到數字CMOS ,也可以看到SiGe RF,” IBM的O’Connell說。對于一些其它領域,特別是10GHz 和10GHz以上的頻率范圍,目前還不存在適合接收器的RF 工藝。“WiMax、5GHz 網絡及雷達目前仍然是SiGe應用場合,”O’Connell 繼續說道。但要注意,SiGe 或GaAs等特殊工藝所需的頻率大大低于功率放大器和天線開關的頻率,從而需要比接收器更高的功耗。

除了工藝技術的選擇外,功率放大器依然存在其它問題。“隨著有效通道長度變短,集成功率放大器的問題變得越來越困難,”Rofougaran說。“由于多種原因,比如可靠性和局部發熱等,極小型晶體管不能承受較大信號。在某些工作條件下,功率放大器中會有相當大的電流。”盡管如此,Broadcom 還是在藍牙芯片等某些低功耗的應用中集成了功率放大器。

“從技術角度來說可以集成達到大約10 mW的任何功率放大器,但實際上目前4 mW已經是極限,”Cypress的Wright說道,“超過這一限度,功率放大器的某些結構即使在低功耗模式下也能消耗大量靜態功率,從而縮短電池壽命。在更先進的工藝中,電壓擺幅也是個問題。”

無線電架構

采用單芯片或雙芯片的決策與設計師實施的無線電架構決策相互影響,這些決策包括無線電中接收器和發射器的選擇。人們對接收器存在一種偏見,認為越早對信號進行數字處理,效果就越好。某些廠商曾將ADC 置于低噪聲放大器的輸出端,直接對輸入的R F數字化,而在轉換器輸入與白噪聲之間只采用一個帶通濾波器。另一極端,某些設計師繼續使用可以追溯到電子管無線電年代的超外差接收器架構。而最常采用的直接轉換接收器架構介于兩者之間。

通常理想的情況是只將一個ADC 置于低噪聲放大器中。這種方式基本上消除了RF 設計的問題,同時帶來新的可能性。例如,簡單數字化整個蜂窩頻譜的蜂窩基站可即時對頻帶進行濾波,并可對多個調制方案選擇通道。設計師不需要為每個主動會話分配RF 前端,同時數字域中的濾波質量會超過任何物理濾波器。

“但這種設計的轉換器很難實現,需要足夠的電流,”O’Connell說。為了采集足夠的信號以確保數字處理的成功,轉換器需要擁有較大的采樣速率和較寬的動態范圍, DSP從可以從相鄰通道信號及帶外噪聲抽取少量的輸入信號。由于類似的原因,這種方案同時具有出色的線性特點。雖然這種轉換器設計目前已有可能,但O’Connell 認為這種轉換器設計只適合于高端設計,如基站和多標準的“全球性電話。”

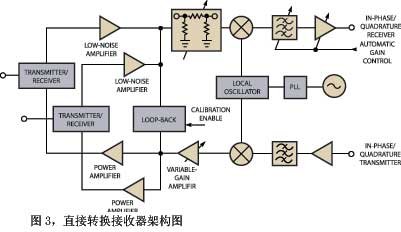

對多數無線電架構師來說直接轉換接收器 (圖3)是更好的選擇。 在這種架構中,RF 信號由低噪聲放大器傳送至RF 信號與來自本地振蕩器的I (同相) 和Q (正交) 信號相乘的混合器。 結果就產生基帶頻率中的I和Q兩個信號。 通常,基帶信號通過抗混疊濾波器進入一對ADC中。

這種方式卻并不能大大簡化問題。直接轉換架構出現在電子管無線電早期超外差技術之后,但由于各種各樣挑戰性的問題,隨后被設計師放棄。低噪聲放大器和混合器必須為線性,本地振蕩器必須清晰穩定,而直接轉換架構的適合程度在某種程度上取決于調制方案。“這取決于數據,”Broadcom公司的Rofougaran說道,“我們的2046 藍牙芯片需要處理數據帶寬比較窄、很多信號頻譜接近直流的GFSK (高斯濾波頻移鍵控) 等問題。由于直流漂移取消,直接轉換架構存在問題,所以,我們使用低IF 超外差結構。與此相反,無線局域網有較寬的數據帶寬和較少的接近直流信息,因此我們采用直接轉換架構。”

Cypress 還選擇了低IF 超外差架構來實施無線USB 設備。“這種架構最適合我們的情況了,”Wright 解釋說,“我們良好的電路設計比直接轉換架構具有更好的抑制效果。而且,低 IF在邏輯電路中所消耗的功耗并不多。在某些情況下,我們可以轉向直接轉換,但最好的選擇是重新使用現有的架構。”

一個不適合采用超外差的因素是采用這種方法對接收器進行系統集成比較困難。Alereon公司的Shoemaker 指出,IF 部分可生成不必要的頻率毛刺 ,雖然不影響超外差接收器本身,但可嚴重影響系統中的其它接收器。由于當今很多移動設備中包含多個無線電,因此在設計設備之前,系統架構師必須為封裝中所有無線電仔細規劃頻譜 。

發射器方面也有類似決策。這時,最常用的架構是極性環路功率放大器。這種設計包括了振幅和相位信號的回饋環路,具有良好的振幅與相位線性特點,對于類似采用兩種數量進行編碼信號的QAM等調制方案非常重要。但設計師還討論了其它方案,包括未來可能的方案,比如以功率DAC直接驅動天線。

所以在對SoC無線電的決策中,終端市場及投資方要求廠商進行單芯片設計的壓力日益增長,至少是對小信號的RF 電路采用單芯片設計。然而使用這種方法的設計師需要克服集成過程所遇到的很難對付的困難。許多問題反映了積極使用數字電路進行校準和控制,以及反映了設計經驗。但這一行業發展到高頻接收器RF 部分采用SoC還有較長的路程,而距離只采用最低功耗的發射器電路則更遠。

由于CMOS工藝技術并沒有轉向更友好的RF 設計,如數年前TI做的一樣,集成度的不斷提高將意味著在電路設計與無線電架構中實現重大創新。Analog Devices公司的Grant 對設計師如何實現這一進步做出了重要的評論:“在數年前的一個項目中,我們只是觀望整個設計。”他說。“我們體會到,RF、數字化及軟件設計師之間并沒有真正地相互交流。他們都只忙于自己的噪聲預算,從而導致系統效率低下。這使我們認識到必須對整個信號鏈進行優化,不能將各模塊彼此分割開來,必須全盤考慮無線電,包括濾波器、數字控制及軟件創建的運行模式,而不能只關注芯片。”

附文:高度集成RF的含意

消費無線設備市場的爆炸性增長正在促進向更高的性能和集成度發展,入市時間和測試成本也面臨著更大的壓力。一直以來測試RF設備傳統上比測試數字設備要困難。如今,由于多波段、多模式、MIMO (多入多出) 設備的出現, RF測試變得更為復雜。設備端口數的不斷增多,收發器復雜性的提高以及先進技術中PVT (工藝/電壓/溫度) 變量的增加等因素都要求有仔細的設計與測試策略,以滿足消費市場的成本壓力及創造一個現實的測試環境。

設計師既要確保芯片的性能,還要確保其合適測試策略滿足入市時間和成本目標,實現市場成功。例如,今后五年內MIMO 設備的RF 結構將從2×2增加到3×3,甚至到8×8 RF 分支。導致RF 路徑在輸入與輸出間的測試出現大幅增長。傳統的單入單出方式由于大大增加了測試時間而變得不切實際。片上DFT (可測性設計) 電路通過片上并行測試或降低外部設備需要,實現高效的多址測試 (參考文獻 A和 參考文獻B),從而有助于緩和消費無線設備市場爆炸性增長。此外,設計師必須增加片上測試電路,以創建實際的測試環境,這種環境,如果不能從外部創建,是很難建立的。這些條件包括在觀察階段與全局PVT變量平衡中對模擬電路多路徑的恒定電流進行加載。盡管RF-BIST (內建自測試) 方式目前應用還不太普遍,但已經開始解決一些問題。

在測試系統方面,工程師仍必須滿足基本的精確、穩定、可靠、低噪聲本底、高RF及基帶性能等要求。此外,這些系統必須具備靈活的系統集成架構,以對設備進行高效測試。集成架構提供了必要的密度和通道數以實現較高的并行測試效率,從而達到最少的測試時間。靈活的架構可以充分利用可行的測試資源。系統應該允許設計師在測試資源要求與可實現的測試時間、及測試成本之間做出折衷,以滿足最終產品要求。

某些新的測試方法使用設計的數學模型來測量供選擇的參數(參考文獻 C及參考文獻 D)。這些技術似乎很有應用前景,但目前還處于開發階段。

責任編輯:gt

-

CMOS

+關注

關注

58文章

5687瀏覽量

235163 -

soc

+關注

關注

38文章

4122瀏覽量

217956 -

無線電

+關注

關注

59文章

2132瀏覽量

116323

發布評論請先 登錄

相關推薦

將無線電硬件集成到單片系統上的挑戰和解決方案

將無線電硬件集成到單片系統上的挑戰和解決方案

評論