SSDl770是晶門科技公司于2005年推出的一款用于點陣顯示系統的單片CMOS彩色STN LCD驅動控制器。目前,SSDl770已經應用于傳統的工控機領域8080系列微控制器的連接,而在32位嵌入式系統領域內的應用還很少。本文主要研究LCD控制器SSDl770與ARM7TDMI內核的嵌入式微處理器SEP3203之間的系統連接及底層、上層軟件開發,并最終在產品中得到應用。

1、系統介紹

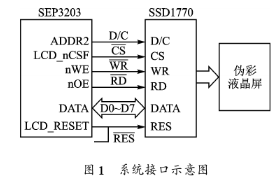

1.1 系統構成

1.2 SEP3203概述

SEP3203是由東南大學國家專用集成電路(ASIC)與系統工程技術研究中心設計的一款基于ARM7TDMI內核的16/32位RISC微控制器,面向低成本手持設備和其他通用嵌入式設備。它集成了支持黑白、灰度、彩色的LCD控制器。SEP3203中的彩色LCD控制器主要用于TFT真彩顯示,不能直接控制CSTN(偽彩)顯示,須通過外接偽彩控制器來實現偽彩顯示。

SEP3203處理器內嵌20 KB零等待的靜態存儲器SRAM,提供SDRAM控制器;可擴展支持各種SRAM接口的設備;提供可自由控制的GPIO口,同時具有多種控制器接口。

1.3 SSDl770概述

SSDl770是一個單片高度集成的偽彩點陣型LCD控制驅動器件。它內含3128l4位的圖形數據顯存GDDRAM和477kHz的振蕩電路,集成偏壓電路和DC-DC電路;具有8位PPI接口(可直接連接80/68xx MCU)、3/4線SPI串行接口和36條控制/傳輸指令。外加幾個電容器件,SSDl770就可控制驅動104RGB8l點彩色STN型LCD,4096種顏色。

1.4 電壓匹配

SSDl770 CMOS電源提供電壓為1.8~3.6V,而SEP3203輸入/輸出電壓最小為2.7V,最大為3.6V,前者的輸出可以直接作為后者的輸入,無須進行電平轉換。

2、 硬件設計

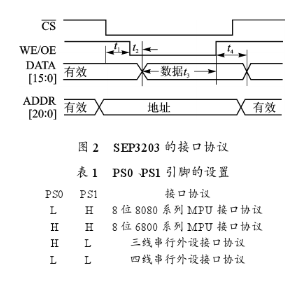

SEP3203的接口協議如圖2所示。

SSDl770同時有4種信號接口協議:①8位8080系列MPU接口協議;②8位6800系列MPU接口協議;③三線串行外設接口協議;④四線串行外設接口協議。不同的接口協議可通過FS0、PSI引腳的設置來實現,如表l所列。

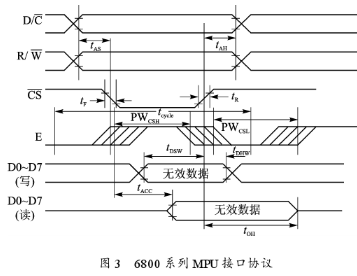

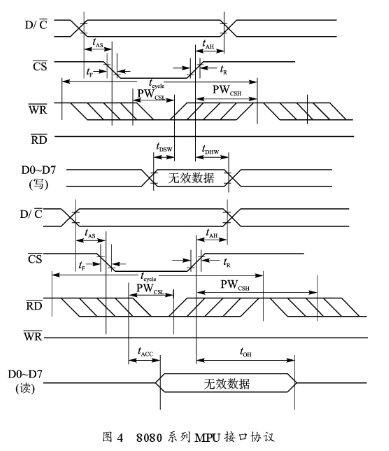

由于本設計中傳輸距離不需要過長,且考慮到速度問題,所以選擇并行接口協議。SSDl770支持2種并口模式:一種是6800系列MPU接口協議,如圖3所示;另一種是8080系列MPU接口協議,如圖4所示。

將SEP3203接口協議與這兩種MPU接口協議相比,可知SEP3203的接口協議屬于8080系列MPU接口協議。因此,采用8080接口實現SSDl770與SEP3203的連接。

SEP3203所用的接口引腳是外部存儲接口模塊(Ex―ternal Metmory Interface,簡稱EMI)中的8位數據總線、輸出使能、寫使能、地址總線、NAND Flash準備就緒/忙和控制時鐘中低電平有效的Reset。EMI的功能即提供對外部存儲器的讀/寫接口。

SEP3203的主要引腳定義如下。

◆nOE:讀使能信號,表示當前周期執行讀操作。

◆nWE:寫使能信號,表示當前周期執行寫操作。

◆LCD_nCSF:片選信號。

◆DATA:外部數據總線。

◆ADDR:外部地址總線。

SSDl770的主要引腳定義如下。

◆D0~D7:并行接口方式,雙向數據總線。

◆RES:復位信號輸入,低電平有效。

◆D/C:數據或命令選擇引腳。若為1,則數據總線上的信息當作顯示數據;若為0,則數據總線上的信息發送到命令寄存器。

◆CS:片選信號輸入,低電平有效。

◆RD:與8080 CPU接口時,為寫信號輸入,低電平有效。

◆WR:與8080 CPU接,用于寫信號(低電平有效)。

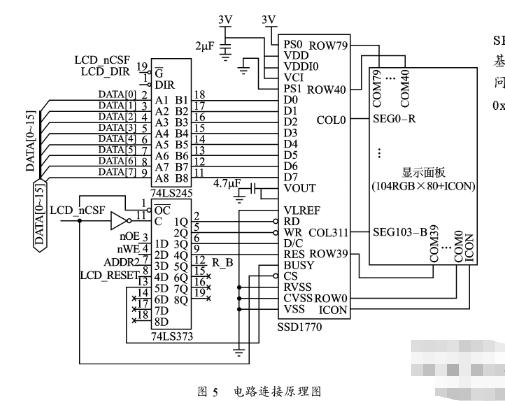

與8080系列CPU并行接口,由8位雙向數據腳DO~D7、RD、WR、D/C、CS組成。根據8080 CPU接口協議,SSDl770的DO~D7、RD、WR、RES、D/C、CS引腳分別與SEP3203的PORTB、nOE、nWE、LCD_RESET、ADDR2、LCD_nCSF引腳相連,如圖5所示。

CS信號直接由SEP3203的LCD_nCSF控制。如果CS是低電平且RD為低,則RD輸入作為讀數據鎖存信號;無論是從GDRRAM讀顯示數據還是從狀態寄存器讀狀態都需要D/C腳的控制。如果CS是低電平且WR為低,則WR輸入作為寫數據鎖存信號;無論是寫顯示數據到GDDRAM還是將命令寫入命令寄存器都需要D/C腳的控制。第一有效數據讀之前,需要一次虛擬讀。為了不產生錯誤操作,在SSDl770與SEP3203控制信號之間使用CMOS芯片。由圖5可知,控制信號D/C、CS、WR、RD都是單向的,所以使用l片單向的CMOS八位鎖存74LS373控制;而D0~D7是雙向的,因此采用1片雙向的74LS245緩沖,具體電路連接如圖5所示。

3、 軟件設計

3.1 軟件系統

LCD的軟件驅動程序是在嵌入式操作系統Asix OS上運行的。Asix OS系統是由國家ASIC系統工程技術研究中心開發的一種嵌入式操作系統,具有設計簡潔、模塊化、易移植、功耗低等特點。它是基于uITRON3.O的T-Kernel,由設備驅動、內核、文件系統、圖形用戶接口以及系統級服務5個模塊組成。結合LCD的具體運用,設計的Asix OS框架如圖6所示。

3.2 LCD初始化

在Asix OS系統之上,LCD的驅動程序通過SSDl770的初始化流程、命令參數列表以及其他資料來編寫。SSDl770的訪問有2種:一種是根據寫入不同的命令來實現對SSD1770的控制而使用控制寄存器;另一種則是通過調用GDDRAM內的地址來讀/寫顯示內容。

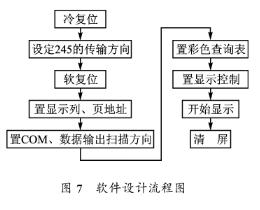

首先計算SSDl770的各端口地址。SEP3203的片選信號LCD_nCSF所對應的基址為0x34000000,所以設定SSDl770的訪問地址為0x34000010,RAM的訪問地址為0x34000018。軟件設計的流程圖如圖7所示。

初始化程序如下:

4 、結論

本設計不僅是對晶門科技公司新推出的單片CMOS彩色STN-LCD驅動控制器在嵌入式系統中應用的擴展,而且滿足了東南大學ASIC中心設計的嵌入式處理器SEP3203外接偽彩顯示的需求。既實現了在具有友好界面的工控系統中的應用,又可以在更多想要具有友好界面的系統中得到推廣。

責任編輯:gt

-

處理器

+關注

關注

68文章

19178瀏覽量

229200 -

控制器

+關注

關注

112文章

16214瀏覽量

177479 -

lcd

+關注

關注

34文章

4414瀏覽量

167135

發布評論請先 登錄

相關推薦

SEP3203處理器的FPGA數據通信接口設計

顯示控制器S6B0724的接口技術

SEP3203處理器實現FPGA數據通信接口設計

Sitara AM62處理器的資料分享

基于ARM的PC/104處理器模塊設計

SEP3203處理器與FPGA數據通信接口設計

顯示控制器S680724的接口解決方案

SEP3203F50移動終端應用處理器用戶手冊

基于ARM7TDMI內核SEP3203處理器的語音信號的軟件

基于SEP3203拉力試驗機嵌入式測控系統設計

基于SEP3203處理器的LCD轉VGA接口設計

偽彩LCD驅動SSD1770的接口設計

基于SEP3203和FPGA實現無紙記錄儀測頻系統的設計

基于和SEP3203處理器和驅動控制器SSD1770的應用接口設計

基于SEP3203處理器和SSDl770芯片實現外接偽彩顯示接口的設計

基于SEP3203處理器和SSDl770芯片實現外接偽彩顯示接口的設計

評論