近年來,多媒體技術逐漸深入到人們的生活中。MP3播放器已經成為流行的便攜式音頻播放設備,由于MP3編碼算法非常復雜,目前,一部分MP3播放器的錄音功能主要基于ADPCM算法和DSP來實現。本文闡述了ADPCM語音編解碼VLSI芯片的設計方法以及利用FPGA的硬件實現。

ADPCM算法及其編解碼器原理

ADPCM(Adaptive Differential Pulse Code Modulation,自適應差分脈沖編碼調制)綜合了APCM的自適應特性和DPCM系統的差分特性,是一種性能較好的波形編碼。它的核心思想是:利用自適應改變量化階的大小,即使用小的量化階去編碼小的差值,使用大的量化階去編碼大的差值;使用過去的樣本值估算下一個輸入樣本的預測值,使實際樣本值和預測值之間的差值總是最小。ADPCM記錄的量化值不是每個采樣點的幅值,而是該點的幅值與前一個采樣點幅值之差。

ADPCM是利用樣本與樣本之間的高度相關性和量化階自適應來壓縮數據的一種波形編碼技術。ADPCM標準是一個代碼轉換系統,它使用ADPCM轉換技術實現64kb/s A律或u律PCM(脈沖編碼調制)速率和32kb/s速率之間的相互轉換。ADPCM的簡化框圖如圖1所示。

ADPCM編解碼器的輸入信號是G.711 PCM代碼,采樣率是8kHz,每個代碼用8位表示,因此它的數據率為64kb/s。而ADPCM的輸出代碼是“自適應量化器”的輸出,該輸出是用4位表示的差分信號,它的采樣率仍然是8kHz,它的數據率為32kb/s,這樣就獲得了2∶1的數據壓縮。

電路的整體結構

基于ADPCM算法,可將語音編解碼VLSI芯片分成編碼、解碼、存儲、控制和時鐘幾個模塊。編碼模塊實現數據壓縮功能,將輸入的PCM信號轉換成ADPCM碼;存儲模塊在控制模塊的作用下,保存編碼所得的ADPCM碼;解碼模塊實現解壓縮功能,將ADPCM碼轉換得到PCM碼;控制模塊的作用是控制其他模塊的協調工作;時鐘模塊主要實現對外部晶振的原始時鐘信號進行分頻,以得到電路系統實際所需的時鐘信號。

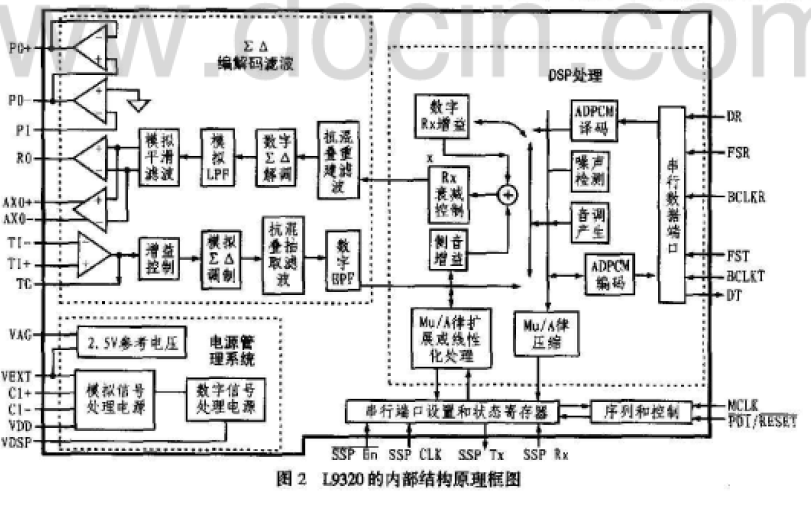

電路整體結構如圖2所示,其中En_en、En_de分別是編碼和解碼的使能信號,RST則為復位信號。當WE為“1”時,RAM寫有效,而當 WE為“0”時,RAM讀有效,CS為“1”時,RAM可進行寫或者讀操作。

(a) ADPCM編碼器

(b)ADPCM解碼器

圖1 ADPCM簡化框圖

電路設計過程

本文采用Top-down方法進行電路設計。主要設計流程如下:首先基于Verilog HDL運用Active-HDL進行電路的RTL級描述和功能仿真;將經過功能仿真正確的程序在Quartus II開發系統中進行綜合和適配;接下來將得到的網表文件(.vo)和具有時延信息的反標文件(.sdo)調入ModelSim SE中,并加入所選器件相應的器件庫進行時序仿真;時序仿真通過后,將Quartus II得到的“*.sof”文件通過JTAG配置模式下載到FPGA中進行不可掉電的實際測試,也可將“*.pof”文件通過AS配置模式下載到FPGA中進行可掉電的實際測試。電路系統的頂層程序如下。

圖2 電路整體結構圖

module ADPCM_TOP ( PCM_OUT,PCM_IN ,RECORD,PLAY,CLK, CLK8K);

parameter ADDR_WIDTH=14;

parameter PCM_WIDTH=8;

input [PCM_WIDTH-1:0] PCM_IN ;

wire [PCM_WIDTH-1:0] PCM_IN ;

output [PCM_WIDTH-1:0] PCM_OUT ;

wire [PCM_WIDTH-1:0] PCM_OUT ;

input CLK, RECORD,PLAY;

output CLK8K;

wire [3:0] code_in,code_out;

wire en_encoder,en_decoder,re_rst,pl_rst,WE,CS,CLK_8K;

wire [ADDR_WIDTH-1:0] ADDRESS;

assign CLK8K =CLK_8K;

CLOCK_GE U0 (CLK,RECORD, CLK_8K);

encoder_new U1 ( PCM_IN,re_rst ,en_encoder, CLK_8K ,code_in );

RAM U2 (ADDRESS,WE,CS,CLK_8K,code_in,code_out);

decoder_new U3 (pl_rst, CLK_8K ,code_out ,en_decoder,PCM_OUT);

controllogic U4 (CS,re_rst,pl_rst,en_encoder,en_decoder,WE,ADDRESS,RECORD,PLAY,CLK_8K);

endmodule

子模塊電路設計及仿真

整個語音編解碼VLSI芯片包括編碼電路、解碼電路、存儲電路、控制電路和時鐘電路幾個部分。下面分別具體描述關鍵電路的設計。

1 編碼電路

編碼電路實現數據壓縮功能,將輸入的PCM信號轉換成均勻的PCM碼,然后與預測信號進行差分,得到的差分信號經過“自適應量化器”進行壓縮編碼得到ADPCM碼,ADPCM碼被返回經過“逆自適應量化器”以及“自適應預測器”用來構建下一個預測信號。編碼電路仿真波形如圖3所示,其中PCM_IN為編碼器輸入信號(PCM碼),CODE為編碼后得到的輸出信號(ADPCM碼)。

圖3 編碼電路仿真波形

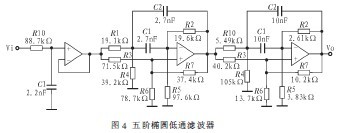

2 解碼電路

解碼電路實現解壓縮功能,將ADPCM碼經過“逆自適應量化器”得到量化差分信號,量化差分信號與預測值相加得到重構信號,然后轉換成PCM碼。解碼電路仿真波形如圖4所示,其中CODE為解碼器輸入信號(ADPCM碼),PCM_OUT為解碼后得到的輸出信號(PCM碼)。與圖3中編解碼前的PCM_IN對比,可以看出解碼誤差很小。

3 其他模塊

控制電路控制其他電路模塊的協調工作,在編碼的同時使能存儲器寫入信號,使編碼電路輸出數據可以及時存入存儲器;在解碼的同時使能存儲器讀出信號,編碼和解碼不能同時進行。時鐘電路主要實現對外部晶振的原始時鐘信號進行分頻,以得到電路系統實際所需的時鐘信號。本系統采用的外部晶振固有頻率為14.318MHz,經過分頻后可以獲得8kHz時鐘。存儲電路在控制電路的作用下,保存編碼所得的ADPCM碼(32kb/s),由于只需驗證電路的功能,所以只設定了2s的錄音存儲空間,即64kb存儲容量。

整體電路仿真

在子模塊電路仿真正確后,對系統整體進行仿真,可以得到圖5所示波形。此次仿真輸入信號PCM_IN激勵采用Testbench產生。在編碼使能信號RECORD為“0”時,開始編碼,RECORD跳變到“1”時,編碼被屏蔽;此時解碼使能信號PLAY為“0”,開始解碼,PLAY跳變到“1”時,解碼被屏蔽。從圖中可以看出編碼前輸入信號PCM_IN的激勵和解碼后輸出PCM_OUT的響應基本符合。由于ADPCM算法本身是有損壓縮,可以確定本電路系統的設計是正確可靠的。

FPGA驗證及結論

本文基于FPGA驗證所設計的電路。這里選用Altera公司Cyclone系列的EP1C6Q240C8器件,其內部有90kb的存儲容量,6k個邏輯單元,2 個PLL。由于電路采用8kHz采樣頻率,編碼后的ADPCM碼為4位,設定錄音時間為2s,所以需要64kb存儲容量;同時,設計需要大約400個左右的邏輯單元。所以選用此低成本的FPGA即可滿足設計要求,而且基本上充分利用了內部資源。此芯片的引腳有240 個,能滿足外面的引腳連接,而且價格也易于接受。

FPGA驗證表明:電路的最大時鐘延遲為26.903ns,最高工作頻率可達37.17MHz,可以很好地再現被錄入的語音,具有較高的保真度和很好的實時性。在電子地圖、車載信息終端語音播報、治安報警系統,特別是便攜式語音記錄裝置等方面具有較高的應用價值。同時,也指明了數字語音壓縮處理高效設計方法的方向。

圖4 編碼電路仿真波形

圖5 系統仿真波形

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601883 -

解碼器

+關注

關注

9文章

1131瀏覽量

40679 -

存儲

+關注

關注

13文章

4265瀏覽量

85675

發布評論請先 登錄

相關推薦

語音和音頻統一編解碼算法研究

振南對ADPCM音頻編解碼原理的一些通俗闡述【附振南的ADPCM解碼原代碼】

如何采用FPGA實現汽車智能語音報警系統設計?

基于DSP Builder的ADPCM算法實現

G.726語音編解碼器在SoPC中的實現

G.726語音編解碼器在SoPC中的實現

基于ADPCM算法的語音報警系統

基于AMR語音編解碼算法的VoIP系統

ADPCM語音編解碼VLSI芯片的設計方法

基于FPGA驗證所設計的ADPCM算法語音編解碼電路

基于FPGA驗證所設計的ADPCM算法語音編解碼電路

評論