在每秒10千兆位系統迅速發展之前,亞皮秒均方根抖動一直是高速網絡和無線通信應用程序之超低抖動時鐘的黃金標準。然而,隨著下一代數據傳輸率遠遠超出每秒10千兆位,最嚴格的行業要求中,對于抖動性能更為嚴格的要求并不罕見。如圖1所示,下一代數據傳輸率正在經歷迅速發展,至高達每秒100千兆位。對于這些領先的邊緣應用程序,飛秒級時鐘抖動是為了達到目標BER(誤碼率)水平的絕對要求。本文將主要討論下一代超低抖動時鐘解決方案和本行業最先進和高要求的網絡、存儲和計算架構的技術問題。

圖 1. 高速通信和網絡應用程序

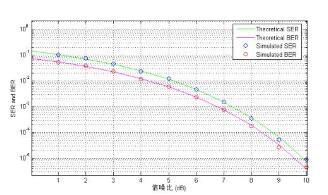

為了應對日益緊縮的時鐘抖動預算,麥瑞半導體(Micrel, Inc)已推出兩個全新系列的ClockWorks超低抖動時鐘合成器,能夠滿足這些精確計時要求。SM84xxxx標準時鐘合成器系列,以及ClockWorks Flex可編程時鐘系列的首臺新型合成器SM802xxx。SM802xxx系列提供了綜合硅定時解決方案,突破了關鍵性的100飛秒抖動障礙。如圖2所示,最新的ClockWorks時鐘合成器技術比目前市場上同類產品具有4倍以上的更佳抖動性能。這種領先的性能優勢具有比目前的設計大得多的抖動裕度,其“不會過時的”內部結構可為向下一代設計無縫升級提供極好的抖動裕度。

圖 2. 麥瑞半導體ClockWorks? 對比與之競爭的時鐘合成器技術。

除了固有的低時鐘抖動之外,在系統資格認證階段常常導致嚴重障礙、卻經常被忽視的性能參數是電源抑制比 (Power Supply Ripple Rejection, PSRR)。時鐘合成器或其它參考時鐘生成器單是能夠在實驗臺評估板上提供飛秒抖動水平還不夠,當嵌入現實系統應用程序時,解決方案還必須維持這種高水平的性能。這就是說,精心設計的時鐘合成器解決方案必須能夠在嘈雜的生產電源條件下發揮作用,而非精確的線性實驗室級別電源。在許多情況下,這涉及使用將電源并行分配給裝滿嘈雜數字裝置機箱的高電流開關式電源,而此等裝置不斷在各種頻率之間變換。超低抖動時鐘合成器的 ClockWorks? 系列的設計,包括從最基本的至可提供非同尋常的電源抑制比。表 1 概述了 ClockWorks? 部件的現實測試與主要競爭對手之插腳兼容設備的比較。

表1. 現實界 10 千兆位以太網測試案例結果。

在該測試案例中,使用現成 10 千兆位以太網 PHY 的 10 千兆位以太網線路卡,設計成使用 ClockWorks? 部件和競爭對手的插腳兼容時鐘合成器。作為基準,使用專門的時鐘評估板和線性實驗室電源在實驗室對兩種時鐘合成器設備進行了測量。

結果顯示,競爭對手的設備綜合時鐘抖動為 850fs (rms 12kHz – 20MHz),而ClockWorks? 部件的抖動不到四分之一,即綜合抖動為 225fs。然而,現實測試是在時鐘合成器置于線路卡,且插入完全填充的10 千兆位以太網交換機機箱時進行的。在這種現實世界使用條件下,競爭對手的部件產生 3031fs,將近基準抖動值的四倍,超過 10 千兆位以太網 PHY 最大輸入時鐘抖動要求 3 倍以上。由于其出色的電源電源抑制性能,在相同條件下,ClockWorks? 部件僅產生 751fs,很容易滿足 10 千兆位以太網 PHY 輸入時鐘抖動要求,且可節約合理的裕度。這讓生產設備能夠具有重要的抖動裕度,從而使系統資格認證更容易。此外,由于使用ClockWorks? 時鐘生成技術執行時,時鐘樹無需廣泛的補充電源調整組件,因此可節約總成本。

作為更好地表征 PSRR 的新舉措的一部分,麥瑞半導體引進了一種新的測試程序,將 -8dBm 的寬帶白噪聲 (100Hz – 100MHz) 強加在電源上。通過產生噪聲層的整體上升,這種測試方法可在現實系統中更準確地模擬電源噪聲,同時創建一個可允許在高度非線性電路中混合各種頻率組件的多頻、豐富的噪聲環境。表2 概述了ClockWorks? 時鐘合成器技術的測試與業界標準 SAW 振蕩器設備的比較。

表2. ClockWorks? PSRR 與 SAW 振蕩器比較

在高度非線性電路中混合各種頻率組件的多頻、豐富的噪聲環境。表2 概述了ClockWorks? 時鐘合成器技術的測試與業界標準 SAW 振蕩器設備的比較。

表 2 的結果顯示,ClockWorks? 時鐘合成器基線抖動的性能比 SAW 振蕩器好 1.7倍以上。然而,更重要的是,在現實界系統應用程序中常見的典型條件,即有噪聲的電源環境中,ClockWorks? 時鐘合成器的性能比業界標準的 SAW 振蕩器好 1.6倍。由于完整時鐘樹解決方案擁有更加簡約高效的 BOM,因此系統資格認證將更加順利,并節省系統總成本與電路板空間,這些增加的受益將有望提高系統抖動裕度。

麥瑞半導體的最新 ClockWorks? SM84xxxx 和 SM802xxx 時鐘合成器系列代表了硅定時技術的一大飛躍,將真正的飛秒級抖動性能推向市場,將每秒 10 千兆位推進為每秒 100 千兆位及更高。在現實系統使用中證明了其穩固性可為現今的系統和電路板設計人員提供豐富的抖動裕度,同時為下一代系統及未來系統提供了時鐘樹無縫升級途徑。

-

以太網

+關注

關注

40文章

5385瀏覽量

171162 -

振蕩器

+關注

關注

28文章

3814瀏覽量

138912 -

時鐘合成器

+關注

關注

0文章

87瀏覽量

8328

發布評論請先 登錄

相關推薦

基于系統總誤碼率的協同伙伴選擇算法

具分配電路的超低抖動 2MHz 至 2700MHz 時鐘合成器

BER誤碼率 影響誤碼率的因素

誤碼率是指什么_誤碼率是怎么表示_怎么計算

能有效降低高速網絡誤碼率的超低抖動時鐘合成器

能有效降低高速網絡誤碼率的超低抖動時鐘合成器

評論