隨著電力電子技術的發展,對信號的要求越來越高。在某些場合,對于信號的頻率,相位以及失真度要求較高。高質量信號的合成顯得具有特殊的地位。"信號系統"課程中,周期連續信號的分解與合成是學習的難點。加深對理論知識的理解,提高學生實踐能力、創新能力以及理論聯系實際的能力,實驗是必不可少的。已知周期信號的數學表達式,按照傅立葉級數可以分解為無窮多個不同頻率不同振幅的正弦信號;反之,無窮多個不同頻率、不同振幅的正弦波可以合成各種周期信號。本系統利用一些常規的芯片設計了一系列電路,可以實現周期連續信號的分解與合成。本系統既可以幫助低年級的同學學習周期信號的分解與合成,又可以運用于實際,信號質量高,具有實用價值。

1 波形合成器設計方案

1.1 該系統的基本原理

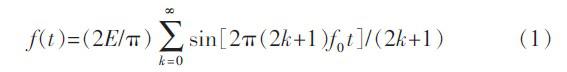

任何周期信號只要滿足狄利克雷條件就可以分解成直流分量及許多正弦、余弦分量。這些正弦、余弦分量的頻率必定是基頻的整數倍。根據函數的對稱性與傅里葉系數的關系知,周期對稱方波信號可以用無窮個奇次諧波分量的傅里葉級數來表示:

周期對稱三角波可以用無窮個奇次諧波分量的傅里葉級數來表示:

在本系統中只用取出前兩項奇次諧波,然后合成即可得到近似方波、三角波。

1.2 方波振蕩電路

采用模擬分立元件或單片壓控函數發生器以及FPGA都可以產生方波,但是采用模擬器件由于元件分散性太大,參數也與外接部件有關,外接電阻電容對參數影響太大,影響系統的穩定性,故本系統用FPGA產生方波。FPGA系統板上有晶振,可以產生高精度高穩定度的基準頻率。利用鎮相環可以輸出頻率穩定的信號源,如果對輸出信號再進行分頻就可以得到步進頻率較細的頻率源。分頻的方法可以使用鎖相環來實現。操作方便,輸出信號穩定性好,可以產生頻率為晶振的約數的任意頻率。

1.3 移相網絡

移相是指對于兩路同頻信號,以其中一路為參考信號,另一路信號相對于該參考信號做超前或滯后的移相形成相位差。主要有數字移相法和RC移相兩種。數字移相法通常采用延時的方法,以延時的長短來決定兩路數字信號間的相位差。數字移相法移相量可以很大,但是在一個周期內采樣點數較多,對AD和RAM的速度要求很高。用RC組成移相網絡進行移相,由于回路呈容性,信號經過該網絡后,相位發生變化。由于該方案簡單,很方便實現-45°到+45°移相,足以滿足需求,所以本系統采用了RC移相法。

1.4 濾波電路設計

濾波電路用八階低通橢圓開關電容濾波器,橢圓濾波器相比其他類型的濾波器,在階數相同的條件下有著最小的通帶和阻帶波動。巴特沃茲濾波器的幅度函數是單調下降的,但巴特沃茲濾波器能實現最大平坦幅度濾波;切比雪夫低通濾波器的幅度響應在通帶內是在兩個值之間波動,在通帶內的波動次數取決予濾波器的階數。為進一步減小高次諧波對有用信號的影響并保證通頻帶內最大平坦幅度濾波,在開關電容濾波器后加上巴特沃斯低通濾波器。

1.5 五選一通道選擇

模擬開關和繼電器都可以控制通道的選擇。模擬開關的作用就是用在模擬信號的傳輸路徑切換電路中,開關在電路中起接通信號和斷開信號的作用。最常見的可控開關是繼電器,當驅動繼電器的電路加高電平或低電平時,繼電器就吸合或釋放,其觸點接通或斷井電路。CMOS模擬開關是半導體器件,它不像繼電器那樣可以用在大電流、大電壓的場合,當輸入信號過低或者過高時,MOSFET處于反向偏量,當電壓達到一定值時(超過限制0.3 V),開關無法正常工作,因此模擬開關只適用于處理幅度不超過其工作電壓、電流較小的模擬或數字信號。模擬開關的導通電阻隨輸入信號的變化而變化,對信號有一定的影響。繼電器壽命高、靈敏度高、轉換速度快、電磁干擾小,故本系統使用繼電器進行通道切換。

1.6 檢波方案的設計

常見的檢波方法主要有兩種:峰值檢波和有效值檢波。基本的峰值檢波電路由二極管電路和電壓跟隨器組成,當輸入電壓正半周導通時,檢波管導通,對電容充電。選擇適當的電容值,使得電容充電速度大于放電速度,這樣電容兩端的電壓可以保持在最大電壓處從而實現峰值檢波。峰值檢波能檢測的信號頻率范圈很寬,被檢測信號頻率低時檢波的紋波較大,且二極管是非線性元件,當交流電壓較小時,檢測的直流電壓偏離其峰值較多。而采用有效值檢波不僅可以直接測得各種波形的真實有效值,而且測量精度高。

2 系統整體方案設計

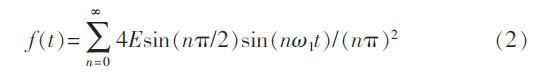

本系統用FPGA產生方波,分頻后用八階橢圓低通開關電容濾波器MAX297初步濾波,然后用三階低通巴特沃斯濾波器進一步濾波。分頻濾波后即可得到10 kHz、30 kHz、50 kHz的正弦波。可通過按鍵選擇波形和合成階數。通過RC移相網絡使得信號產生確定的相位差,根據方波三角波各次諧波組成關系,把各次諧波疊加,即可得到近似方波和三角波。各次諧波信號依次經過峰值檢波電路處理后送入單片機,單片機對分頻濾波后的信號采樣,經過一系列處理后,將峰值用LCD顯示。系統框圖如1所示。

圖1 系統框圖

3 系統硬件電路設計

3.1 整個系統中電源的去耦問題

在整個系統中會用到很多的運算放大器芯片。一般來說,運算放大器的供電電源端應連接去耦電容(對交流放大器尤其需要),以消除信號電流通過電源內阻給電路帶來的影響。運算放大器的性能不同,其去耦電容的容量也有所不同。對于低速運算放大器,一般在緊靠運放供電端與電源地之間接容量為0.1μF的電容就可以了,但是對于高速運算放大器,應當在緊靠運放的供電端與電源地之間用容量為10μF和容量為0.01μF的電容器并聯連接。整個系統中所有的運算放大器都做了去耦處理,只是畫圖中為簡單起見,省略了去耦電容。

除此之外,運算放大器的地線連接也有講究,對于小功率運放而言,地線連接無特殊要求,但對于較大功率的運算放大器,地線連接相當重要。總的原則是地線應短而粗并且在同一點連接。本系統中數字地模擬地共存,因此設計時將所有模擬地和數字地分別連接,最后電路中的模擬地和數字地與電源地一點匯集。

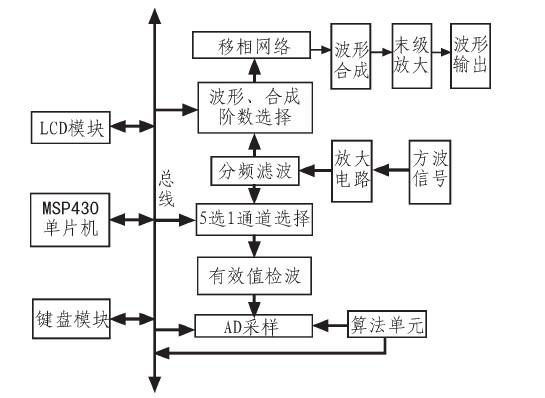

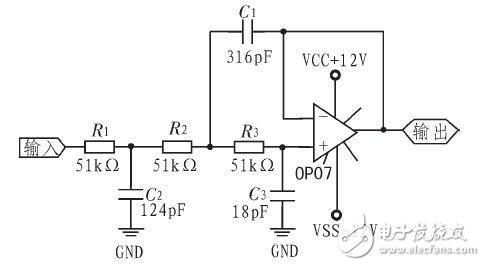

3.2 濾波電路

圖2、圖3中兩個低通濾波器都是三階巴特沃斯低通濾波器。有源濾波器適應在低頻段(<100 kHz)的濾波,當頻率較低時,若用無源濾波,電容、電感的元件值及體積都會很大,大電容電感不易獲得,且誤差較大,而有源濾波器則可以依靠運放在低頻段的諸多優勢(尤其是低噪聲運放)達到很好的濾波效果。10 kHz、30 kHz、50 kHz信號經八階橢圓開關電容濾波器濾波后,10 kHz、30 kHz、50 kHz信號再分別用理論截止頻率為20kHz、35 kHz、55 kHz的低通濾波器濾波,理論值與實際截止頻率有一定的偏差,為防止有用信號落在通頻帶之外,理論截止頻率沒有按照嚴格的10kHz和30kHz。

圖2 20kHz低通濾波器

圖3 35kHz低通濾波器

3.3 移相電路

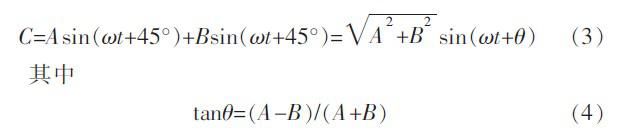

RC移相網絡參數的計算:

要求疊加后的信號移相范圍為-45°~+45°,設A信號為Asin(ωt+45°),B信號為Bsin(ωt+45°),疊加后的信號為

改變A和B的值就可以改變疊加后信號的相位。

只有輸入信號的頻率與RC網絡的諧振頻率相同時,才會有45°的相移,因此隨著輸入信號頻率的變化,RC網絡的諧振頻率也要相應的改變。根據公式

f=1/2πRC (5)

推導可得R值,取電容C為0.1μF,當輸入信號的頻率為100Hz時,R=16kΩ,當頻率為1kHz時,R=1.6kΩ,當頻率變為10kHz時,R=160Ω。

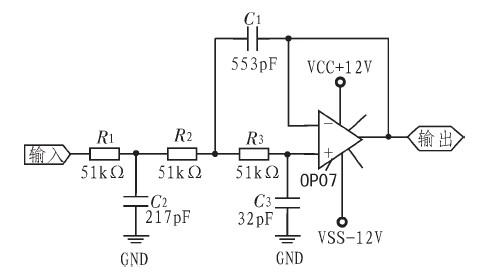

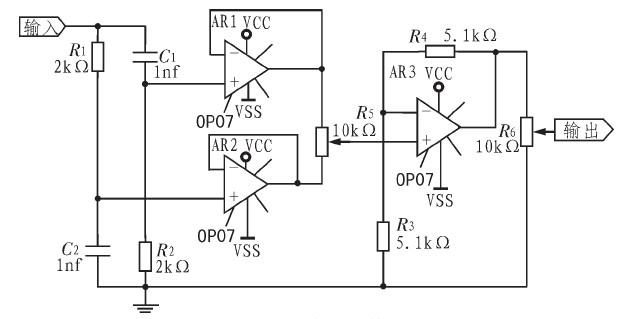

輸入的正弦信號經過RC構成的超前和滯后網絡后經過運放(OPA37)構成的射極跟隨器,然后通過電位器R3疊加,再經過放大電路通過一個電位器輸出。電路圖如圖4所示。

圖4 移相網絡

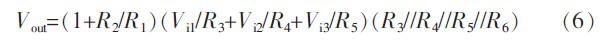

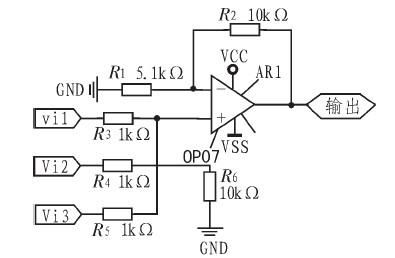

3.4 加法器

此加法器為同相加法器,由于集成運放可視為理想運放,其輸入端可視為虛短和虛開路。在同向端運用節點電流方程可求得輸出:

圖5 加法器

3.5 有效值檢波

有效值檢波采用真有效值/直流轉換芯片AD637能計算任何復雜波形的真有效值、平均值、均方值、絕對值,具有分貝輸出(0~60 dB)。具有寬頻帶,量程在0~7 V范圍內可調。

AD637內部結構包括有源整流器(即絕對值電路),平方/除法器、濾波放大器、獨立的緩沖放大器、偏置電路五部分。使用AD637在測量峰值系數高達10的信號時附加誤差僅為1%,且外圍元件少、頻帶寬。對于有效值為200 mV的信號,-3dB帶寬為600kHz;對于有效值為1V的信號。-3dB帶寬為8MHz.該方案硬件簡單,兩且精度很高,效果理想。

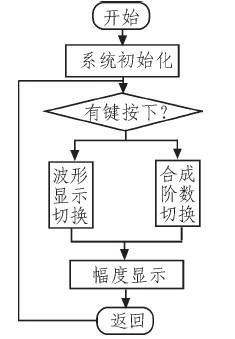

4 系統軟件設計

軟件流程圖見圖6,本系統選用MSP430F449單片機,主要負責對方波、三角波10k、30k、50k等各次諧波連行采樣,并用LCD12864對各次諧波的峰值顯示;在程序運行的過程中,可通過16x16矩陣鍵盤控制選擇波形及階數的切換。

圖6 軟件流程圖

5 結束語

系統實現了對三角信號、方波信號的合成。從方波信號中經分濾波獲得了10kHz、30kHz、50kHz的正弦信號,信號波形比較好,無明顯失真,同謀峰峰值達到要求。最終合成的方波、三角波比較好,接近方波、三角波。從總體上看,系統的性能很好。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601850 -

芯片

+關注

關注

453文章

50406瀏覽量

421830 -

ARM

+關注

關注

134文章

9046瀏覽量

366817

發布評論請先 登錄

相關推薦

使用MSP430F522x和MSP430F521x器件進行設計

從MSP430F541x和MSP430F543x遷移到MSP430F541xA和MSP430F543xA

MSP430F67xx和MSP430F67-xxA器件之間的差異

組合兩個 LMX2820 合成器輸出,以改善相位噪聲應用說明

功分器能否作為功率合成器使用

單節功率合成器工作原理是什么

MSP430F677x、MSP430F676x、MSP430F674x多相位計量SoC數據表

MSP430F677xA、MSP430F676xA、MSP430F674xA多相儀表計量片上系統(SoC)數據表

MSP430F677x1、MSP430F676x1、MSP430F674x1多相位計量SoC數據表

鎖相環頻率合成器的特點和應用

MSP430F665x、MSP430F645x、MSP430F565x、MSP430F535x混合信號微控制器數據表

MSP430F15x, MSP430F16x, MSP430F161x混合信號微控制器數據表

MSP430F14x、MSP430F14x1、MSP430F13x混合信號微控制器數據表

以MSP430F499為核心的波形合成器設計方案

以MSP430F499為核心的波形合成器設計方案

評論