引言

模擬電路中廣泛地包含電壓基準(reference voltage)和電流基準(current reference)。在數/模轉換器、模/數轉換器等電路中,基準電壓的精度直接決定著這些電路的性能。這種基準應該與電源和工藝參數的關系很小,但是與溫度的關系是確定的。在大多數應用中,所要求的溫度關系通常分為與絕對溫度成正比(PTAT)和與溫度無關2種。

近年來有研究指出,當漏電流保持不變時,工作在弱反型區晶體管的柵源電壓隨著溫度升高而在一定范圍內近似線性降低。基于該特性,帶隙基準源所采用的基極-發射極結可以被工作在弱反型區的晶體管代替產生低溫度系數的基準源。文獻中提到采用該設計原理的基準源,利用0.13μm工藝的低閾值電壓NMOS管和襯底調整的PMOS管實現其中的放大器。本文所采用的基準源電路利用傳統帶隙基準源的核心電路原理,通過飽和狀態MOS等效電阻對PTAT電流動態反饋補償,基本實現了基準源的穩定要求。

1 帶隙基準源的基本原理

帶隙基準源可以在0~70℃的溫度范圍內有lO ppm/℃的溫度系數。由室溫下溫度系數為-2.2 mV/℃的PN結二極管產生電壓為VBE。同時也產生一個熱電壓VT(VT=kT/q),其與絕對溫度(PTAT)成正比,室溫下的溫度系數為0.085 mV/℃,則輸出電壓為:

將式(1)對溫度求導,用VBE和VT的溫度系數求出理論上不依賴于溫度的K值。為了達到所希望的性能,更詳細地分析VBE與溫度的關系是必須的。帶隙基準就是將負溫度系數的電壓與正溫度系數的電壓加權相加來抵消溫度對輸出電壓的影響。

1.1 負溫度系數電壓的產生

雙極晶體管的基極-發射極電壓具有負溫度系數,或者說PN結二極管的正向電壓具有負溫度系數。從文獻可得到與溫度的關系式:

式中:η為與三極管結構有關的量,其值大約為4;α為與流過三極管的電流有關的一個量,當PTAT電流流過三極管時α為1,當與溫度不相關的電流流過三極管時為0;T0為參考溫度;VBG為硅的帶隙電壓。由式(1)可以看出VBE是一個具有負溫度系數的電壓。

1.2 正溫度系數電壓的產生

兩個三極管工作在不同的電流密度下,它們的基極-發射極電壓的差值與絕對溫度成正比。如果兩個同樣的三極管(IS1=IS2),偏置的集電極電流分別為nI0和I0,并忽略他們的基極電流,那么:

式中:△VBE表現出正溫度系數,而且此溫度系數是與溫度無關的常量。

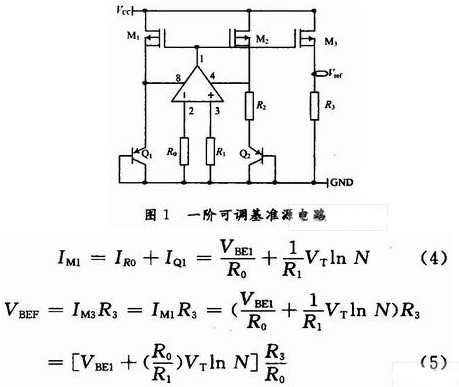

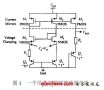

1.3 一階溫度補償帶隙基準源

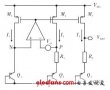

將正、負溫度系數的電壓加權相加,就可以得到一個近似與溫度無關的基準電壓。常見的一階可調基準源電路如圖1所示。

式中:N為Q2與Q1的發射結面積之比,式(4)中第一項具有負的溫度系數,第二項具有正、負溫度系數,合理設計R0與R1的比值和N的值,就可以得到在某一溫度下的零溫度系數的一階基準電壓。式(5)中方括號內是約為1.25 V的一階溫度無關基準電壓,通過調節R2/R0的比值,可以得到不同大小的基準電壓。

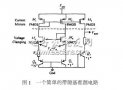

2 電路結構及原理分析

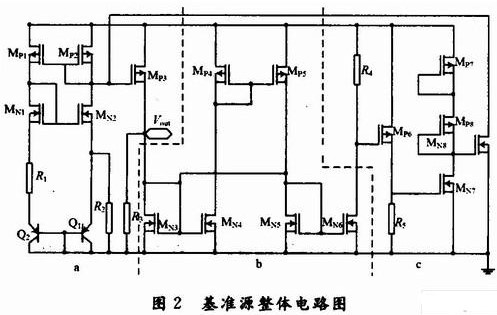

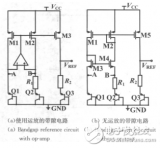

圖2為本文設計的基準源整體電路圖,包含帶隙核心電路、反饋補償電路和啟動電路。其中虛框a為帶隙核心電路,虛框b為偏置及反饋補償電路,虛框c為基準源啟動電路。

2.1 帶隙核心電路

圖2中,由Mp1~Mp3,MN1,MN2,R1,R2和Q1,Q2組成的電路構成帶隙核心電路。輸入晶體管的偏置電流由PMOS電流源提供,可通過減小其電流,而不是減小其寬長比來降低負載器件的gm,從而增加其差動放大增益。

其中Mp1,Mp2,MN1,MN2均工作在飽和狀態,Mp1,Mp2復制了Iout,從而確定了IREF。從本質上講,IREF被“自舉”到Iout。選擇一定的MOS管尺寸,如果忽略襯底溝長長度調制效應,則有Iout=KIREF,因為每個二極管連接的器件都是由一個電流源驅動的,故IREF和Iout與VDD無關,左右兩支路永遠維持這兩個電流值。雙極晶體管Q1和Q2工作在不同的電流密度下,它們的基極與發射極間的電壓差與絕對溫度成正比。將與電源無關的偏置電路與雙極晶體管結合,得到帶隙核心電路。

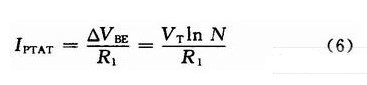

假設Mp1,Mp2和MN1,MN2均為相同的對管,將PTAT電流Ip3加到基極-發射極電壓上,因此輸出電流為:

PTAT基準電流IMp3PTAT(與絕對溫度成正比)通過R3產生輸出基準電壓。

2.2 自偏置電路及反饋補償電路

為了提高電源電壓抑制,該設計對核心電路和運放的電源電壓進行了調節,由MOS管的電流電壓特性可知,當VDS≥VG-VTH時器件工作在飽和區,有:

因為柵漏短接,故MN3,MN5一定處于飽和狀態,它們均可作為一個阻值由過驅動電壓控制的等效電阻,定義MN3和MN5的等效電阻分別為RN3和RN5,則可將MN3與R3視為并聯電阻Rx,如果Vout增大,則RN3減小,并聯電阻Rx減小,從而使PTAT基準電流通過MN3分流一部分;同樣原理適用于MN5和MN6,達到抑制補償輸出電壓,使基準源輸出電壓穩定。其中Mp4和Mp5為MN3提供偏置電流,但使用這種“自偏置電路”會帶來電路的啟動問題。

2.3 啟動電路

在基準源電路中需要啟動電路使得系統上電時電路能夠進入正常的工作狀態,而自偏置放大器電路往往也存在啟動問題。當電路處于非工作狀況時,放大器的輸入端電壓初始值為零,而輸出電壓由于寄生電容的存在可能位于一個比較高的電勢,當電源接通后不但放大器的偏置電路為截止狀態,而且基準源的核心電路也無法正常啟動。本文設計的啟動電路則可以同時滿足放大器和核心電路的啟動要求,它由Mp6~Mp8,MN7,MN8,R4,R5構成。

當電源接通后,啟動電路提供了放大器輸出端到地的通路,從而拉低了核心電路中Mp1~Mp3的柵極電勢,放大器的偏置電路開始工作,同時基準源的Mp1和Mp2支路中流過的電流也隨之增大,使得放大器的輸入端電勢上升,這樣放大器進入高增益工作區,帶動基準源電路開始正常工作。

電路剛啟動時,使Mp7和Mp8飽和,保證MN8柵極有足夠高的開啟電壓,當MN8導通時,一個小的導通電流流過運放,啟動帶隙電路。電路開啟后,虛框b部分電流鏡像電路將輸出電流進行鏡像,給啟動電路提供偏置,偏置電流使Mp6導通,從而MN7的柵極電壓升高,MN7導通,由于MN8的電阻很大,導致MN7漏極電壓很低,從而關斷MN8,使啟動電路(虛框c)兩端電壓降低而停止工作。

3 仿真結果與分析

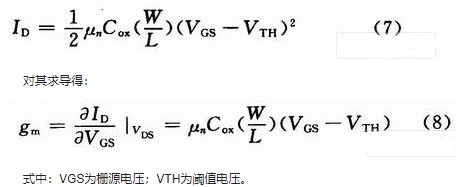

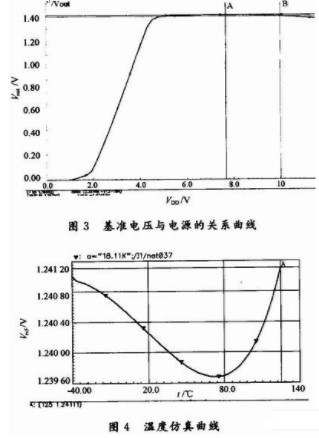

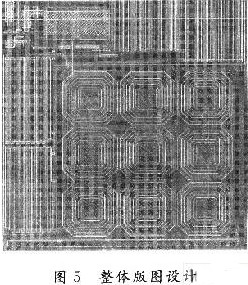

圖3說明了該基準源對電壓的抑制效果。根據仿真數據,在所取5~10 V的輸出電壓范圍經計算基準電壓電源抑制比為82 dB。圖4為Cade-nce下的溫度仿真曲線,根據所要求取的溫度范圍在-25~+120℃,計算得溫度系數為:TCF=7.427 ppm/℃。圖5為整體電路的版圖設計,面積近似為0.022 mm2。

4 結語

本文通過對傳統帶隙基準源的基本原理分析,設計的基準電路工作電壓為5~10 V,通過飽和狀態MOS等效電阻對PTAT電流反饋補償,得到了82 dB的電源電壓抑制比和低于7.427 ppm/℃的溫度系數,版圖面積0.022 mm2。該電路產生的基準源電壓基本滿足普通應用要求。

-

CMOS

+關注

關注

58文章

5689瀏覽量

235170 -

放大器

+關注

關注

143文章

13554瀏覽量

213144 -

模擬電路

+關注

關注

125文章

1555瀏覽量

102686

發布評論請先 登錄

相關推薦

基于CMOS工藝設計低溫漂高PSRR帶隙基準源

基于CMOS放大器實現帶隙基準源電路的設計

基于CMOS放大器實現帶隙基準源電路的設計

評論