現場可編程門陣列(FPGA)作為專用集成電路(ASIC)領域的一種半定制電路,可以根據設計的需要靈活實現各種接口或者總線的輸出,在設備端的通信產品中已得到越來越廣泛的使用。FPGA 是基于靜態隨機存儲器(SRAM) 結構的,斷電后程序丟失后的每次上電都需要重新加載程序。且隨著FPGA 規模的升級,加載程序的容量也越來越大,如Xilinx 公司的Spartan - 6 系列中的6SLX150T,其加載容量最大可以達到4.125 MB。

1 FPGA 常用配置方式

FPGA 的配置數據通常存放在系統中的存儲器件中,上電后控制器讀取存儲器中的bit 文件并加載到FPGA 中,配置方式有JTAG、從并、從串、主從4 種,不同廠家叫法不同,但實現方式基本都是一樣的。

(1)邊界掃描JTAG 方式。單板調試階段常用JTAG 模式,該方式需要控制器,FPGA 等芯片JTAG 接口構成菊花鏈,且在該模式下,控制器其他功能不能使用。

(2)從串方式。從串加載方式占用資源少,主要是和FPGA 相連的I/O接口較少,但是一個配置時鐘只能傳輸一個bit 數據,速度相對較低。

(3)主從方式。該方式最主要的缺點是配套使用的FLASH 存儲器必須是FPGA 廠家指定的型號,且這個FLASH 容量不大,不能和控制器的FLASH 共用,使用這種方式,單板上就會有兩個FLASH,增加產品成本,因此該方案使用較少。

(4)從并方式。即文章中探討的FPGA 加載方案。

2 從并加載方式的實現

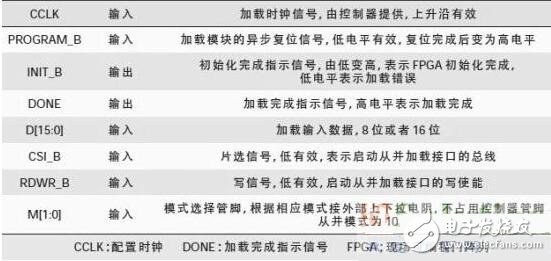

以Xilinx 公司Spartan - 6 系列FPGA 為例,與從并加載相關的管腳如表1 所示。

表1 從并加載管腳名稱

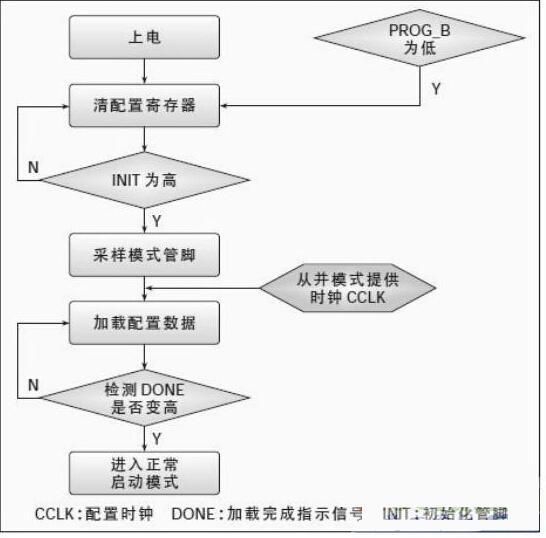

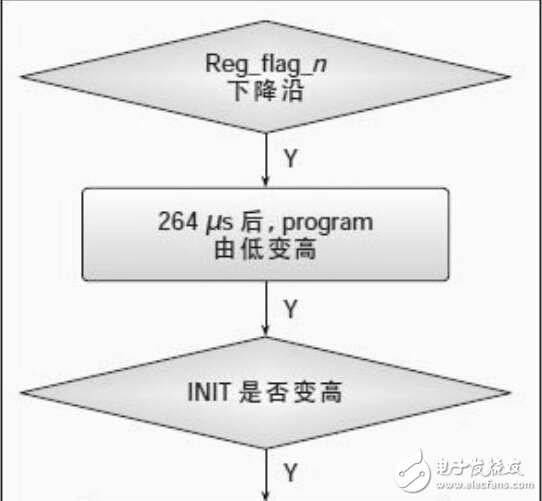

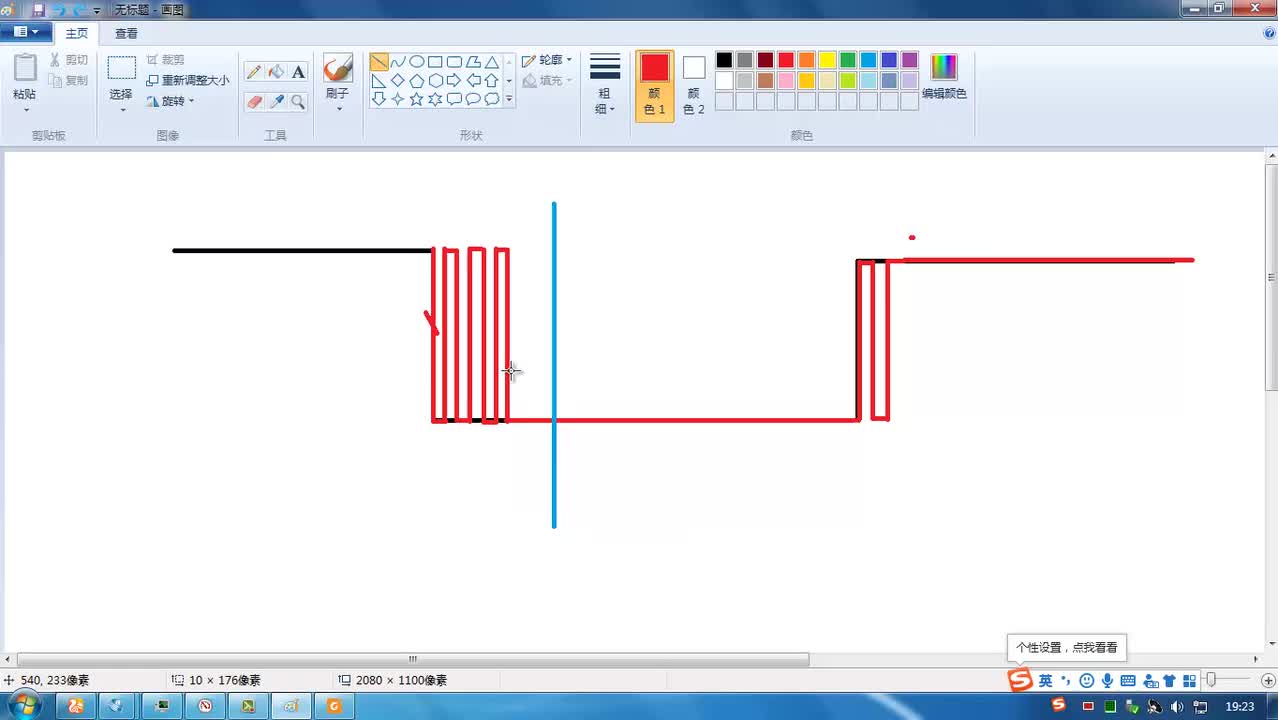

由表1 可以看出,從并加載接口占用的管腳資源是比較多的,即使加載數據總線使用8 位,也要14 個管腳,CPU 一般沒有這么多通用輸入/輸出(GPIO)口,因此從并加載一般和CPLD 配套使用。其加載流程如圖1所示。

圖1 SPARTAN-6 從并加載流程

3 基于CPLD 的FPGA 加載方案

3.1 方案介紹

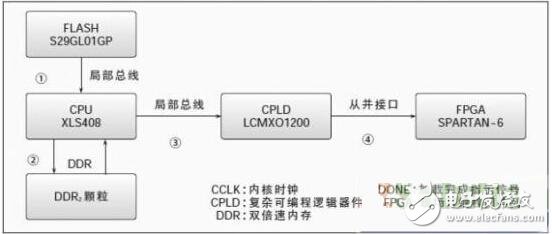

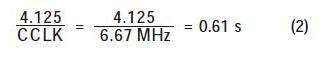

在 設備端通信產品中,基于CPLD 的FPGA 從并加載框如圖2 所示,配置數據存儲在FLASH 中,且在加載數據之前,CPU 通過局部總線和雙倍速內存(DDR)接口,將配置數據從FLASH 中搬移到DDR 顆粒;真正需要加載時,再通過DDR2 接口將配置數據搬移到CPU 的緩存中,DDR2接口速度很快,其時鐘頻率可以達到266 MHz,因此①、②兩步加載時間可以忽略不計。

圖2 基于CPLD 的FPGA 從并加載框

之 后CPU 通過和CPLD 的接口③——8 位的局部總線接口,將配置數據逐字節的寫入CPLD 的寄存器中。以MIPS 系列CPU XLS408 為例,XLS408 工作時鐘頻率為66.7 MHz,寫總線周期最快需要10 個工作時鐘周期,即6.67 MHz,這一步受局部總線速度限制。

數據寫入到CPLD 后,再通過接口④ ——CPLD 與FPGA 之間的從并接口,將數據加載到FPGA,從并接口是同步總線,加載時間受限于總線時鐘CCLK 頻率。

本方案的優點為:① 、② 兩條路徑可以在加載之前處理,且運行速度快,不占用加載時間。加載時間只受③ 、④ 的限制,而③ 受限于寫總線周期間隔,④受限于從并接口的時鐘。

3.2 程序實現

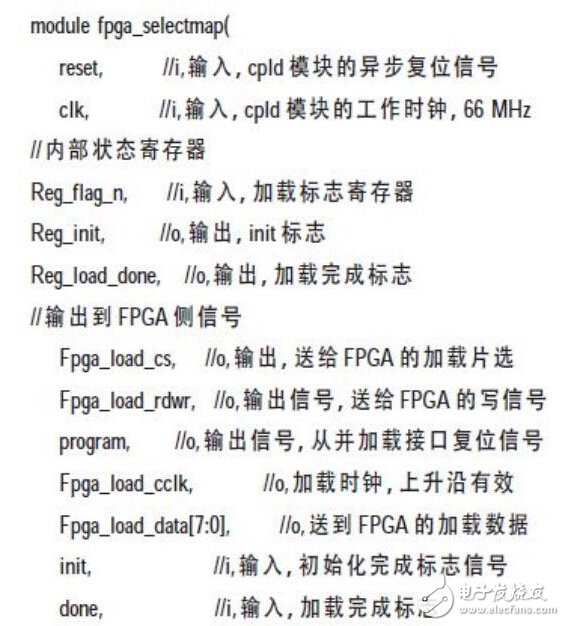

CPLD 從并程序采用verilog 語言實現,該加載模塊接口定義如下:

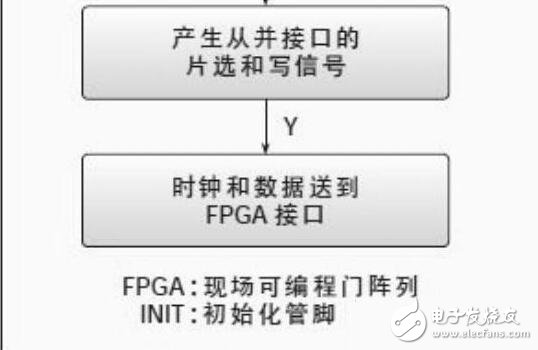

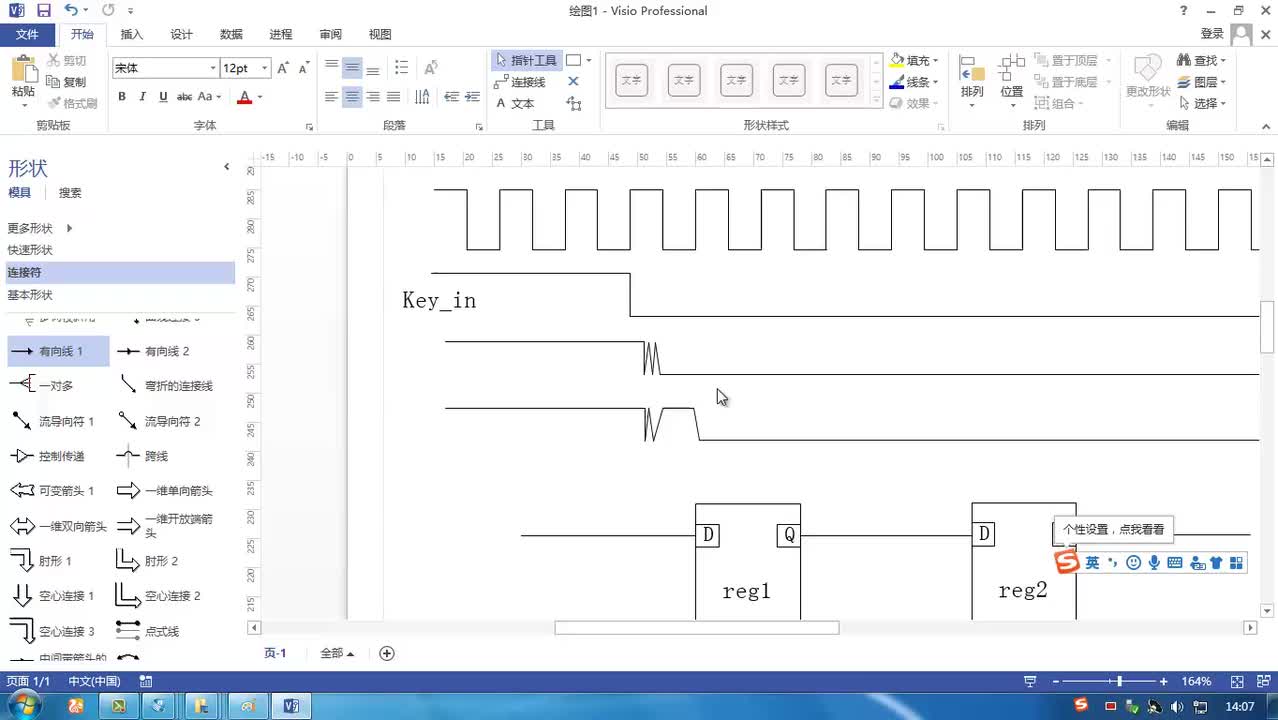

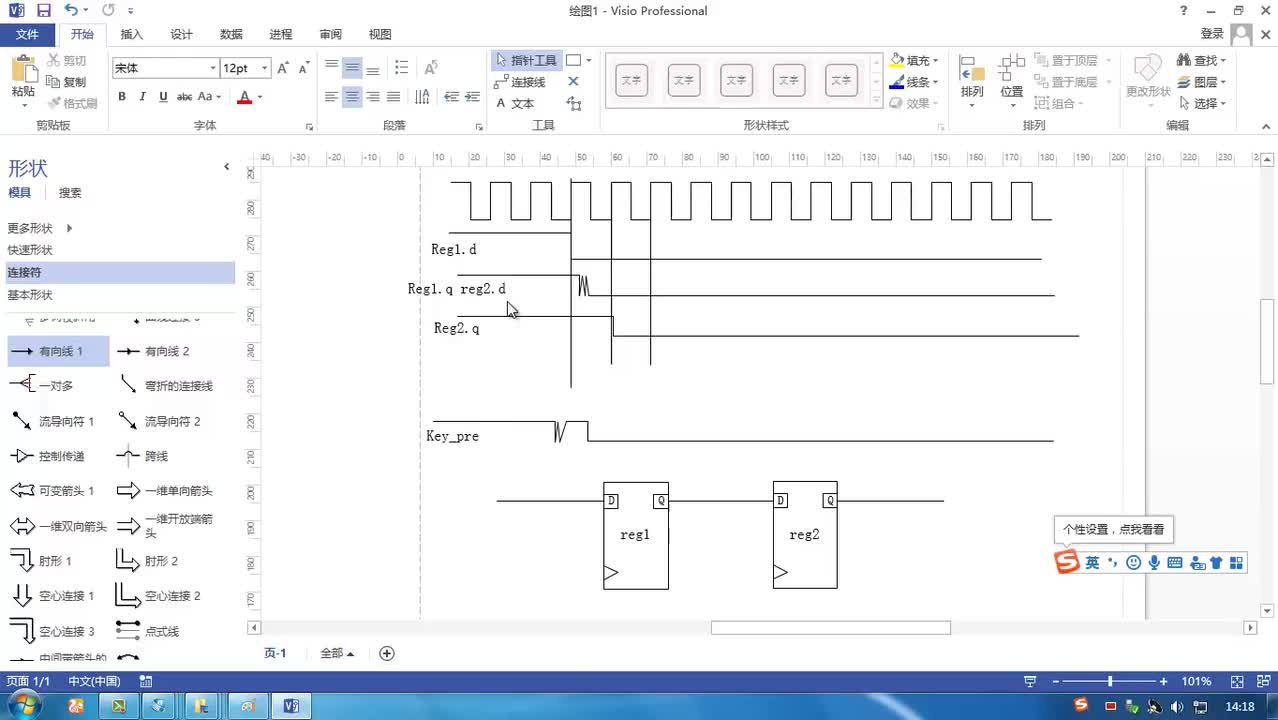

程序實現流如圖3 所示。

圖3 基于CPLD 從并加載FPGA的程序流程

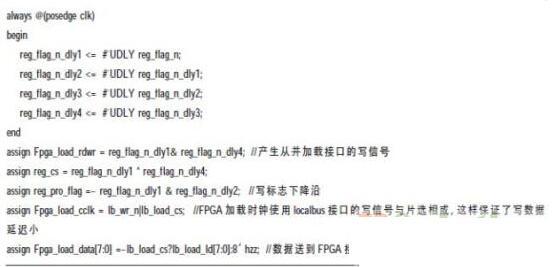

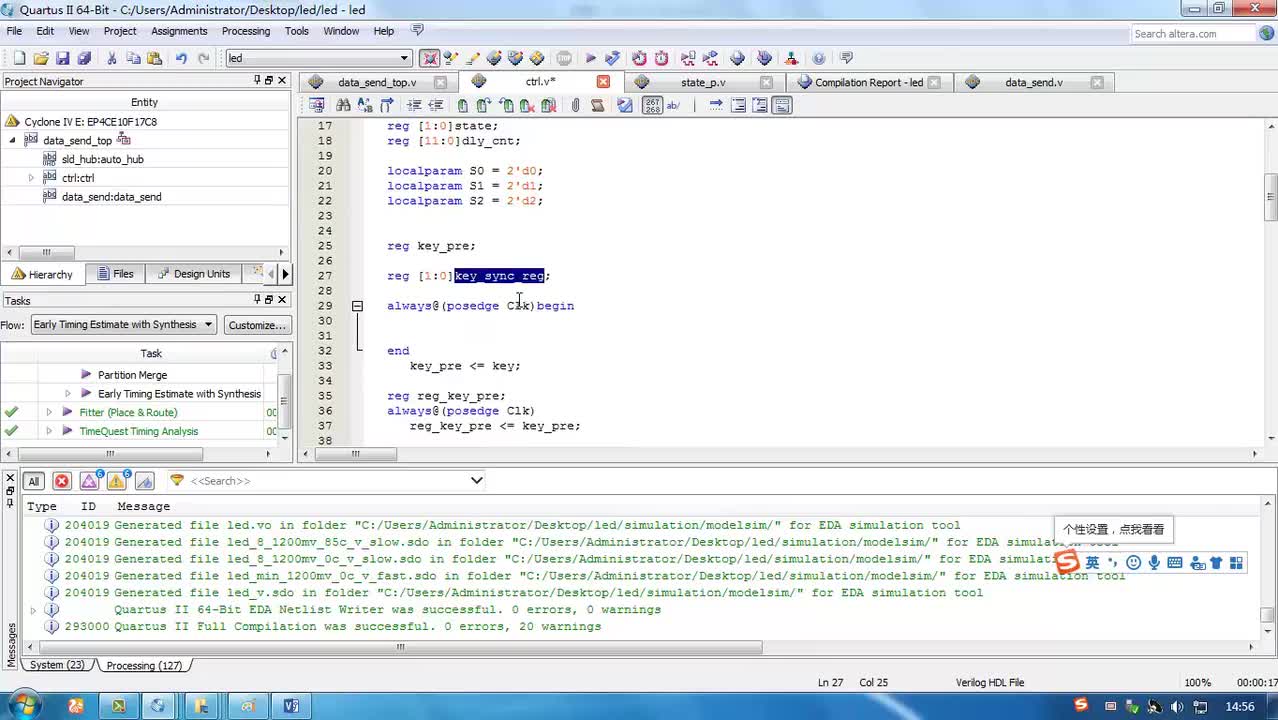

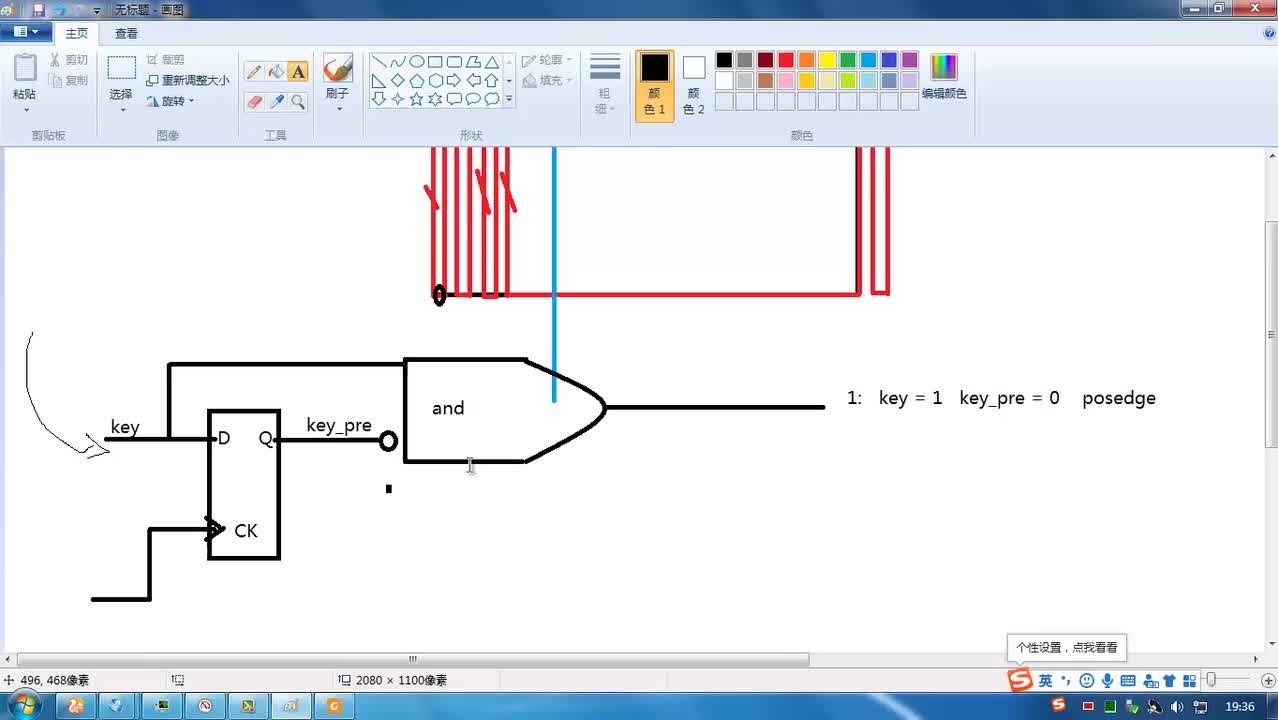

FPGA 加載片選和寫信號產生部分代碼如下:

4 仿真及加載結果分析

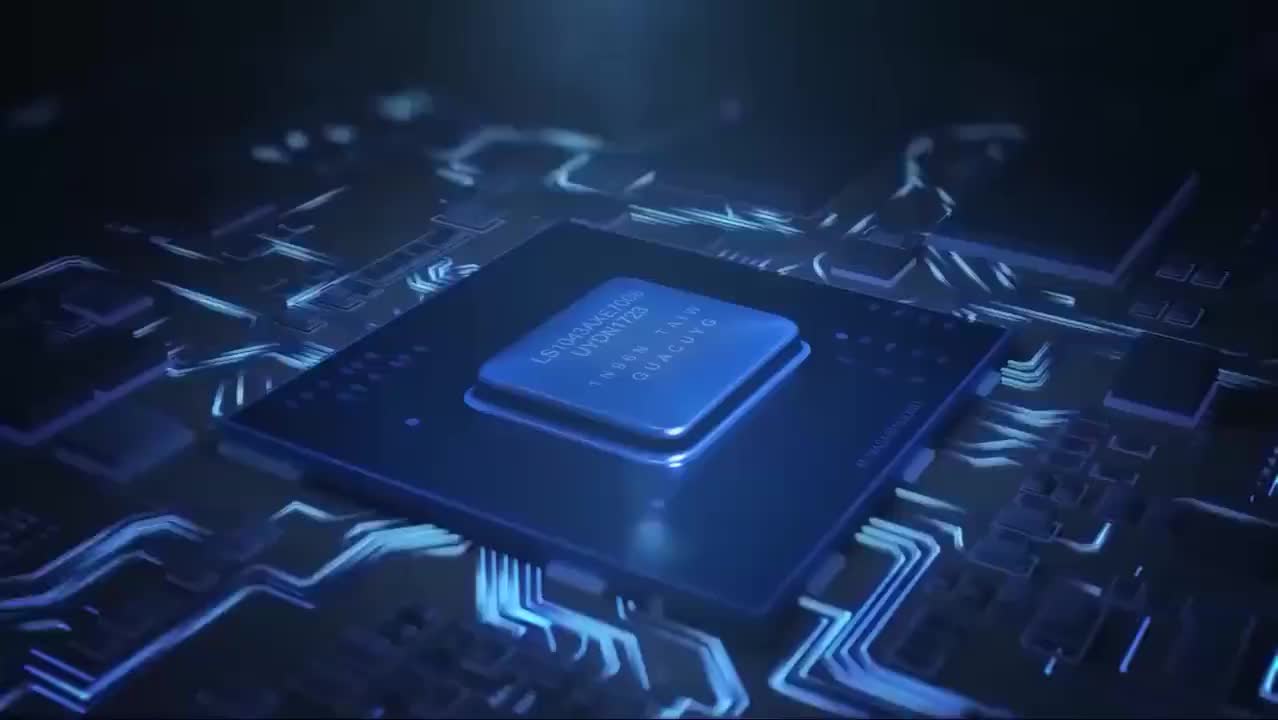

基于modelsim 6.5SE 仿真波形可以看出CPU 每加載1 字節數據需要向CPLD 寫1 次加載數據,這共需花費一個局部總線周期,局部總線頻率最快為6.67 MHz。因此CPU 加載4.125 MB 數據到CPLD 共需時間為:

CPLD 需要1 個CCLK 周期寫1 字節數據到 FPGA,CCLK 則是利用CPU局部總線的寫信號產生,可以實現CCLK 和數據的同步,因此CCLK 時鐘速率為6.67 MHz,因此加載4.125 MB數據到FPGA,共需時間為:

FPGA 上電需要1 ms,因此當FPGA 使用SPARTAN-6 系列最高端的6SLX150T 時,采用基于CPLD 的從并加載方式,共需要的加載時間為1.221 s,滿足通信產品FPGA 加載時間小于2 s 的要求。而如果采用從串等加載方式,使用ARM7 處理器作為控制器,對于CycloneII 系列中的EP2C35,配置文件大小1.16 MB,加載時間需要1.30 min;采用基于CPLD的從串加載方式,加載同樣4.125 MB的FPGA 數據,CPLD 加載時鐘33MHz,則加載時間需要3.8 s,FPGA加載時間過長,則會影響系統的啟動時間。

表2 是常用加載方式加載6SLX150T 型號FPGA 芯片數據所需時間比較。

表2 FPGA 加載時間對比

從上述分析可以得出結論,如果提高CPU 的局部總線寫速度,加載FPGA 的時間就會更快。

5 結束語

使用基于CPLD 的FPGA 從并加載方案,相對于其它幾種加載方式,雖然加載管腳增多,但加載時間大大縮短,并且如果提高CPU 局部總線的寫速度,加載速度有進一步提高空間,滿足通信系統快速啟動的要求,具有很高的實用價值。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601846 -

集成電路

+關注

關注

5381文章

11385瀏覽量

360871 -

cpld

+關注

關注

32文章

1247瀏覽量

169217

發布評論請先 登錄

相關推薦

基于CPLD的FPGA從并快速加載方案

FPGA從并加載解決方案的介紹

FPGA從并加載解決方案的介紹

評論