基于DSP方案

目前的視頻監控行業,基于DSP的H.264編碼器解決方案占有絕對優勢的市場份額,這是由DSP方案開發周期相對較短的特性決定的。在ASIC或FPGA方案仍處于研發階段時,DSP方案已捷足先登,并較好地解決了視頻監控行業中H.264編碼器方案從無到有的過程,為H.264在監控應用中走向成熟立下了汗馬功勞。但是由于DSP運算能力本身的制約,考慮到H.264標準實現的高復雜度,要達到未來對編碼器高性價比的要求,DSP方案會非常困難。為從低碼率的實時通信系統或無線環境到高碼率的HDTV和數字存儲系統提供一個優良的視頻壓縮編碼通用工具。但H.264標準優異的性能表現是以編碼運算復雜度和運算量大為代價,在通用的PC機平臺實現會占用較大的CPU和內存資源。隨著數字信號處理器(DSP)技術的高速發展,DSP的處理速度和能力飛速提高。同時,雖然DSP方案具有非常好的可編程性能,但由于其硬件接口和架構均已固定,很難滿足產品架構靈活性的要求,也相對增加了靈活提供對多通道編碼支持的實現難度。

基于ASIC方案

在目前階段基于ASIC的H.264編碼成熟方案在監控領域的應用還相對較少,這和芯片設計研發周期較長,成本較高的特點緊密相關。ASIC方案的最大優勢就是一旦量產后,成本和其他方案相比將非常低廉,同時由于是硬件編碼實現,通常可以較容易滿足行業對高編碼性能的要求。同時一款成熟的ASIC芯片和DSP實現方案相比通常具有更高的穩定性。監控市場相對多變的客戶需求則使得建立在ASIC平臺上的產品方案在未來有著更大的產品不確定性和市場風險。

基于FPGA方案

FPGA作為一個可編程的硬件邏輯實現平臺很好地融合了DSP架構的可編程可升級性和ASIC架構的由硬件實現方式而帶來的高編碼性能。FGPA方案的靈活性不僅僅體現在具有和DSP平臺一樣的可編程性和可升級性,而且還體現在可以提供更高的系統架構上的靈活性。以XilinxSpartan3系列芯片為例,首先提供了不同規格能力的芯片選擇,其次對于同一規格的芯片又提供了不同的封裝,以提供不同的管腳數目的選擇,同時,每一款FPGA芯片其管腳都可以根據用戶的要求重新定義功能,提供非常靈活的接口控制。通過和系統設計的有效配合,基于FPGA的方案有可能大幅降低產品的BOM成本。FPGA這種架構上的靈活性非常有利于采用同一個H.264編碼內核靈活支持不同應用、不同規格的產品方向。同時架構上的靈活性使得設計者可以充分發揮創造性,開發出個性化風格的產品,這是基于DSP或ASIC的方案難以做到的。

FPGA是現場編程門陣列器件。它和DSP集成在一塊芯片上,可實現寬帶信號處理,大大提高信號處理速度。據報道,Xilinx 公司的Virtex-II FPGA對快速傅立葉變換(FFT)的處理可提高30倍以上。它的芯片中有自由的FPGA可供編程。Xilinx公司開發出一種稱作Turbo卷積編譯碼器的高性能內核。設計者可以在FPGA中集成一個或多個Turbo內核,它支持多路大數據流,以滿足第三代(3G)WCDMA無線基站和手機的需要,同時大大WCDMA無線基站節省開發時間,使功能的增加或性能的改善非常容易。因此在無線通信、多媒體等領域將有廣泛應用。

FPGA方案與前兩種方案相比,其結合DSP方案和ASIC方案的部分優勢,彌補一些固有不足。如FGPA方案的可編程可升級性能大大降低了系統集成商在選用ASIC芯片方案時可能會遇到的一些后期風險,同時FPGA接近ASIC的強運算能力則有效彌補了DSP方案在編碼性能上的瓶頸。另一方面,FPGA類似于ASIC的實現方式也使得FPGA平臺有可能提供比DSP方案更高的產品穩定性。

FPGA方案從產品角度來考量的話,最主要的難度是如何既考慮到產品的成本需要,又考慮其性能需求,為市場提供高性價比的編碼解決方案。

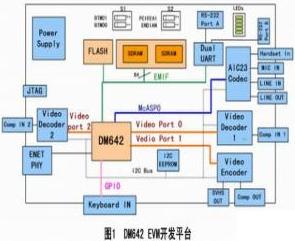

目前市場上針對以上三種產品平臺的都已有成熟的編碼器方案,其中基于DSP的主要是TI的DM642和DAVINCI媒體處理器,以及NXP的PNX15xx和PNX17xx。基于ASIC方案的相對較少,主要用的比較多的是海思的HI3510。基于FPGA的目前主要是XILINXSPARTAN3ADSP3400采用DVMICRO硬件IP核提供的編碼器方案。

H.264在監控的應用

TOYA SDVR 7IV 是采用止前最為先進H.264視頻壓縮算法的專業數字監控產品,具有強大的視頻/音頻壓縮引擎,與MPEG-4壓縮方式的硬盤錄像機相比,壓縮比可提高近30%,大大提高了存儲和網絡傳輸帶寬,同理采用新的算法極大地抑制了由于攝像機噪聲導致的圖像失真,背景流動現象,便圖像質量更加清晰。H.264產品的推出無疑又使我國的數字監控技術上了一個新的臺階。

系統采用最先進的H264視頻壓縮技術和G。729的音頻壓縮技術,實現超大無損壓縮。具備本地實時監視、音視頻同步壓縮存儲、組合報警、有線或無線網絡傳輸、管理權限設置等多種功能,單個本地系統可完成顯示16路監控畫面、每路可單獨放大和切換,查詢錄象記錄及進行回放。每個本地系統均可通過不同的網絡方式組成有線或無線數字監控系統。

2 TOYA SDVR 7IV 系統主要特點:

采用時間最先進的H.264視頻編碼技術,具有高清晰度的畫質;

在壓縮處理過程中使用多種專用技術,保證以最低碼流達到最佳畫質,采用幀內壓縮,絕無馬賽克出現;

提供多種圖象處理方法,加強噪音信號的過濾,畫面更平滑。

可同時支持H.264、MPEG-4壓縮格式;

實時壓縮、實時預覽、實時回放;

支持I\B\P幀多種組合/量化模式,圖象壓縮比更大;

在壓縮過程中,可動態抽幀,可隨時恢復,進一步減少存儲空間;

預覽、壓縮不占用CPU時間,互不干擾;

可動態精確設置多種視音頻壓縮參數,達到最佳視聽效果;

碼流可調,占用硬盤空間最少可達40兆每小時;

工藝精良,結構穩定;低功耗,發熱少,系統可靠性、穩定性高;

3 主要技術規格

壓縮畫面以及分辨,支持CIF/QCIF,圖象分辨率352X288,圖象壓縮

壓縮格式:支持H.264、MPEG-4壓縮格式;

壓縮幀率:1-25幀可調

壓縮碼率:64K~2Mbit/秒,支持CBR\VBR\Hybrid

三種碼率控制方式:變碼流、動碼流、混合碼流

網絡傳輸

支持PSTN/DDN/LAN/WAN等網絡遠程傳輸與控制

每個服務器支持32路TCP/UDP傳輸,組播無限制

4系統功能

多畫面分割:單路、四路、九路、十六路、全屏顯示等多種畫面分割;

采用錄象方式;常規錄象,動態錄象,視頻移動報警錄象,定時錄象;

字符/時間疊加功能:可以在每一路視頻上疊加地點信息,便于查詢;

多用戶管理:可設置多級管理員權限;

工作日志:詳細記錄系統工作狀態,方便用戶管理;

報警:具有報警輸入/輸出功能,單獨設置報警區域和靈敏度

圖象亮度/對比度/色度/飽和度隨時可調

支持G.729標準音頻壓縮,線性音頻輸入,音質好,占硬盤空間少

回放檢索:根據時間、日期、攝象機編號分別回放檢索

5 TOYA SDVR 7IV系統應用

技術的成熟和不斷人性化的設計,使得本系統得以全方位進入金融、保險等特殊領域,而且在全能樓宇、文化教育、醫學研究、交通指揮管制、在建工程管理、惡劣工況管理、海關及公、檢、法商業貿易等諸多領域得到了廣泛的應用。

-

處理器

+關注

關注

68文章

19165瀏覽量

229127 -

FPGA

+關注

關注

1626文章

21667瀏覽量

601845 -

編碼器

+關注

關注

45文章

3595瀏覽量

134158

發布評論請先 登錄

相關推薦

h.264編碼器下載

H.264三大開源編碼器的評測報告

H.264視頻編碼在DM642上的實現與優化

一種基于DSP平臺的快速H.264編碼算法的設計

基于ASIC的H.264編碼器設計及其ADSP驗證策略

基于TMS320DM642平臺的H.264編碼器優化

基于ADSP-BF561的H.264視頻編碼器的實現

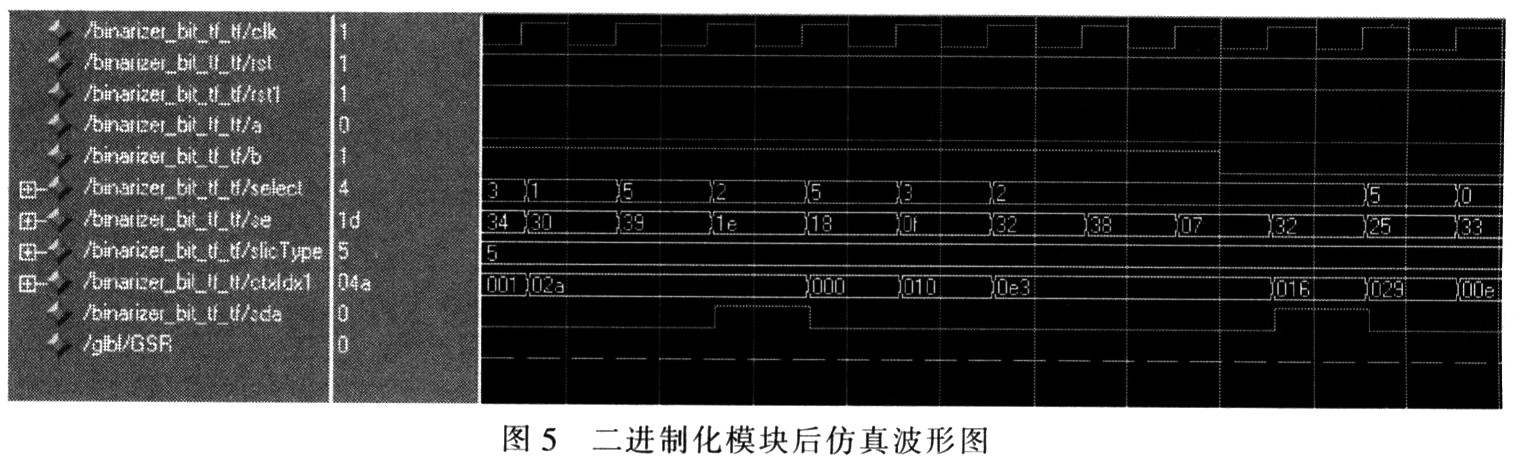

H.264中二進制化編碼器的FPGA實現

Jointwave發布的H.264編碼器可實現1080p

H.264視頻編碼器在DSP上的實現與優化

針對DSP、ASIC與FPGA三種產品平臺的H.264編碼器方案

針對DSP、ASIC與FPGA三種產品平臺的H.264編碼器方案

評論