將近一半的嵌入式設計用到FPGA,僅次于微控制器。FPGA可用于執(zhí)行任何膠合邏輯、自定義IP 、計算密集型算法加速器。通過采取一些處理任務, FPGA可以幫助提高系統(tǒng)性能,從而使單片機從周期密集的任務中騰出部分時間。FPGA還提供優(yōu)良的性能特點和更的靈活性,以適應不斷變化的標準。

基于FPGA的MCU設計有兩種基本實現(xiàn)方式:一種是在FPGA邏輯結(jié)構(gòu)中內(nèi)置MCU軟核;一種是使用基于離散FPGA的標準MCU產(chǎn)品。FPGA內(nèi)置軟核有效果,但與標準MCU相比,該方式實現(xiàn)一個微控制器是比較昂貴和耗電的。尤其是使用基于32位ARM的內(nèi)核。結(jié)果,基于FPGA內(nèi)置軟核的FPGA MCU設計只占三分之一。其余的三分之二是基于離散FPGA的標準微控制器產(chǎn)品。

標準微控制器產(chǎn)品和FPGA都沒有有效的發(fā)展兩者之間的通信,甚至使用不同的語言。因此,它們之間的接口將是一種挑戰(zhàn)。FPGA的沒有任何專門的邏輯電路來與微控制器通訊。首先,這種邏輯模塊的設計必須從零開始。其次,微控制器和FPGA之間的通信是異步的。特別是需要使單片機與FPGA時鐘域同步。最后,無論是接口,還是微控制器總線,都存在瓶頸問題。MCU和FPGA之間的信息傳遞通常需要在MCU總線上循環(huán),且通常占用資源(PIO or EBI)影響傳遞速度。因此必須注意避免與外部SRAM或閃存和微控制器總線的瓶頸問題。

MCU的FPGA接口基本上有三種硬件選擇:可編程的I / O(PIO);外部總線接口( EBI的),如果有的話;最后,MCU之間的一個專門的接口,先進的高速總線( AHB )和FPGA 。該方法的使用依賴于高端應用和市場期望。

PIO接口

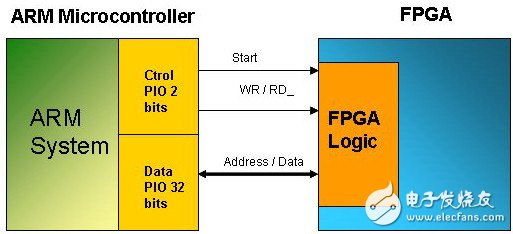

通過PIO 連接MCU和FPGA相對簡單數(shù)據(jù)傳輸來說比較簡單,包括傳輸32位的地址, 32位數(shù)據(jù),還有一些控制信號的控制。這就需要一個32位的PIO和一個2位PIO(圖1) 。

圖1 PIO連接FPGA

為了將數(shù)據(jù)傳輸?shù)紽PGA,PIO中的雙向緩沖器方向必須設置為輸出。數(shù)據(jù)傳輸?shù)紽PGA的軟件算法實現(xiàn)如下:

PIO_DATA = ADDRESS; // Pass the address to write

PIO_CTROL = START | WR; // Send start of address cycle

PIO_CTROL = CLEAR; // Clear PIO ctrl, this ends the address cycle

PIO_DATA = DATA; // Set data to transfer

PIO_CTROL = START; // Data is ready in PIO

PIO_CTROL = CLEAR; // This ends the data cycle

從FPGA讀取數(shù)據(jù)的方法相似。同樣,PIO中的緩沖區(qū)首先必須設置為輸出,然后改變方向為輸入從FPGA讀取數(shù)據(jù),下面是執(zhí)行代碼:

PIO_DATA = ADDRESS; // Set the address to read

PIO_CTROL = START | RD; // Send start of address cycle

PIO_CTROL = CLEAR; // Clear PIO ctrl, this ends the address cycle

PIO_DATA_DIR = INPUT; // Set PIO-Data direction as input to receive the data

DELAY(WAIT_FOR_FPGA); // wait for the FPGA to send the data

DATA_FROM_FPGA = *PIO_DATA; // Read data from FPGA

上述算法是一個基本的傳輸,更先進的算法是必要在ARM微控制器和FPGA之間建立適當?shù)耐ㄐ拧L貏e要注意的是,確保數(shù)據(jù)的可靠性,例如沒有因高速或等待周期造成資料遺失等。

訪問時間計算的總和:

T訪問-PIO=t1+處理階段+t2+數(shù)據(jù)階段

使用最大優(yōu)化的GCC編譯器,系統(tǒng)大約需要55個AHB周期向FPGA執(zhí)行寫操作(圖2)。

圖2 PIO向FPGA 寫數(shù)據(jù)

假設t2(FPGA的等待響應時間)也大約是25個 AHB周期,系統(tǒng)大約需要85個AHB周期從FPGA進行讀操作(圖3)。

圖3 PIO從FPGA讀取數(shù)據(jù)

MCU自身接口連接非常簡單和直截了當。然而,在FPGA里必須用特殊的邏輯來解碼所有的由PIO生成的業(yè)務流。在大多數(shù)情況下,微控制器的業(yè)務流是完全異步。因此,F(xiàn)PGA必須能夠從微控制器中過采樣控制信號;否則,F(xiàn)PGA將錯過時間窗口且業(yè)務流將不會最終到達FPGA內(nèi)。

因為處理器專門負責維持PIO工作,所以處理時間消耗很大。雖然CPU是從事數(shù)據(jù)傳輸,它還是不能做別的事了。因此,這一解決方案有可能使系統(tǒng)處理陷入癱瘓。DMA不可能使用的PIO接口,所以程序員必須限制的數(shù)據(jù)帶寬,以便其他任務能夠與MCU進行通訊。例如,如果有一個常規(guī)的進程要求100 %的處理器運行周期,同時又要與FPGA進行串行(SPI,USART或TWI)通信(讀或?qū)懀敲催@兩個進程必須有一個要等待。如果發(fā)送到或接受來自FPGA的數(shù)據(jù)沒有及時的存進緩沖區(qū),那么到下一個字節(jié)/字數(shù)據(jù)時可能會溢出。從本質(zhì)上講,嵌入式處理器成為受邤賴的數(shù)據(jù)移動硬盤。

通過外部總線接口連接(EIB)

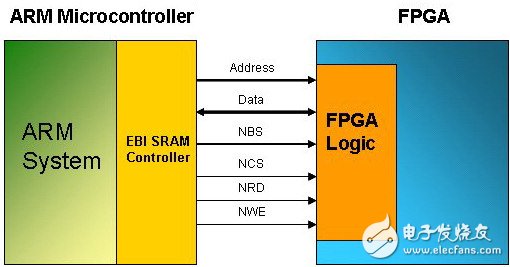

許多32位微控制器有一個外部總線接口(EBI)模塊,它是為外部設備和基于ARM設備的存儲控制器之間傳輸數(shù)據(jù)而設計的。這些外部存儲控制器能夠處理幾種類型的外部存儲器和外圍設備,如SRAM,PROM,EPROM,EEPROM,flash和SDRAM。只要FPGA可以處理預定義存儲器接口,EBI也可用于FPGA的接口。在EBI中使用靜態(tài)存儲器接口(SRAM)對于FPGA通信來說是最好的,因為它設計簡單,且大多數(shù)設計者都熟悉它。至于PIO接口, FPGA不得不包含一個模塊,用來理解SRAM時間,并能產(chǎn)生一個響應返回微控制器(圖4)。

圖4 EBI-SMC接口

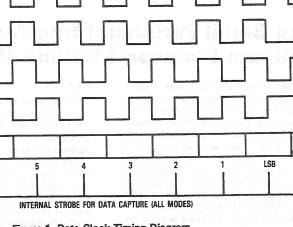

圖5顯示了EBI讀SMC存儲器接口的標準時間,而圖6顯示了其標準寫周期。

圖5 EBI-SMC讀周期

圖6 EBI-SMC寫周期

注意:這些時間波形是默認的SMC規(guī)格。所有可編程參數(shù)顯示都基于外部設備的速度。

EBI的接口速度比PIO塊,是因為EBI有其自己的I / O,且大部分的信號是并行的。但是,如果外部設備很慢或引入等待狀態(tài), EBI的速度優(yōu)勢可能會受到損害。

跟PIO接口一樣, EBI接口必須由處理器或其他的主AHB來驅(qū)動。因此,實現(xiàn)帶寬的EBI的還依賴于軟件,并取決于它可以利用多少處理器時間。當然,可能受到帶寬的限制。這又可能限制了嵌入式處理器旨在實現(xiàn)的其他系統(tǒng)功能。

在MCU中使用專用的FPGA接口

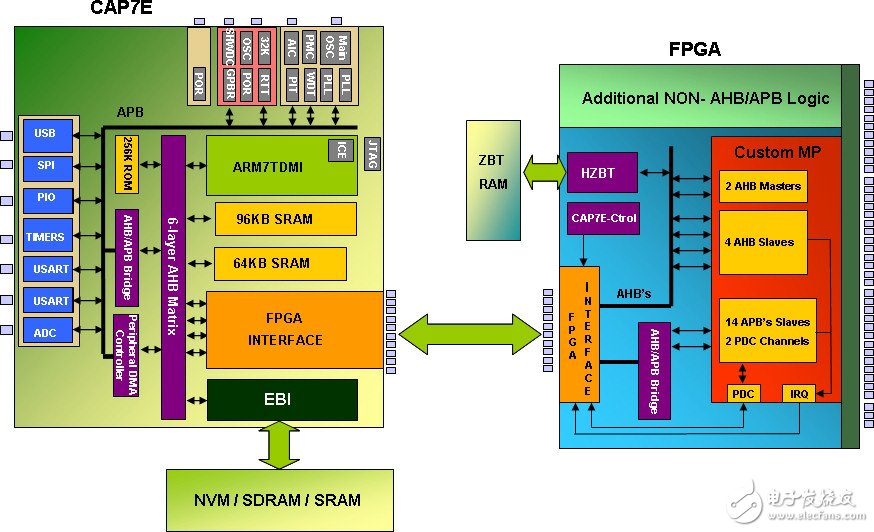

基于ARM7的微控制器提供一個特殊接口,它允許FPGA通過DMA存取2個主AHB和四個副AHB直接接入MCU的內(nèi)部AHB總線。在啟動時,一個外加的副AHB可用于重新映射ROM,它通過使用外部ZBT RAM具有PROM重新映射功能的FPGA來實現(xiàn)。

該接口還提供了FPGA接入14個副先進外圍總線(APB)、兩個全雙工的DMA通道、多達13個中斷優(yōu)先編碼(IRQs)、兩個DMA傳輸?shù)姆蔷幋aIRQs和32位共享可編程I/O。該FPGA接口通過微控制器接入預先定義的主副AHB(圖7)。

圖7 MCU專用的FPGA接口

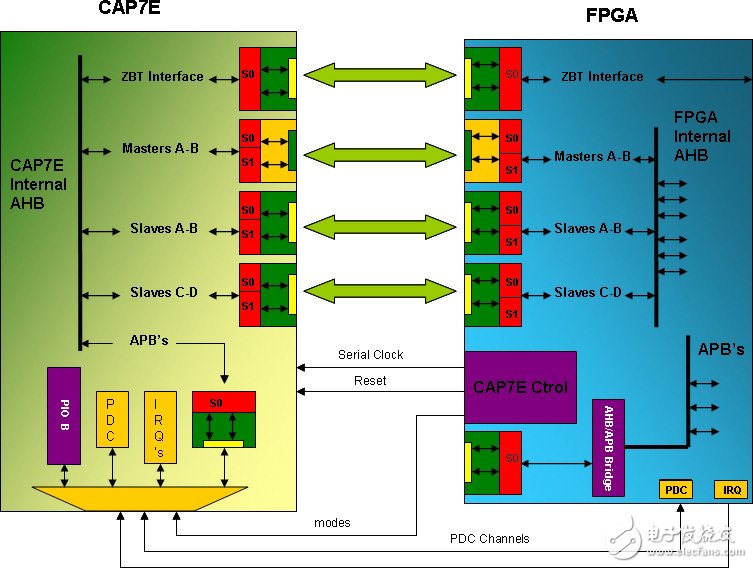

FPGA接口是基于多個并串行轉(zhuǎn)換器來編碼和解碼所有微控制器和FPGA之間的業(yè)務流。為了使兩個不同設備之間能進行有效的同步通信,必須滿足以下要求:

在FPGA必須能夠處理時鐘偏斜平衡和時延消除。賽靈思的FPGA采用DCM(數(shù)字時鐘管理器)強制性處理所有時延消除,且要求產(chǎn)生時鐘。Altera的器件需要使用鎖相環(huán)電路。該FPGA還必須為微控制器的內(nèi)置接口提供配置和復位方式。它必須為微控制器提供的串行通信時鐘,頻率范圍應在100兆赫以上。ARM7的內(nèi)部時鐘和串行時鐘之間的比率應為0.8或更低(ARM的時鐘/串行時鐘)。

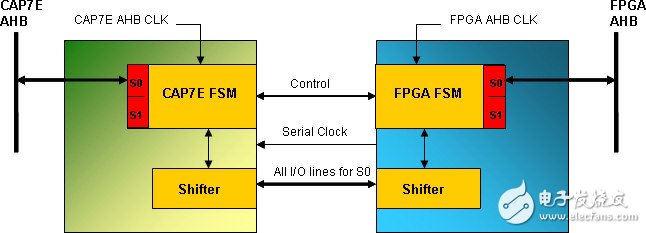

FPGA接口是基于一套編碼和解碼AHB內(nèi)部業(yè)務流的單元。各主從AHB編碼/解碼的數(shù)據(jù)傳輸通過使用專用并串行轉(zhuǎn)換器的MPIO來實行。由于傳送大量數(shù)據(jù),一個單一的傳輸就消耗多個AHB總線時鐘周期。具體所需的時鐘周期取決于ARM7中的AHB時鐘、串行時鐘和FPGA中的AHB時鐘之間的比例。由于微控制器的AHB時鐘與FPGA中的AHB時鐘之間相互獨立, FPGA和微控制器可以在不同的頻率運行。甚是FPGA內(nèi)的主或副AHB時鐘可以在不同的頻率運行。

微控制器和FPGA上的每個并串行轉(zhuǎn)換器阻滯都有一個互補的有限狀態(tài)機(FSM)與AHB總線打交道。因此,該接口可以借鑒EBI或PIO消除共同接口瓶頸的技術(shù)來處理同步傳輸問題。

帶有直接FPGA接口的微控制器幾乎所有的外圍都有DMA通道,有幾個DMA通道專用于FPGA的接口。多通道外圍DMA控制器( PDC )支持該DMAs,像其他兩種方法一樣,在FPGA、外設和存儲器之間傳輸數(shù)據(jù)時通過CPU卸荷。這避免了普通ARM7的帶寬限制,它被只有4萬比特每秒(Mbps)數(shù)據(jù)傳輸速率完全壟斷。

通過從CPU中卸下這一任務, PDC可以實現(xiàn)處理時間占85 %CPU周期,數(shù)據(jù)傳輸率12 Mbps。多重DMA通道是專為FPGA接口連接PDC多個特定應用的外設和接口而設的,不受微控制器的任何干預。在PDC中使用DMA專用通道,可以使ARM處理器有時間把重點放在處理器的繁重任務上,提高系統(tǒng)的總體性能和數(shù)據(jù)帶寬(圖8)。

圖8 ARM7與FPGA接口

該并串行轉(zhuǎn)換器模塊能處理所有的AHB和串行通訊。它由一個有限狀態(tài)機(FSM)和移位器組成。有限狀態(tài)機解讀AHB,并與AHB對話。當主AHB初始化一個傳輸(讀/寫操作)時,F(xiàn)SM通過使用遵守的AHB協(xié)議的HREADY來引入等待狀態(tài)。FSM直接根據(jù)AHB時鐘和串行時鐘之間的比例來自動處理引入等待周期的數(shù)量。比例越小,引入的等待周期就越少。

FSM控制移位器,負責處理所有微控制器和FPGA之間的數(shù)據(jù)轉(zhuǎn)移(序列化),每周期傳輸在2個bits的數(shù)據(jù)。如果串行時鐘速率為100兆赫,移位器的傳輸速度為200 Mbps。

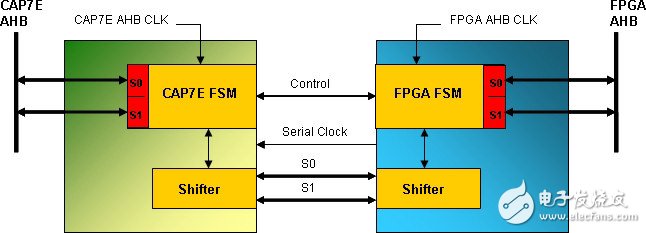

這些并串行轉(zhuǎn)換器模塊處理主口A / B、副口A / B和副口C/D,通過FPGA 內(nèi)的“模式”模塊在復位時程序化,使可用的I / O數(shù)量盡可能多。設計者可以為一個單一的串行配置選擇使用所有的10個I / O線。在這種情況下,串行模塊將只處理一個的AHB接口。例如,如果用戶僅想使用AHB主口A,串行模塊將所有主口設定為“串行單配置” 。這種配置將改善轉(zhuǎn)換器之間的傳輸速度,從而加快了微控制器和FPGA之間的傳輸速度(圖9)。

圖9 串行單配置

另一種選擇是配置串行模塊為“雙串行配置”使其能處理2個AHB接口,2個AHB (主/副)之間共用10個I / O線。在這種情況下,微控制器和FPGA之間的數(shù)據(jù)傳輸速率較低,但數(shù)據(jù)帶寬更高,因為有2個AHB接口可用。雙配置給另一個AHB接口重新使用一半以上的專用I / O(圖10)。

圖10 雙串行配置

FPGA的接口邏輯

當通過EBI或PIOs執(zhí)行一個FPGA接口時,工程師必須寫RTL代碼,讓FPGA與MCU進行溝通。直接FPGA接口微控制器供應商提供的所有RTL需要為每個具體的FPGA供應商建立適當?shù)木幋a和解碼通信限制。這種邏輯模塊產(chǎn)生一個重置,并提供不同模式下的重置條件。供應商提供的RTL可讓用戶來決定選擇哪些功能來。默認情況下,所有的模式位0 (表1)。

表1 模式位

一個供應商提供的模板可用于FPGA接口的主從AHB實例。提供具體的例子。在FPGA模板,一個模塊所謂的“自定義MP”不費力的整合AHB / APB外設。因為系統(tǒng)將使用FPGA邏輯,此模板讓設計師使用遷移的兩片MCU加FPGA毫不費力的實現(xiàn)單芯片可定制微控制器。

外部ZBT-RAM和NVM/SDRAM/SRAM是可選的,它基于應用程序和系統(tǒng)要求。

設計人員還可以在FPGA添加非AHB邏輯,為添加與AHB總線無關(guān)的功能提供了靈活性。

在單一配置模式下,單一AHB接口從微控制器傳輸所有的AHB信息到FPGA需要4個AHB時鐘周期,反之亦然(圖11 ) 。在雙配置模式下,雙AHB接口從微控制器傳輸所有的AHB信息到FPGA需要8個AHB時鐘周期,反之亦然。

圖11 通過直接FPGA接口傳輸?shù)淖x/寫時間

發(fā)生在ARM7 MCU和FPGA之間的相關(guān)傳輸時間如下:

? t1:標準時間——2個AHB周期;

? t2:FPGA傳輸所需時間(單一AHB接口4個周期,雙AHB接口8個周期);

? t3:FPGA的外設響應時間;

? t4:傳輸響應返回CAP7E的時間(單一AHB接口4個周期,雙AHB接口8個周期);

? t5:從FPGA到CAP7E AHB總線內(nèi)部讀取響應/數(shù)據(jù)時間;

? t6:引入等待周期時間。

下面的公式是用來近似從ARM到FPGA外設的存取時間:

注: t1和的t5相對于PIO和EBI是可以忽視的的AHB周期時間。

在數(shù)據(jù)傳輸速率低的情況下,如點陣式液晶顯示器,MCU到FPGA通過PIO或EBI接口就足夠了。然而,F(xiàn)PGA和MCU之間或其他一些外設和存儲器的高數(shù)據(jù)傳輸率可以完全占用CPU周期和給外設創(chuàng)造瓶頸。舉例來說, TFT液晶彩色圖形將需要傳輸大量的數(shù)據(jù)到液晶顯示器幀緩沖區(qū),這最有可能完全占用CPU和EBI。這種應用將更好地執(zhí)行從微控制器到FPGA的直接接口連接,而允許液晶數(shù)據(jù)通過DMA傳輸,使處理器空出時間處理其他事和使EBI空出時間傳輸其他數(shù)據(jù),如從閃存運行主要應用軟件,或TFT液晶顯示器為單個或多個幀緩沖區(qū)使用SDRAM。

此外, FPGA中的AHB邏輯定義類似MCU,猶如它在微控制器“內(nèi)部”。這使得未來設計路線很容易就轉(zhuǎn)移到可定制微控制器。

直接FPGA接口的發(fā)展時間也較短,因為接口已經(jīng)在微控制器內(nèi)部定義且邏MCU供應商提供了FPGA的輯模塊。設計者不需要寫入任何接口RTL 。帶專用FPGA接口的微控制器將會提高整個系統(tǒng)的性能和設計的易用性。

-

微控制器

+關(guān)注

關(guān)注

48文章

7490瀏覽量

151061 -

FPGA

+關(guān)注

關(guān)注

1626文章

21671瀏覽量

601914 -

液晶顯示器

+關(guān)注

關(guān)注

11文章

575瀏覽量

43609

發(fā)布評論請先 登錄

相關(guān)推薦

怎么通過FPGA實現(xiàn)微控制器?

基于XCCV3004HQ240芯片的8051微控制器接口設計

基于FPGA的航天相機控制器接口的設計

MAX1169 ADC與PIC微控制器的接口

可不使用微控制器配置Dallas Semiconductor

基于FPGA的PCI接口控制器的設計與實現(xiàn)

微控制器的開發(fā)方案

針對微控制器應用的FPGA實現(xiàn)

基于FPGA中實現(xiàn)微控制器

微控制器的FPGA接口的設計與實現(xiàn)方案介紹

微控制器的FPGA接口的設計與實現(xiàn)方案介紹

評論