在信號采集與處理中,常只關心具有較窄帶寬和較強周期特征的信號,這時寬帶噪聲成為必須濾除的有害成分。信號的頻譜攜帶著信源最本質的特征,但是實際采集的信號不可避免地受到寬帶噪聲或寬帶干擾的影響,如何快速、高效地消除這些噪聲和干擾,增強目標譜線在信號處理領域具有重要的意義。ALE利用窄帶信號的周期性和寬帶噪聲的弱相關性,能夠在信號特征未知的條件下自適應地將信號從噪聲中提取出來,廣泛應用于目標識別和特征提取中。FPGA因具有高度的設計靈活性、高速的數據處理能力、豐富的片內資源而在數字信號處理領域占用重要的地位。在此利用FPGA作為數字信號處理的核心部分。流水線結構和分布式算法即是充分利用FPGA高速處理能力,實現復雜數字信號處理算法的有效途徑。ALE核心部分構造了利用LMS(Least Mean Square LMS)算法實現自適應譜線增強以及硬件實現的FPGA流水線結構。

1自適應濾波原理

自適應濾波是相對固定濾波器而言的.固定濾波器濾波頻率是固定的,自適應濾波器濾波的頻率自動適應輸入信號而變化的,所以其適用范圍更加廣泛。自適應濾波器是滿足某種準則的最佳濾波器,這種濾波器能夠在不需要任何關于信號和噪聲先驗統計知識的情況下,自動地根據輸入信號的變化更新自身的權系數,來滿足最佳濾波的需要。自適應濾波器不僅能夠處理平穩隨機信號而且能處理非平穩隨機信號。這些特點使得自適應濾波器在干擾消除、預測、反演、辨識等信號處理領域得到廣泛應用。

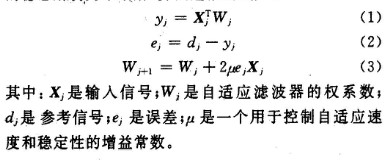

自適應濾波原理包含兩方面的內容:一是調整濾波器系數的自適應算法,二是濾波器結構。自適應濾波算法是設定某種準則,使濾波后的輸出信號與參考信號的差在此準則下最小。維納準則廣泛應用于自適應濾波,它的解為維納解。濾波器結構是具體實現自適應算法的途徑,尋求高效的濾波器結構一直是自適應濾波的研究重點。FIR橫向結構是最常見的濾波器結構。為橫向結構濾波器設計硬件的流水線是在FPGA中實現高速自適應濾波的有效途徑,因此該設計中采用流水線實現ALE的自適應濾波器。自適應濾波器原理如圖1所示。其中,x(n)為輸入信號,y(n)為輸出信號,d(n)為參考信號,e(n)為誤差信號。

LMS算法是一種易于實現、性能穩健、應用廣泛的算法。它采用負誤差能量梯度更新濾波器的權系數,它的穩態解仍為維納解,算法遞推公式如下:

其中:Xj是輸入信號;Wj是自適應濾波器的權系數;dj是參考信號;ej是誤差;μ是一個用于控制自適應速度和穩定性的增益常數。

2.1 ALE原理

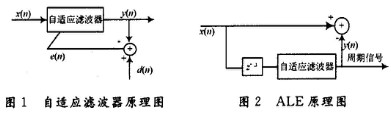

ALE屬于自適應濾波的范疇,但是在譜線增強的自適應濾波器設計中,沒有外部參考信號可以利用。此時,利用窄帶信號周期性明顯而寬帶噪聲周期性差,延遲一段時間后窄帶信號的相關函數會顯著地強于寬帶噪聲這一特征,將原始輸入信號接入具有固定延遲的延遲線作為參考信號。只要選取的延遲△足夠長,參考信號的寬帶噪聲和原始輸入的寬帶噪聲相關性就會迅速減弱,而窄帶周期信號的相關性不會受到影響。根據自適應濾波理論可知,ALE濾波會有一個學習過程,學習過程就是誤差信號趨于不斷減小的過程。當學習過程進入穩態后,濾波器輸出是源窄帶周期信號和一個隨機的誤差,其誤差可以通過選取合適的步長因子而達到很小的振幅。ALE原理圖如圖2所示。

2.2 ALE的Matlab仿真

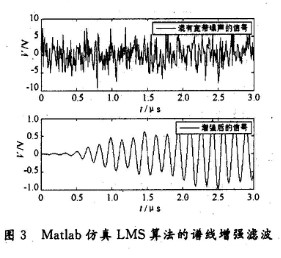

Matlab是數字信號處理和仿真的有效工具,設計之初使用Matlab進行仿真,可以有效地*估設計的最終效果,為整個設計過程提供強有力的理論支持。首先用Matlab仿真以LMS算法實現的ALE,從仿真結果的時域波形和處理時間兩方面證明算法在ALE系統中的有效性。將正弦波混合高斯白噪聲作為譜線增強濾波的輸入信號,圖3是用Matlab對算法的部分仿真結果。可以看出根據混有噪聲的輸入信號根本無法判斷原始周期信號,經過0~100時間長度的學習過程后濾波器輸出信號已經具有明顯的周期性,寬帶噪聲得到有效的濾除,窄帶信號得以濾出。而這段時間在高速FPGA中只需要μs級的處理時間,滿足實時性要求。

3 系統結構

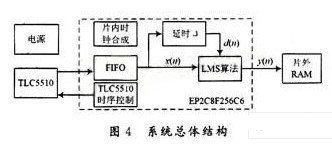

ALE系統總體包括:模/數轉換、FPGA核心處理、片外RAM、電源等。前端采用TLC5510完成模擬信號的采集,并以數字信號的形式傳遞給FPGA。FPGA部分是整個系統的核心,其實現模/數轉換器時序控制、內部數據緩存FIFO、片內時鐘合成、譜線增強算法以及片外RAM控制。經過譜線增強后的數據存入片外RAM芯片CY7C1021V。電源提供整個系統需要的3.3 V和5 V以及TLC5510的參考電壓。系統結構如圖4所示。

TLC5510是TI公司的高速模/數轉換器,可以用于視頻處理、高速數據轉換等領域,它的轉換速率達到20 Mb/s,采用高速AD芯片是為了與FPGA的高速處理能力相匹配。EP2C8F256C6是Altera公司的生產的CycloneⅡ系列的FPGA,片內具有162 Kb的片內存儲器和36個18×18 b片內乘法器,可以用于實現復雜數字信號算法。片內存儲器基于流行的M4K存儲器塊,可以支持廣泛的配置方式,包括RAM,ROM、先入先出(FIFO)緩沖器以及單端口和雙端口模式等。片內乘法器是低成本數字信號處理(DSP)應用的理想方案。這些乘法器可用于實現通用DSP功能,如有限沖擊響應(FIR)濾波器、快速傅里葉變換、相關器、編/解碼器以及數控振蕩器(NCO)。EP2C8F256C6提供高級外部存儲器接口支持,允許開發人員集成外部單倍數據速率(SDR)、雙倍數據速率(DDR)、DDR2 SDRAM器件以及第2代4倍數據速率(QDRⅡ)SRAM器件。片內具有時鐘管理模塊,利用PLL實現片內時鐘合成,使數據處理速率遠高于信號采集速率,以滿足實時性要求。在FPGA內部首先實現TLC5510的采樣控制,采樣信號先要存人片內FIFO,當每次ALE算法迭代完成后,取出FIFO中的數據,更新處理數據。需要處理的數據經過信號延遲處理和LMS自適應濾波算法后得到譜線增強的信號。片內時鐘合成模塊為系統提供時鐘信號,利用片內PLL對晶振時鐘倍頻和分頻,為片內提供600 MHz時鐘和片外TLC5510以及RAM提供10 MHz時鐘。為了保證數據精度。經過ALE處理后的數據以16位二進制數字信號輸出。片外存儲器選用64K×16 b靜態RAM芯片CY7C1021V,它的讀/寫控制時序也由FPGA實現。

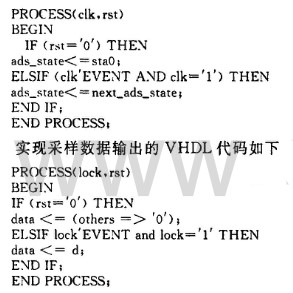

3.1 TLC5510的控制

TLC5510是8位高速模數轉換器,以流水線的工作方式進行采樣,在每一個時鐘周期啟動1次采樣、完成1次采樣,采樣在時鐘下降沿進行,經過2.5個時鐘周期后輸出轉換結果。設計中根據采樣時序,用狀態機來描述采樣控制過程,實現了采樣的控制。實現狀態交替的VHDL代碼如下:

3.2 采樣信號延遲

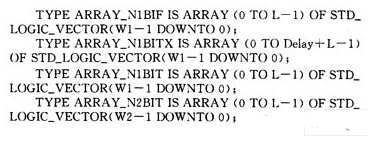

為了實現延時,FPGA片內開辟了3個緩沖區,分別是輸入、時延、權值緩沖區。采樣后的數據首先存入片內數據緩存FIFO,進入待命狀態。時延緩沖區實現△長度的時延,權值緩沖區儲存權值。其中,時延緩沖區和輸入緩沖區地址是連續的。時延緩沖區的長度由延遲△決定,輸入緩沖區和權值緩沖區的長度由權值的維數決定。緩沖區的實現是在VHDL語言編寫的程序中定義存儲數據的向量,這些數據向量的數據類型定義如下:

其中:ARRAY_N1BIF定義的是濾波器參數向量的數據類型;ARRAY_N1BIYX定義的延遲后信號向量的數據類型;ARRAY_N1BIT定義的是輸入信號向量的數據類型;ARRAY_N2BIT定義的是譜線增強后信號向量的數據類型;W1是采樣數據的寬度,這里為8;Delay是延時長度;L是濾波器階數。

3.3 LMS算法核心模塊

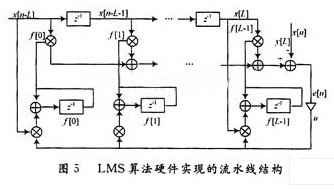

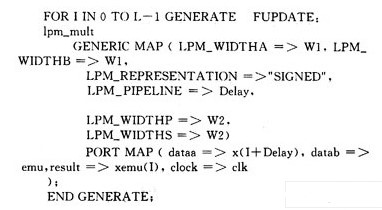

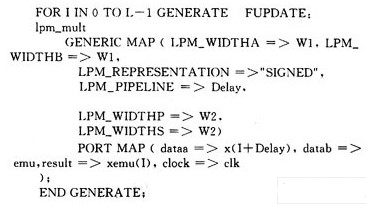

這是設計的核心部分也是設計中的難點。用FPGA實現復雜數字信號處理并不像DSP中那樣簡單,需要考慮時序同步、數據寬度以及如何舍入。該設計采用16階自適應濾波器實現ALE,濾波器初始權值全部為0,按照式(3)的算法進行迭代更新,算法實現中用到大量乘法運算。調用芯片內部嵌入的乘法器宏功能模塊lpm_mult使實現這些乘法運算更加快速、高效的方案。lpm_mult模塊輸入采樣的8位數據,因為在乘法運算中2個8位二進制數相乘得到的結果是1個16位二進制數,所以設計中將處理結果輸出為16位二進制數。為了提高自適應濾波速度,設計中采用流水線的濾波器結構。流水線結構能夠顯著地提高處理的速度,但是要消耗更多的硬件資源,特別是硬件乘法器,如果LMS FIR濾波器的長的為L則需要2L個通用乘法器。設計中L=16,片內有36個片內乘法器可以勝任處理要求。編譯結果顯示片內應用于LMS核心算法的其他資源消耗全部小于或等于總消耗的6%,其余資源可以用于片內的采樣、輸出等時序控制。LMS算法硬件實現的流水線結構框圖如圖5所示。

流水線結構中調用乘法器的VHDL代碼如下:

4 仿真結果分析

VHDL程序在QuartusⅡ軟件上部分仿真結果如圖6所示,圖中仿真數據以十進制表示。因為仿真結果不便于繪制類似Matlab中的圖形,將仿真結果的數據與Matlab仿真結果進行對比。通過行比較,發現處理結果在大體上與Matlab相一致,但是在幅度上整體有些衰減,這是由于FPGA中將處理結果的低位進行截尾處理,而Matlab仿真環境使用浮點形式、數據位數長,處理精度遠高于FPGA,FPGA設計中存在較大的截尾誤差。該仿真結果表明,基于:FPGA實現ALE是切實可行的。

5 結 語

系統采用FPGA芯片加上少量的外圍電路,完成了信號的自適應譜線增強。通過調用FPGA片內乘法器和片內存儲器,完成了LMS算法的自適應譜線增強,仿真結果與理論相符合。現代數字信號處理算法大多要進行大量的乘法運算,調用FPGA片內乘法器是實現這些算法的快速高效而又經濟的手段,這使得復雜信號處理算法在FPGA上實現成為可能。流水線結構是硬件設計中犧牲資源以提高速度的有效手段,有效地利用流水線可以顯著地提高資源利用率和處理速度。該設計可以實現高速、準確地譜線增強,在需要濾除寬帶噪聲提取單根譜線的領域具有一定的現實意義。

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601902 -

濾波器

+關注

關注

160文章

7731瀏覽量

177699 -

仿真

+關注

關注

50文章

4044瀏覽量

133424

發布評論請先 登錄

相關推薦

變步長LMS自適應濾波算法及其分析

基于粒子群算法的自適應LMS濾波器設計及可重構硬件實現

改進的變階數LMS自適應濾波算法

求助!如何使用labview編寫 VS_LMS 算法自適應陷波器

基于LMS算法與RLS算法的自適應濾波

采用FPGA芯片完成基于LMS算法的自適應譜線增強系統的設計

采用FPGA芯片完成基于LMS算法的自適應譜線增強系統的設計

評論