應用VHDL語言設計數字系統,很多設計工作可以在計算機上完成,從而縮短了系統的開發時間,提高了工作效率。本文介紹一種以FPGA為核心,以VHDL為開發工具的數字秒表,并給出源程序和仿真結果。

1 系統設計方案

1.1 系統總體框圖

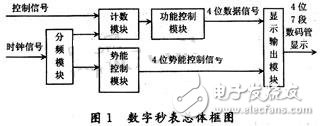

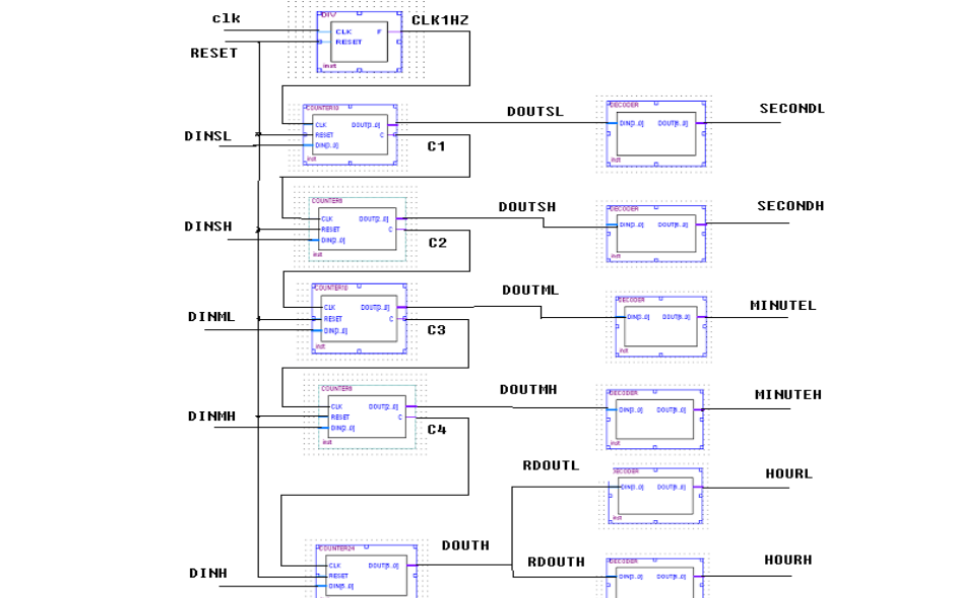

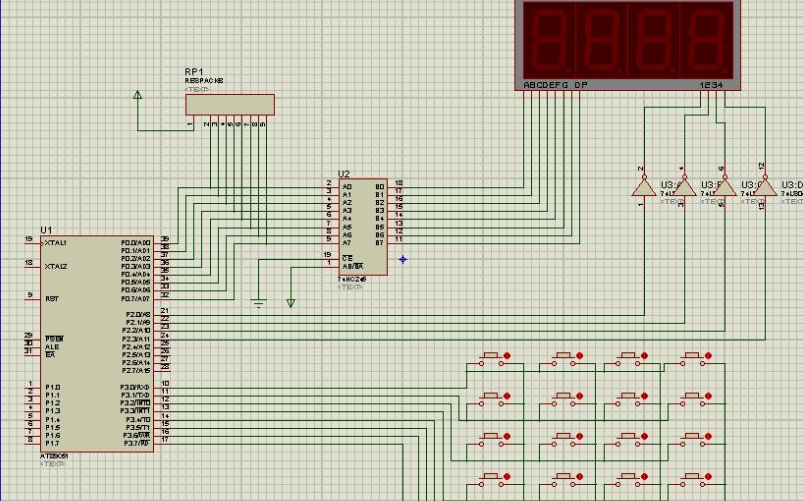

數字秒表主要有分頻器、計數模塊、功能控制模塊、勢能控制模塊和顯示輸出模塊組成。系統框圖如圖1所示。

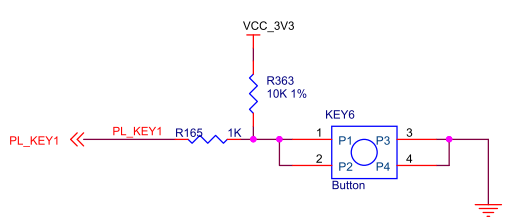

本次的設計仿真選用以EP1C6Q240芯片為核心的FPGA開發板,該開發板提供了較完善的外圍周邊電路和信號接口,并提供了一塊4位7段數碼管的擴展板,為本次設計提供了硬件條件。在設計中,功能控制模塊根據控制選擇不同的功能狀態的時間輸出,通過勢能控制模塊和顯示輸出模塊驅動7段數碼管顯示相應的時間。

1.2 系統功能要求

(1)具有時鐘秒表系統功能要求顯示功能,用4個數碼管分別顯示秒和百分秒;

(2)具有3種功能狀態:系統時間運行狀態,系統時間至零狀態,時鐘正常顯示狀態,通過輸入控制信號可以使系統在這3個狀態之間切換,使數碼管顯示相應狀態的時間;

(3)開啟時間設定、關閉時間設定可通過控制信號中的時間調節來設置,在秒設置方面每按一下,秒就會自動加1,采用60進制計數,當計數到59時又會恢復為00;百分秒設置方面每按一下,百分秒會自動加1,采用100進制計數,當計數到99時,向上進位并恢復00。系統時間可以同單獨的至零信號,將數碼管顯示時間直接恢復到00.00狀態。

2 模塊功能設計及仿真

2.1 分頻模塊

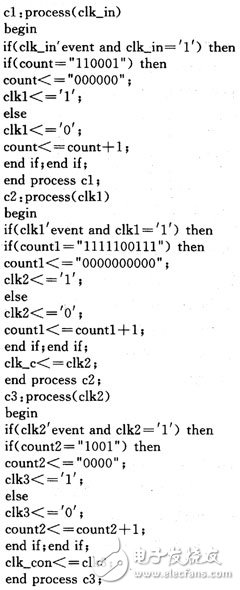

開發板提供的系統時鐘為50 MHz,通過分頻模塊3次分頻,將系統的時鐘信號分為100 Hz和1 000 Hz分別提供給計數模塊和勢能控制模塊作為時鐘控制信號。該模塊部分VHDL源程序如下:

2.2 計數模塊

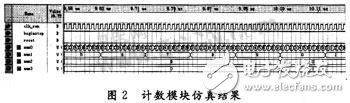

計數模塊中,時鐘信號是100 Hz作為秒表的百分秒輸入,百分秒為100進制計數器,其進位輸出作為秒的計數時鐘,秒為60進制計數器。控制信號輸入端的begin-stop和reset信號控制計數器的開始、停止和至零。該模塊部分VHDL源程序如下,方針結果如圖2所示:

2.3 勢能控制模塊

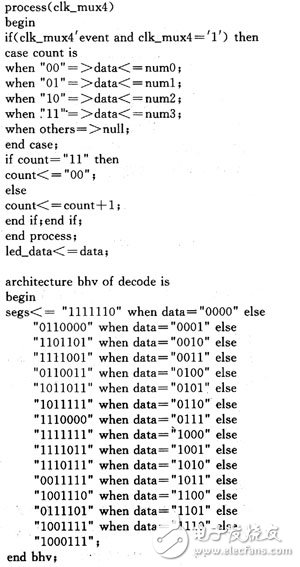

本次設計選用的開發板數碼管擴展板的數碼顯示采用的是4個數碼管動態掃描輸出,一般只要每個掃描頻率超過人的眼睛視覺暫留頻率24 Hz以上就可以達到點亮單個顯示而不閃爍,掃描頻率采用1 kHz信號。通過勢能控制,每個數碼管的顯示頻率為250 Hz,滿足顯示要求。該模塊部分VHDL源程序如下:

2.4 顯示控制模塊

本次設計選用的開發板在4位數碼管輸入方面只提供1個數據接口,用來動態顯示4位數據,在數據輸入信號方面要做到和勢能控制信號同頻率輸出,才能保證數碼顯示不會出錯或顯示移位。該模塊部分VHDL源程序如下:

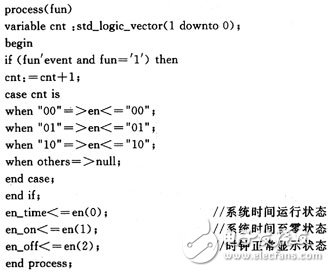

同時通過控制信號示系統處在不同的功能狀態:系統時間運行狀態,系統時間至零狀態,時鐘正常顯示狀態。利用功能轉換信號實現3個功能狀態之間的轉換,并產生相應的控制信號去控制顯示輸出模塊不同狀態的正確顯示。其部分源程序如下:

3 系統部分功能仿真

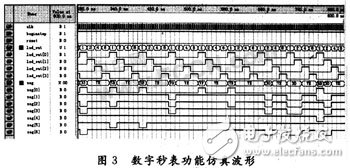

各部分模塊完成后,用QuartusⅡ對程序編譯、仿真、得到的仿真波形如圖3所示。

本系統采用的FPGA芯片為Altera公司的EP1C6Q240,用VHDL和QuartusⅡ軟件工具開發,設計輸入完成后,進行整體的編譯和邏輯仿真,然后進行轉換、延時仿真生成配置文件,最后下載至FPGA器件,完成結果功能配置,實現其硬件功能。

4 結 語

該系統運用先進的EDA軟件和VHDL,采用模塊法自頂向下的設計原則,并借助FPGA實現數字秒表的設計,充分體現了現代數字電路設計系統芯片化,芯片化設計的思想突破了傳統電子系統的設計模式,使系統開發速度快、成本低、系統性能大幅度地提升。

-

FPGA

+關注

關注

1626文章

21675瀏覽量

601950 -

芯片

+關注

關注

454文章

50444瀏覽量

421921 -

vhdl

+關注

關注

30文章

816瀏覽量

128081

發布評論請先 登錄

相關推薦

VHDL語言在FPGA/CPLD開發中的應用?

基于CPLD的VHDL語言數字鐘(含秒表)設計

基于Xilinx FPGA和VHDL的數字秒表設計與仿真實現

利用VHDL硬件描述語言和FPGA技術完成驅動時序電路的實現

使用VHDL語言和FPGA設計一個多功能數字鐘的論文免費下載

硬件描述語言和FPGA的具體關系

基于VHDL語言和FPGA開發板實現數字秒表的設計

基于VHDL語言和FPGA開發板實現數字秒表的設計

評論