1 引言

工業CT 機運動控制系統往往需要對多個軸的運動進行精確、實時控制,在以往的系統中多采用工控機+多塊板卡的結構進行運動控制器的設計。隨著工業CT 機整體功能日趨復雜,整體系統對運動控制系統的體積、成本、功耗等方面的要求越來越苛刻。另一方面,運動控制系統控制的軸數越來越多、控制精度要求越來越高、控制對象的實時性要求越來越強。

現有的工控機+多塊板卡組成的控制系統逐漸呈現出運動控制方面的劣勢。ARM+FPGA 的硬件方案,將工控機從現有的運動控制系統中解放出來,取而代之的是體積小、功耗低、功能強的ARM 處理器。強大的嵌入式Linux 操作系統保證ARM 處理器的功能可以發揮到最佳。

2 硬件系統關鍵技術設計與實現

本系統采用ARM+FPGA的結構進行運動控制系統的設計,與目前應用中常見的IPC(IndustrialPersonal Computer)+板卡的運動控制系統相比具有以下優點:

(1) 采用FPGA 完成運動控制細節任務,實現硬件軟化的設計思想。即具有軟件可編程、可重構的特性,又有硬件高性能、高可靠、高一致性的優點。

(2) 采用嵌入式應用方案與現有IPC+板卡結構相比無論從體積、成本、還是性能方面相比都具有較大的優越性。

(3) FPGA 具有高速并行的執行能力,系統的實時性能得到較大的提高。

(4) 將ARM 中操作底層硬件的驅動程序進行打包,方便應用程序調用,可以較快完成用戶的二次開發。

2.1 硬件系統總體設計

工業CT 運動控制系統結構如圖1 所示。該系統以Atmel 公司一款ARM9 核處理器AT91RM9200和Altera 公司的Cyclone 系列芯片EP1C6Q240C8 為核心。ARM9 作為主控芯片負責整個系統的控制,通過AHB[3]總線協調與FPGA 之間的數據交換,并將接收到的數據通過網絡發送到工業控制計算機進行圖像的處理與重建。FPGA 則負責接收數據采集系統的串行數據,并把其轉化成并行數據存入FPGA 的RAM 中,同時對ARM 發出中斷請求響應,通知ARM9 讀取。AT91RM9200、SDRAM、FLASH 以及電源等基本外圍電路構成嵌入式Linux 運行的最小系統,而FPGA 最小系統則由EPlC6Q240C8、時鐘電路、配置接口等組成。然后兩者通過高速AHB 總線進行連接,實現數據的快速傳輸。

圖1 工業CT 運動控制系統結構圖

2.2 ARM 與FPGA 接口設計

在系統中ARM 作為通用處理器,用來實現系統任務的觸發、系統命令的發送和任務的調度等功能。

FPGA 作為ARM 的外設,用來對ARM 經地址數據總線傳送過來的命令進行解析,并最終按照ARM 命令的要求,完成脈沖發送和脈沖計數的功能及具體的運動控制細節任務。

兩塊FPGA通過各自的地址/數據總線與ARM的地址/數據總線連接起來,雙方可以進行雙向的數據交換。

ARM 與FPGA 通過地址選通信號線連接起來,兩塊FPGA 各自作為ARM 的外設芯片,運行在獨立的地址空間,地址選通信號結合地址總線實現ARM對 FPGA 內部寄存器的尋址。

3 軟件系統關鍵技術設計與實現

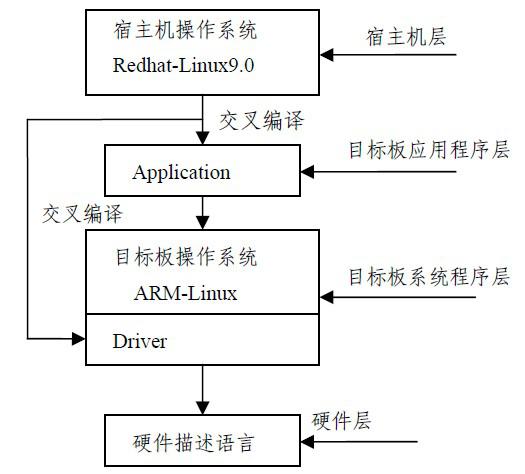

系統軟件總體采用分層思想進行設計。整個系統軟件主要由宿主機操作系統、宿主機開發軟件、目標板操作系統、目標板底層硬件驅動程序、目標板應用程序、HDL 硬件描述語言組成。宿主機操作系統選擇REDHAT-LINUX9.0 版本;宿主機開發軟件主要由一些交叉編譯環境、匯編和鏈接工具組成;目標板操作系統選用ARM-LINUX 操作系統;目標板應用程序使用C 代碼進行編寫;HDL 語言用于對FPGA 的功能進行描述。

軟件系統分層示意圖如圖2 所示。在宿主機中,交叉編譯將要在目標板平臺上運行的應用程序代碼和底層硬件驅動程序代碼展開,然后通過宿主機與目標板之間的硬件接口傳遞到目標板中,目標板通過底層硬件驅動程序控制FPGA 模塊中配置的各功能寄存器,從而完成具體的控制任務。本文重點介紹FPGA內部功能模塊的設計及驅動程序接口設計。

圖2 軟件系統分層示意圖

3.1 FPGA 內部關鍵功能模塊設計

FPGA 不擅長對數據進行運算處理,但本系統對每個軸的控制都要進行相應的運算,因此在每個軸的控制模塊設計中盡量不涉及復雜的算法實現,算法部分留給ARM 進行處理。原則上FPGA 僅僅接收經ARM 進行處理過的數據,而后按照ARM 主控單元的處理結果進行處理。

單軸控制模塊框圖如圖3 所示。在每個位置管理單元中都配置了兩個計數器:邏輯位置計數器和實際位置計數器。其中邏輯位置計數器的輸入端接到脈沖發生器的輸出端,其功能是計量從脈沖發生器實際發出的脈沖數量。實位計數器的輸入端接到編碼器的輸出端,其功能是計量從編碼器發出的脈沖個數。邏輯位置寄存器和實際位置寄存器實際上構成一個閉環系統,前者為閉環系統的輸入,后者為閉環系統的輸出。當兩者的誤差范圍不超過某一個限度時,在FPGA中對實時的脈沖發送速率進行調節;當兩者的誤差超過某一個設定的范圍時,FPGA 向ARM 發送一個中斷請求。當某個軸接收到減速信號SD 或者極限到位信號EL 時,在FPGA 內部經過同樣一個中斷發生器模塊向ARM 發送一個中斷。ARM 接收到中斷信號后,開啟運動控制進程,對PID 控制參數進行整定,計算控制量。

圖3 單軸控制模塊設計

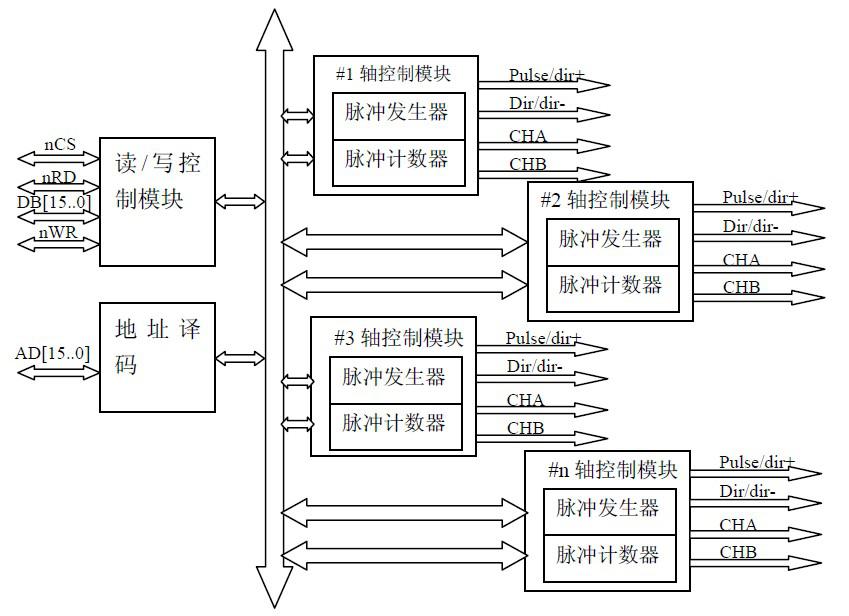

3.2 驅動程序接口設計

在系統設計中,兩片FPGA 作為ARM 的外設,掛在ARM 的外設地址空間。當ARM 要訪問FPGA時,首先要在ARM 中運行包含FPGA 所在地址空間地址的指令,而后ARM 的片選線選中FPGA,FPGA檢測到自己被選中,從而開始檢測地址總線上傳來的ARM 指令所包含的地址數據。根據從ARM 地址線傳來的地址總線上的數據,FPGA 讀取從ARM 數據總線上傳來的數據總線上的數據,而后開始進行相應的動作,從而完成一次控制任務。寄存器是本運動控制系統的基本組成部分之一,ARM 對FPGA 的控制就是通過配置在FPGA 內部的寄存器來實現的。完成配置的FPGA 整體結構如圖4 所示。

圖4 FPGA 內部結構圖

4 控制算法設計與仿真

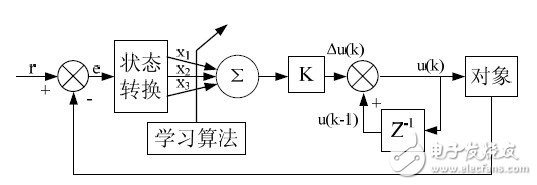

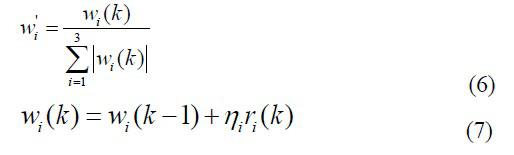

4.1 單神經元自適應PID 控制器設計

單神經元自適應PID 控制器的結構如圖5 所示。

圖5 單神經元自適應PID 控制器

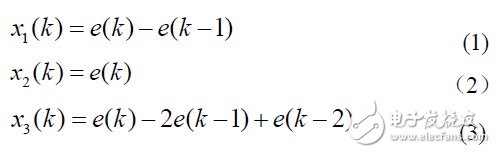

圖5 中,神經元的3 個狀態變量分別為:

單神經元自適應控制器是通過對加權系數的調整來實現自適應、自學習功能,權系數的調整是根據有監督的Hebb 學習規則實現的。

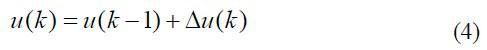

控制器的輸出為:

其中:

式(5)中,w'i為加權系數,可在線修正。加權值的在線學習則采用規范化的學習算法,公式為式(6):

式(7)中ηi(i = I、P、D ), ηI 、ηP 、ηD 分別為積分、比例、微分的學習速率。

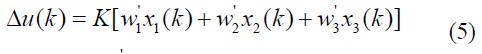

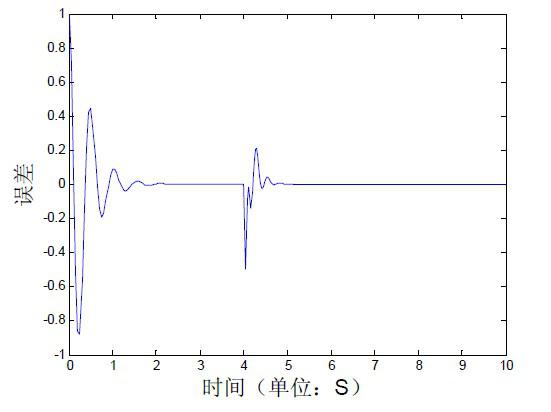

4.2 算法仿真

仿真系統的參數:比例、積分、微分的學習速率分別為 ηP =0.40 , ηI =0.35 , ηD =0.40 ,系統初始誤差量值設置為1,仿真曲線如圖6 所示。從仿真結果可以看出,系統PID 控制參數隨系統的運行在線整定,經整定的PID 參數對系統進行控制,系統的誤差最終趨于0。

圖6 單神經元PID 控制誤差曲線

5 運行結果

5.1 系統位移調試結果

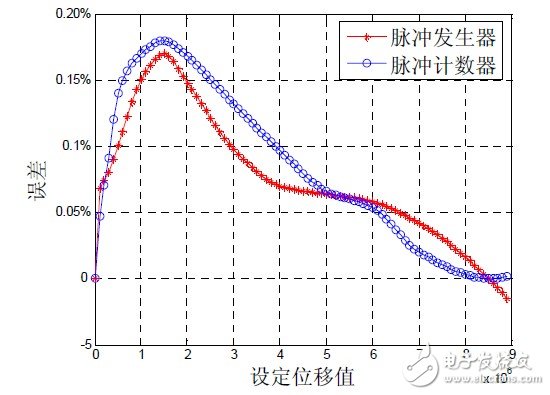

為了測試運動控制系統的位置控制效果,在電機空載時進行了100 次試驗,圖7 所示為在實驗室中測定的電機空載時的位移測試結果曲線圖,各試驗數據均是取100 次實驗數據的平均值。圖7 為各實驗數據的曲線擬合圖。從圖中可以看出,電機空載時脈沖發生器和脈沖計數器的誤差曲線經歷了一個積累的過程,當誤差超過設定值0.18%時單神經元自適應PID控制器開始在線整定PID 控制參數,整定結果使系統的誤差趨于0。

圖7 系統位移調試結果

5.2 系統速度調試結果。

為了測量系統的速度響應結果,系統使用M/T法[7]對速度數據進行測量,M/T 法的計算公式如式(8)所示:

式(8)中f 為基準時鐘頻率;P 為光電編碼器每轉一周產生的脈沖個數;M1 和M2 分別是在相同的時間內對編碼器脈沖和基準時鐘脈沖進行計數的計數值。

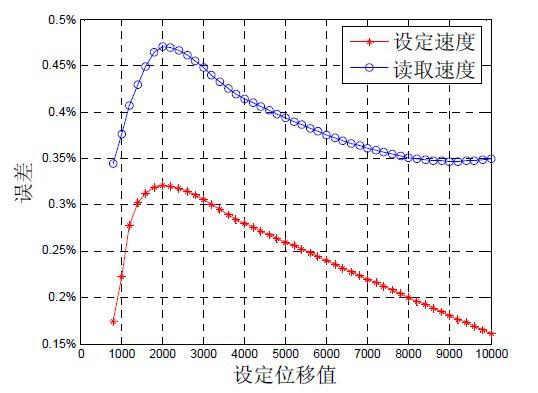

在電機空載時進行了100 次試驗,圖8 所示為在實驗室中測定的電機空載時的速度測試結果,各個參數值均是取100 次實驗數據的平均值。圖8 中設定速度值對應程序運行時在脈沖發生器中設定的分頻系數,驅動器顯示電機轉速對應設定速度時對應的誤差,使用M/T 測得的轉速對應讀取速度時對應的誤差。

圖8 電機空載時速度測試結果

6 結論

采用嵌入式方案設計的運動控制系統不管在體積、成本還是功能方面,較原有的工控機+板卡的結構均有較大的優勢。該系統突破了原有的工業CT 運動控制系統本身固有的一些缺點,采用嵌入式的ARM+FPGA 解決方案進行設計,控制系統內部采用基于單神經元自適應PID 控制器進行設計。系統運行結果證明方案的可行性。為今后進一步研發擁有自主知識產權的基于嵌入式系統的多軸智能運動控制器做了基礎性的探索工作。

-

處理器

+關注

關注

68文章

19178瀏覽量

229201 -

FPGA

+關注

關注

1626文章

21678瀏覽量

602038 -

ARM

+關注

關注

134文章

9057瀏覽量

366881 -

嵌入式

+關注

關注

5072文章

19026瀏覽量

303523

發布評論請先 登錄

相關推薦

利用嵌入式ARM+FPGA實現工業CT運動控制系統設計

利用嵌入式ARM+FPGA實現工業CT運動控制系統設計

評論