引言

隨著芯片規模的越來越大、資源的越來越豐富, 芯片的設計復雜度也大大增加。事實上, 在芯片設計完成后, 有時還需要根據情況改變一些控制, 這在使用過程中會經常遇到。這時候如果再對芯片設計進行改變將是很不可取的, 因為需要設計人員參與這種改變, 這無論是對設計者還是用戶都是不能接受的。于是就有必要讓這種可以改變的簡單控制在芯片設計時就存在, 而且同時還應該使這種改變相對容易, 比較通用, 并且與芯片的其它設計部分盡量不相關。為了滿足上述的要求, 在FPGA中嵌入一個IP核是比較理想的選擇, 而這個即通用又控制簡單的IP核最好選擇8051微處理器。

在FPGA中植入8051后, 還可在上面實現簡單的TCP/IP協議, 以支持遠程訪問或進行遠程調試, 這只是在嵌入FPGA的8051上的一個應用。為了保證用戶能夠對8051實現不同的控制操作,設計時也可以采用一個外部flash對8051進行加載, 這樣, 用戶只需要將編譯好的匯編語言代碼加到flash就可以控制8051的工作, 而此時用戶完全不需要對FPGA進行操作就能實現簡單的控制,而這需要的僅僅只是keil的編譯環境。

1 IP核8051的FPGA實現

現在有許多免費的8051核可以利用, 這些核都可通過硬件描述語言來實現, 并且基本上都可綜合, 也就是直接拿來就能用, 需要的只是根據自身的具體需求做一些簡單修改即可。總的說來, IP核8051的移植是比較簡單的。

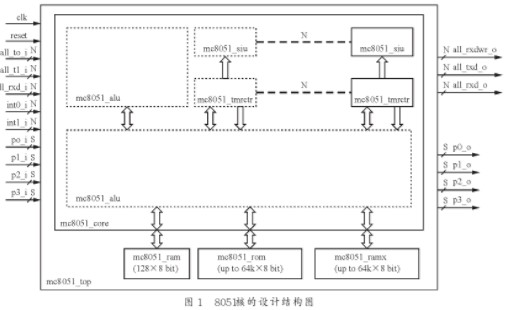

本系統的設計與實現可以采用oregano system的mc8051內核, 并且加入定時計數的和串口模塊, 8051單片機的設計結構框圖如圖1所示。

在8051核的FPGA設計中, 完全可以實現包括計時/計數、中斷、串口、數據及程序存儲器、特殊寄存器、布爾處理的位處理機等的所有功能, 而且兼容所有指令, 只是在具體的移植過程中做一些改變而已。

這種方法對程序存儲器不再做內外之分, 因為FPGA內部存儲容量已經能夠滿足要求, 同時將程序存儲器的容量擴大了一倍 (變為8KB), 以滿足大程序的容量需求; 為了讓8051更為強大且更具有通用性, 可將數據存儲器RAM的容量擴大一倍, 變為256字節。可以看出, 在設計過程中將8051的功能也進行了加強, 但是并不影響對它的控制, 僅僅是在硬件上對存儲器的容量進行了擴大, 而這種擴大只是改變了地址線的寬度, 完全不影響111條指令的正確執行。對用戶來說這只是可以使用的內部RAM增加了, 控制并沒有任何改變。當然, 在資源比較緊張, 而且程序容量比較小時, 也可以將存儲器的容量改小, 這種改變也相當方便, 只需要改變地址線的寬度就能達到目的。由此可見, 設計時完全可以根據需要改變IP核的設計, 而不局限于8051。

雖然整個8051IP核能正確執行所有指令, 并能實現串口、計時器及中斷控制, 且整個IP的核工作時鐘也在20 MHz以上, 但是, 由于這時候的所有指令周期并不與真實的8051完全一致, IP核中有的指令需要比真正的8051多執行幾個周期才能完成, 這就使得分析IP核的工作時鐘復雜起來了, 因為相對于真正的8051不能有一個精確的工作時鐘對比。但是經過分析仍然可以認為, IP核應該可以工作在15 MHz左右, 也就是比真實的8051快了15倍左右。這對于芯片整體來說, 其速度可能相對較低, 但是由于這部分與芯片其它部分的邏輯相關性極小, 所以并不會影響芯片的整體性能, 而對于一些簡單控制來說, 這個速度還是能夠滿足要求的。

2 UIP協議棧

2.1 UIP簡介

在FPGA中實現TCP/IP協議的主要目的是為了滿足設計人員對芯片的遠程調試。而滿足這種要求實際上并不需要很強大和快速的傳輸功能。功能過于強大將會占用過多的資源, 而且實際上, 很多功能并沒有實際作用; 同時也不需要很快的傳輸速度。畢竟對于一個芯片的設計來說,無論是設計文檔或是設計程序, 容量都是非常有限的。綜合考慮, 則應選擇一個實現簡單、占用資源少, 但能夠比較穩定地進行數據傳輸的協議, 為此, 本文選擇了相對簡單的UIP協議棧,而放棄了功能比較強大的LWIP協議棧。選擇UIP還有一個好處, 就是這個協議棧是專門針對單片機等微控制器設計的TCP/IP協議棧, 它能夠利用嵌入的IP核8051來實現TCP/IP協議, 而不再需要額外的邏輯單元。

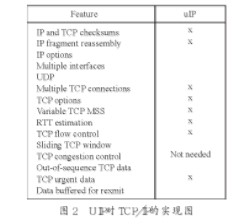

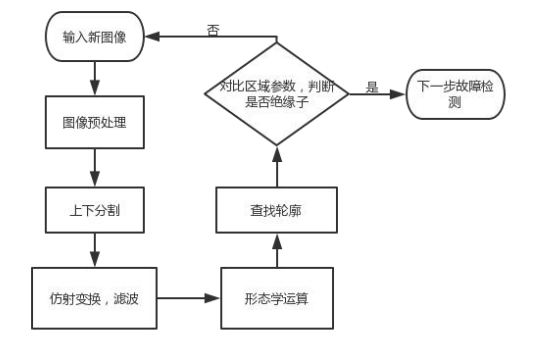

UIP的特點是代碼量和數據量都比較小, 因而可以為存儲器比較緊張的地方提供合適的實現方案, 包括TCP/IP所需的最小實現方案和只包含TCP、IP、ICMP (ping) 以及簡單的UDP協議, 其具體的實現方法如圖2所示, 圖2中, 帶“×”的表示已經實現。

2.2 UIP協議棧的實現方法

通過UIP可實現TCP/IP協議集的四個基本協議, 包括ARP地址解析協議、IP網際互聯協議,ICMP網絡控制報文協議和TCP傳輸控制協議。為了在8位、16位處理器上應用, UIP協議棧在實現各層協議時采用有針對性的方法來保證代碼大小和存儲器使用量最小。

實現ARP地址解析協議時, 為節省存儲器,ARP應答包可直接覆蓋ARP請求包; 而在實現IP網絡協議時, 則對原協議進行了極大的簡化, 并沒有實現分片和重組; 當實現ICMP網絡控制報文協議時, 只需實現echo (回響) 服務。UIP在生成回響報文時, 并不重新分配存儲器空間, 而是直接修改echo請求報文來生成回響報文。設計時可將ICMP類型字段從“echo”改變成 “echo re-ply”類型, 并重新計算校驗和修改校驗和字段。UIP里的TCP沒有實現發送和接收數據的滑動窗口。每個TCP連接的狀態均由uip_conn結構保存。uip_conn結構包括當地和遠端的TCP端口編號、遠程主機的IP地址、重發時間值、上一段重發的編號以及連 接段的最大尺寸等信息。uip_conn結構數組可用于保存所有的連接, 數組的大小等于可支持同時連接的最大數量。為了減少儲存器的使用量, 在處理重發時, UIP并不緩存發送的數據包, 而是由應用程序在需要重發時重新生成發送的數據。

2.3 UIP協議棧的接口

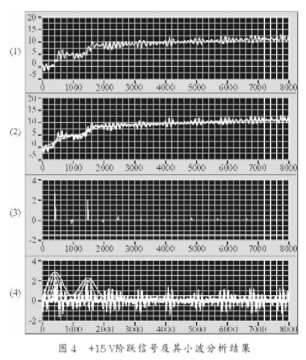

為了UIP協議棧能具有最大的通用性, 在實現時可將底層硬件驅動和頂層應用層之外的所有協議集“打包”在一個“庫”里。協議棧通過接口與底層硬件和頂層應用進行通信。通過這種方式可使uIP具有極高的通用性和獨立性, 以便移植到不同的系統和方便地實現不同的應用, 很好的體現TCP/IP協議平臺無關性的特點。UIP協議棧與系統底層和應用程序之間的接口如圖3所示。圖中, 各接口之間都是由一系列函數來實現的。

3 UIP協議棧在IP核8051上的實現

3.1 UIP協議棧在IP核8051上的移植

由于UIP協議棧是專門針對微處理器編寫的,所以移植也是非常的方便, 但需注意以下幾點:

(1) 協議棧是用C語言編寫的, 故在移植時需要再加上兩個頭文件, 一個是8051的頭文件, 另一個是8051的硬件初始化頭文件;

(2) 通過keil c編譯器編譯時, 在選器件時需要注意, 只有選取數據寄存器為256個字節才能順利通過編譯, 這也是為什么前面8051IP核的數據存儲器RAM需要擴展至256個字節的原因。不對RAM進行擴展, 就會出現“不能寫B9地址”的錯誤, 因為在沒有對RAM擴展前, 根本不存在B9地址;

(3) 將軟件keil編譯生成的hex文件送入到8051的程序存儲器, 即可在IP核8051上實現簡單的TCP/IP協議。這在軟件測試時, 與實際工作將有所不同。軟件測試時需要將hex文件作為程序存儲器的初始化輸入, 即在EDA軟件編譯8051時, 將程序存儲器的初始化文件mif的路徑設置為hex所在的路徑, 在完成綜合布線后, hex文件的內容就進入了程序存儲器。這樣, 仿真時就能在8051IP上實現TCP/IP協議了。

3.2 UIP的工作流程

TCP/IP協議在嵌入到FPGA的IP核8051上的工作流程, 實際上也是簡化后的TCP/IP協議的工作流程, 這跟正式的TCP/IP協議有所不同。下面的工作流程以輸入一個同步幀 (即: 三向握手的第一次握手) 為例。對于8051實現的UIP來說, 它屬于被動建立連接, 其正確的輸出結果應該是三向握手的第二次握手, 送出一個確認同步幀是所期望的結果。

下面簡單介紹UIP的整個工作流程:

(1) 在P0端口有數據前, 讀取數據函數并反復執行, 以對P0端口進行監視 (此種情況只是在測試時, 實際工作中物理層通過控制信號通知讀數函數P0口是否有數據);

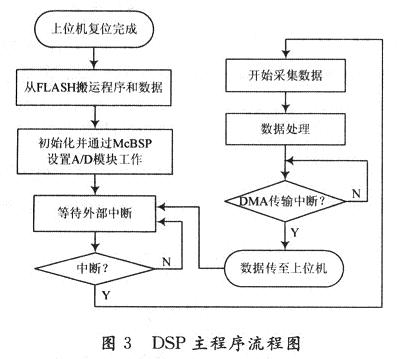

(2) 為信號的第8級分解小波模極大值圖;

(3) 為信號各級 (共9級) 的高頻分量即小波系數。

由圖4可以看出, 該故障信號分析儀能有效采集實時故障信號, 并可在對信號經過小波分析后有效的提取故障特征, 而且故障點定位明顯。

5 結束語

該便攜式接觸網故障信號分析儀采用圖形化程序設計語言LabVIEW開發設計, 可實現數據的高速實時采集、在線分析、自動存儲、顯示等功能。高速數字化儀NI PXI- 5112卡采樣速度高、性能穩定可靠, 適宜對高速變化信號的實時監測。將軟件安裝在PXI- 1042工控機上, 具有體積小、抗干擾能力強、攜帶方便等特點, 同時具有故障性質判斷、故障定位功能。該系統目前已經在石家莊變電所現場運行, 效果良好。

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601902 -

芯片

+關注

關注

454文章

50430瀏覽量

421872 -

微處理器

+關注

關注

11文章

2247瀏覽量

82323

發布評論請先 登錄

相關推薦

200km時速電氣化鐵路接觸網施工工法 (YJGF61—2000)

接觸網應力實時檢測及斷線事故預警系統

接觸網智能CAD系統的研究和實現

基于DSP技術的接觸網動態參數檢測系統

基于電路模型法的接觸網電流分布研究

基于GPRS及Web服務器技術實現接觸網補償裝置遠程監控系統設計

接觸網的分類

使用機器學習實現接觸網圖像檢測的研究論文免費下載

為什么可以通過設計和零接觸網絡實現AI

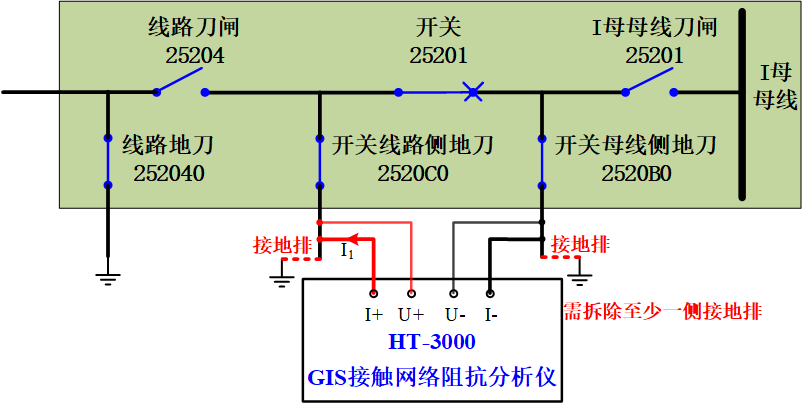

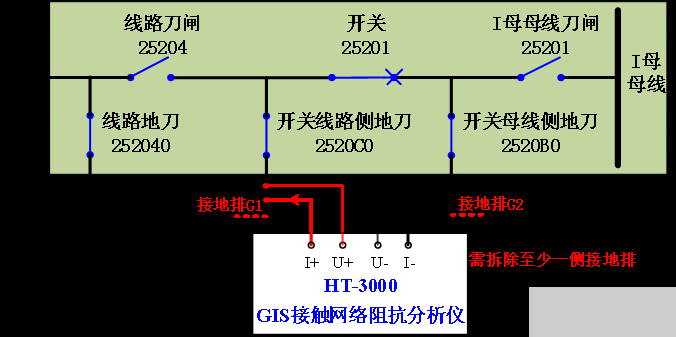

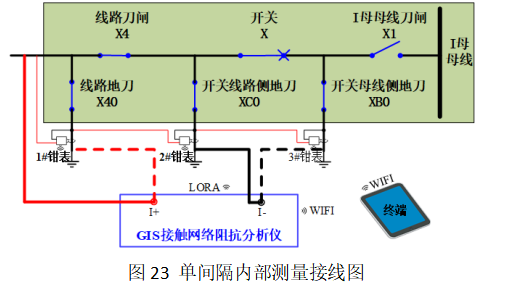

GIS接觸網絡阻抗分析儀接線圖

GIS接觸網絡阻抗分析儀操作方法

GIS接觸網絡阻抗分析儀測試步驟——每日了解電力知識

在植入8051微處理器的FPGA芯片中實現接觸網故障信號分析儀的設計

在植入8051微處理器的FPGA芯片中實現接觸網故障信號分析儀的設計

評論