隨著現代技術的發展,作為現代高科技代表的航天工程,對星載計算機的依賴程度也越來越高。由于宇宙中存在著大量的帶電粒子,星載計算機硬件系統的電子器件會受到電磁場的輻射和重粒子的沖擊,其相互作用產生各種效應,其中單粒子反轉(SEU)效應的影響尤為明顯,它將引起衛星工作的異常或故障。SEU是由空間輻射環境導致的,重離子運動徑跡周圍產生的電荷被靈敏電極收集,形成瞬態電流,觸發邏輯電路,導致邏輯狀態翻轉,引起誤操作,使得星載計算機上的數據可能出現小概率錯誤,其主要發生于存儲器件和邏輯電路中,導致存儲器單元的內容發生翻轉(1變為0或O變為1)。這種錯誤若不及時進行糾正,將會影響計算機系統的運行和關鍵數據的正確性,造成程序運行不穩定和設備狀態改變。利用糾錯編碼進行檢糾錯電路設計是一種使星載計算機中SRAM具備抗SEU能力的有效方法,它能夠降低數據出錯的概率,保障計算機系統的正常運行。

1 糾錯原理

漢明碼(Hamming Code)是由Richard Hamming于1950年提出的,屬于線性分組碼的范疇,其基本原理是將信息碼元與監督碼元通過線性方程式聯系起來的,每一個監督位被編在傳輸碼字的特定比特位置上。系統對于錯誤的數位無論是原有信息位中的,還是附加監督位中的都能把它分離出來。(n,k)線性分組碼的生成矩陣G和校驗矩陣H分別為n×k和n×(n-k)維矩陣,其中校驗矩陣H決定信息位與校驗位的關系,在編碼和譯碼中都要用到。線性碼的最小碼距為d,即校驗矩陣H中任意d-1列線性無關,它與碼的糾錯能力有以下關系:

(1)檢測P個隨機錯誤,要求d≥e+1;

(2)糾t個隨機錯誤,要求d≥2t+1;

(3)糾t個隨機錯誤,同時檢測e(e≥t+1)個隨機錯誤,要求d≥e+t+1。

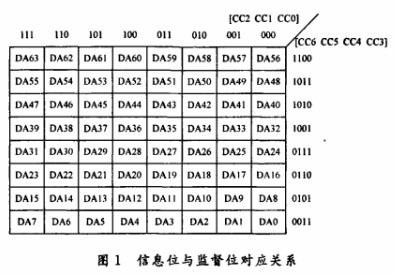

作為一種典型的線性分組碼,標準漢明碼的碼長n=2m-1,監督位數為m,信息位數為k=n-m,最小碼距d=3,因此它的糾錯能力t=1,是一種常用糾單個位錯誤的編碼方式。還可以根據需要對標準漢明碼進行擴展,增加1個校驗位對所有位進行監測,就得到擴展漢明碼。1個(n,k)漢明碼經過擴展以后,就變成了(n+1,k)漢明碼。擴展以后的漢明碼d=4,t=2,e=1,可以糾正單個位錯誤,并檢測出雙位的錯誤。對64位的數據進行糾錯設計,滿足信息位數大于64要求的最短的標準漢明碼為n=26-1時的(127,120)碼,它具有7個監督校驗位。根據漢明碼信息位刪減后其糾錯能力較之前不會降低的特性,將該碼的信息位縮短為64位,使用了(71,64)的刪減漢明碼。這里設計了一種7個校驗位同64個信息位的對應計算關系如圖1所示。

圖1中DA0~DA63為信息位;CC0~CC6為監督校驗位。其中CCO是所有位于編號末位數為1列中信息位數據的奇偶校驗計算結果。與之類似,CCl對應于所有位于編號次低位數為1列中的信息位。同理,CC3~CC6分別對應了行號各位數為1行中的信息位數據。通過這個對應關系表,可以得出整個漢明碼的生成公式:

M=DG

式中:M為生成的(71,64)漢明碼矩陣,每個行向量是一組漢明碼;D為信息位數據矩陣行,64個信息位組成一個行向量;G成為漢明碼生成矩陣,可以根據上述的對應計算關系得出來。

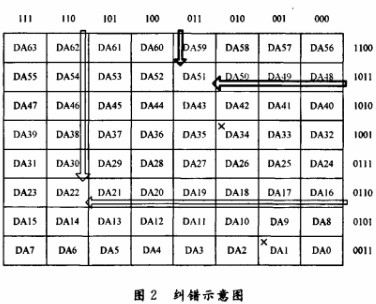

當執行糾錯功能時,需要同時讀取數據位和監督校驗位,并且對所讀取的數據位按照校驗位的生成算法重新進行1次校驗位的生成(可以用NCC0~NCC6來表示),通過CC0~CC6和NCCO~NCC6的比對來進行檢錯糾錯運算。如果發生1位數據翻轉錯誤,則新生成的校驗位NCC中會有若干位同原先的CC校驗位相異,通過相異的位可以對數據進行糾錯。假設目前檢測出CCl,CC2,CC4,CC5這4個校驗位同新生成的NCC中對應位的異或運算結果為1,如圖2中細箭頭所示。

CCl校驗位相異對應出錯數據位列號倒數第二位為1;CC2對應列號倒數第3位為1,可以推出錯誤數據位的列號為110,同理行號相關的幾個校驗位中CC4,CC5出現相異可以推出錯誤數據位的行號為0110,由此可以知道出錯的數據位是DA22,再對確認出錯的數據位取反就實現了糾正1位錯誤的功能。而如果出現2位錯誤,比如數據位DAl和DA34同時出錯,如圖2中所示,這會引起新老校驗位中的CC0,CCl,CC3,CC4,CC6同時出現相異。這時如果還按照上述糾正1位錯誤時的算法,就會推出出錯數據位的行號為1011列號為011,這樣,就會認為是數據為DA51發生了翻轉,從而產生錯誤的檢糾錯結果,如圖2中粗箭頭所示。以前的測試數據表明,若在近地軌道中,SRAM存儲器中的每一個存儲數據位一天之內發生SEU概率約是10-7(位·天),則可以推導出這個SRAM中1組64位的數據,在一天時間內有2位同時出現錯誤的可能性約為10-10(次·天),在南大西洋輻射異常區和太陽活動高峰期,這種情況的發生率可能還會提高1~2個數量級。

為了避免在發生雙位元錯誤時出現錯檢錯糾的情況,需要增加1個校驗位CC7,它是所有數據位的奇偶校驗結果,即CC7=DA0⊕DAl⊕DA2⊕DA3⊕…⊕DA63。這樣在每次出現1個數據位錯誤時,新生成的NCC7也都會與先前的值相異,而當數據位中有2個存儲單元出錯,其他校驗位會檢測有錯誤出現,但NCC7不會發生變化,NCC7⊕CC7=0,這時就可以判斷出有雙位錯誤,從而使系統實現了檢測雙位錯誤的功能。

2 設計實現

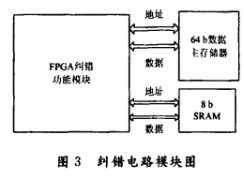

將所有與主存儲器中數據一一對應的校驗位(CCl~CC8)存儲在另一個獨立的8位SRAM中,系統的硬件結構如圖3所示。

存儲校驗位的8位數據SRAM2同樣遇到出現SEU效應得可能,通過分析可以知道,SRAM2出現1位數據翻轉時,只有對應的一位數值與通過數據位新生成的校驗位數值相異,而其他的7個校驗位數據都沒有變化,此時對對應的校驗位取反就實現了糾錯功能。對于出現雙位元錯誤的可能,通過理論分析,可以知道一組8位的校驗數據在一天中出現這種情況的概率約為7×10-13。,相比于主存儲器而言降低了兩三個數量級,暫時可以不予考慮。

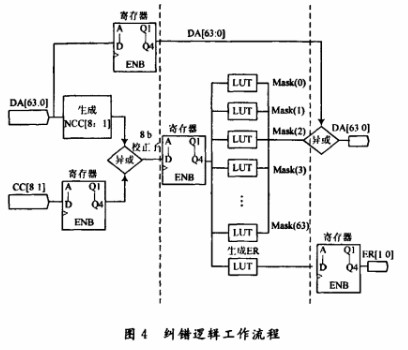

FPGA的檢糾錯邏輯設計采用VHDL語言實現。設計使主存儲器SRAMl中的64位數據新生成的NCC[7:0]與SRAM2中的7位校驗位CC[7:0]一起經過異或運算,生成8位的校正子,其中前7位就對應于前述定位錯誤數據的行號和列號的值,第8位用于判斷是否出現雙位元錯誤。8位校驗子的值可以求出1個64位糾錯掩碼(Mask),用以校正單位元錯誤。如果未檢測到錯誤,此掩碼的所有位都為零。如果檢測到單位元錯誤,相應掩碼會屏蔽除錯誤位之外的所有位。下一階段,使用原始數據對此掩碼進行異或運算。最終,錯誤位被反轉(或校正)至正確狀態。如果檢測到雙位元錯誤,所有掩碼位也都為零。使用1個雙位的數組(ER[1,O])用于報告檢測的錯誤類型(“OO”表示無錯、“01”表示單位元錯誤、“10”表示雙位錯誤、“11”表示無法判斷的多位錯誤)。整個糾錯邏輯的工作過程如圖4所示。生成錯誤類型報告數組和相應的校正掩碼的工作都在同一時鐘周期內完成,體現了采用FPGA進行并行處理的獨特優勢。

3 結 語

對綜合后進行仿真的結果進行分析,期間人為地加入1位、2位、3位隨機分布的數據位錯誤,該系統能夠在2個系統時鐘周期內對1位錯誤的情況成功地檢測并予以糾正;對2位和3位錯誤情況也都進行了正確的類別判定。仿真結果表明,設計的系統比較理想,能滿足設計要求。

然而對于整個星載計算機系統而言,空間中的應用環境非常苛刻,輻射和粒子沖擊造成的影響絕不僅只在SRAM上,對FPGA,DSP等芯片同樣也會帶來各種復雜的影響,要消除這些影響,確保計算機系統可靠的工作,還需要廣大科技工作者進行大量的工作。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601863 -

存儲器

+關注

關注

38文章

7452瀏覽量

163606 -

計算機

+關注

關注

19文章

7421瀏覽量

87718

發布評論請先 登錄

相關推薦

fpga時序邏輯電路的分析和設計

基于VHDL邏輯電路設計與應用

采用CPLD/FPGA的VHDL語言電路優化原理設計

數字邏輯電路教學中的C語言描述和應用

基于FPGA的檢糾錯邏輯算法的實現

基于VHDL語言的FPGA檢糾錯邏輯電路的設計

基于VHDL語言的FPGA檢糾錯邏輯電路的設計

評論