1 引言

交錯正交相移鍵控(OQPSK)是繼QPSK之后發展起來的一種恒包絡數字調制技術,是QPSK的一種改進形式,也稱為偏移四相相移鍵控(offset-QPSK),有時又稱為參差四相相移鍵控(SQPSK)或者雙二相相移鍵控(Double-QPSK)等。它和QPSK有同樣的相位關系,也是把輸入碼流分成兩路,然后進行正交調制。與普通的QPSK比較,交錯正交相移鍵控的同相與正交兩支路的數據流在時間上相互錯開了半個碼元周期,而不像QPSK那樣I、Q兩個數據流在時間上是一致的(即碼元的沿是對齊的)。OQPSK信號中,I(同相)、Q(正交)兩個數據流,每次只有其中一個可能發生極性轉換。所以每當一個新的輸入比特進入調制器的I或Q信道時,輸出的OQPSK信號中只有0°、±90°三個相位跳變值,而根本不可能出現180°相位跳變。所以頻帶受限OQPSK的信號包絡起伏比頻帶受限QPSK的信號小,經限幅放大后頻帶展寬得少,故OQPSK性能優于QPSK。

本設計中OQPSK解調器接收端接收的信號是10.7MHz已調信號,按照軟件無線電的設計思想,先進行計算機的模擬仿真,充分利用FPGA的特點,成功實現了對的10.7MHz的OQPSK信號差分解調。解調器的技術指標為:解調器輸出碼:256 kb/s 、TTL電平;解調器輸出時鐘:256 KHz 、占空比50%。

2解調器的設計與FPGA實現

2.1總體方案設計

解調器前端的載波恢復部分采用分離元件實現,這里不做詳細介紹,大家可以參考經典鎖相環電路進行設計。位時鐘信號可以由I路信號提取也可以由Q路信號來提取,本設計中由I路信號來提取。并串變換之后就完成了信號的解調。后邊的HDB3編碼是為了便于傳輸和其他處理,比如解調后的信號送計算機處理等等。

2.2位時鐘恢復電路的設計

位時鐘恢復電路由高穩定度振蕩器(晶振)、分頻器、相位比較器和控制器所組成。其中,控制器包括扣除門、附加門和“或門”。高穩定度振蕩器產生的信號經整形電路變成周期性脈沖,然后經控制器再送入分頻器,輸出位同步脈沖序列。若接收碼元的速率為F(波特),則要求位同步脈沖的重復速率也為F(赫)。這里,晶體的振蕩頻率設計在nF(赫),由晶振輸出經整形得到重復頻率為nF(赫)的窄脈沖,經扣除門、或門并n次分頻后,就可得重復頻率為F(赫)的位同步信號。如果接收端晶振輸出經n次分頻后,不能準確地和收到的碼元同頻同相,這時就要根據相位比較器輸出的誤差信號,通過控制器對分頻器進行調整。調整的原理是當分頻器輸出的位同步脈沖超前于接收碼元的相位時,相位比較器送出一超前脈沖,加到扣除門(常開)的禁止端,扣除一個a路脈沖,這樣,分頻器輸出脈沖的相位就推后1/n周期(3600/n);若分頻器輸出的位同步脈沖相位滯后于接收碼元的相位,晶振的輸出整形后除a路脈沖加于扣除門外,同時還有與a路相位相差1800的b路脈沖序列加于附加門。附加門在不調整時是封閉的,對分頻器的工作不起作用。當位同步脈沖相位滯后時,相位比較器送出一滯后脈沖,加于附加門,使b路輸出的一個脈沖通過“或門”,插入在原a路脈沖之間,使分頻器的輸入端添加了一個脈沖。于是,分頻器的輸出相位就提前1/n周期。經這樣的反復調整相位,即實現了位同步。

接收碼元的相位可以從基帶信號的過零點提取(它代表碼元的起始相位),而對數字信號進行微分就可獲得過零點的信息。其中codein輸入端輸入的是I路信號,clkin輸入的是32.0867M的時鐘信號,Clkout輸出同步信號。FredivN分頻器的分頻倍數為64倍。

其中codein輸入端輸入的是I路信號,clkin輸入的是32.0867M的時鐘信號,Clkout輸出同步信號。FredivN分頻器的分頻倍數為64倍。

2.3 差分譯碼電路的設計

差分譯碼完成的功能就是把相對碼變為絕對碼。絕對碼是以基帶信號碼元的電平直接表示數字信息。如高電平表示“1”,低電平表示“0”;相對碼(差分碼)是用基帶信號碼元的電平相對前一碼元的電平有無變化來表示數字信息的,假若相對電平有跳變表示“1”,無跳變表示“0”,由于初始參考電平有兩種可能,因此相對碼也有兩種波形,但是不論是那種形式解碼方式都是一樣的。現假設{an}和{bn}分別表示絕對碼和相對碼序列,則差分譯碼器的功能可表示為:an =bn bn-1,其中 表示模二加。

其中b為相對碼,a為絕對碼,clkin為為同步信號時鐘。

2.4 并串變換電路的設計

A、B兩路128kb/s的并行輸入信號分別接到數據選擇器74153的兩個數據輸入端,其中B路信號落后A路信號半個碼元周期。256KHz的位同步信號經分頻為128KHz作為數據選擇器的一路地址選擇信號,另一路地址選擇信號接地。這樣數據選擇器輸出為A、B兩路信號的并路信號,即A1、B1、A2、B2、A3、B3……,速率為256kb/s。

2.5 HDB3編碼器的設計

2.5.1編碼規則

HDB3碼是AMI碼的改進型,稱為三階高密度雙極性碼.他克服了AMI碼的長連0串現象.

HDB3碼的編碼規則:

① 將消息代碼變換成AMI碼;

② 檢查AMI碼中的連0情況,當無4個或4個以上連0串時,則保持AMI碼的形式不變;

若出現4個或4個以上連0串時,則將1后的第四個0變為與前一非0符號(+1或-1)同極性的符號,用V表示(+1記為+V,-1記為-V).

③ 檢查相鄰V符號間的非0符號的個數是否為偶數,若為偶數,則再當前的V符號的前

一非0符號后的第一個0變為+B或-b符號,且b的極性與前一非0符號的極性相反,并使后面的非0符號從V符號開始再交替變化.

2.5.2建模思想

本設計沒有象其他設計那樣將插V補B分開實現,而是通過變量的設置將兩個功能一起實行。

首先判斷前面已存在非0符號的極性,用以判斷后面非0符號的極性。同時通過變量flag的狀態判斷前面是否已經插V,若已經插V則再通過變量H的狀態判斷兩個V之間的非0符號的個數,為偶數且后面連續輸入4個以上連0時則插B,為奇數時則不插B。若尚未插V則不補B。插V和插B的功能由兩個3位移位寄存器的強制輸出實現,當不需要插V和B的時候則移位寄存器順序輸出。

本設計在實現過程中將插入的V和B根據需要直接由+1和-1表示,省去了其他程序中先插入V和B然后再判斷極性的過程。輸出部分由兩路表示,當aout和bout分別為0和1時表示輸出-1,為1和0時表示輸出+1,為0和0時表示輸出0。限于篇幅這里就不給出程序清單。

3 部分試驗結果

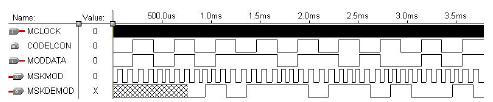

系統加入調制部分后的仿真結果如下圖7所示。其中indata為調制器的輸入信號,DATAOUT為解調輸出,outa2和outb2為DATAOUT的HDB3編碼結果。OUTCLK為最后的輸出時鐘。

4 結論

隨著FPGA技術的發展,大規模FPGA的容量在不斷增大,價格不斷下降,這使得集成復雜的算法成為可能。用它將實現連續相位OQPSK解調所需的大部分功能封裝于其中,將有利于通信系統實現小型化和集成化,并可提高系統的穩定性。另外,由于FPGA器件具有可編程性,可以很方便地進行系統升級和修改,以滿足不同應用場合的需要。憂無線SOC開發平臺豪華的單片機開發系統S3C44B0 ARM7 開發板無憂S3C2410 ARM9開發板單片機以太網開發板Mini ARM Debugger無憂單片機實驗開發板無憂單片機學習板 無憂無線nRF-9E5模塊。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602031 -

解調器

+關注

關注

0文章

285瀏覽量

25800 -

計算機

+關注

關注

19文章

7430瀏覽量

87733

發布評論請先 登錄

相關推薦

解調器

LoRa?調制解調器相關設計操作

一種基于FPGA的全數字短波解調器設計

全數字QAM解調器方案采用了載波相位和符號定時的聯合估計環——基于FPGA的同步電路設計與實現研究 精選資料分享

基于FPGA的OQPSK解調器的設計與實現

一種全數字BPSK解調器的設計與FPGA實現

基于FPGA的MSK調制解調器設計與應用

一種全數字BPSK解調器的設計與FPGA實現

基于FPGA的MSK調制解調器設計與應用

基于FPGA的全新數字化PCM中頻解調器設計

基于FPGA的BPSK調制與解調器設計

采用FPGA技術如何設計OQPSK解調器

采用FPGA技術如何設計OQPSK解調器

評論