1 引言

多年來CCD 器件以體積小、重量輕、功耗小、工作電壓低和抗燒毀等優點以及在分辨率、動態范圍、靈敏度、實時傳輸、自掃描等特性,廣泛地應用于攝像器材、氣象、航天航空、軍事、醫療以及工業檢測等眾多領域。

在對某多通道高速CCD相機輸出圖像信號的采集系統設計過程當中,我們需要對此系統在正式使用之前進行調試,來測試它能否正常工作。本文利用CPLD和LVDS嚴格對CCD相機的輸出接口進行了模擬,并且以LVDS方式輸出圖像信號。

2 相機系統輸出接口信號及Camera link 接口

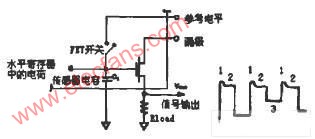

此CCD 相機最終的輸出信號符合camera link 接口標準,每個通道輸出3072個像元后,接著輸出1024個零電平像元,數據采用LVDS差分輸出,每通道的輸出信號包括:控制信號:像元時鐘DCLK,行同步信號LVAL和外觸發信號DTRG;數字圖像信號(8位并行輸出)DATA。各信號波形大致如圖1 所示:

圖1

· DCLK像元時鐘頻率為31MHz,由62MHz晶振產生后二分頻得到。以LVDS信號輸出。

·&nb

sp; 行同步信號LVAL在輸出3072個像元和1024個零電平像元時,LVAL為低電平,在兩個有效行中間會跳變幾個無效的像素點,跳變無效像素點時,LVAL為高電平。跳過的像素點的數目未定,初步設為固定4個像素。以LVDS信號輸出。

· 外觸發信號DTRG是用來觸發采集卡的工作,它與LVAL信號下降沿對齊,高電平寬度為像元時鐘一個周期的寬度。

為提高傳輸效率以及降低傳輸成本,CCD相機將以上圖像信號按Camera Link 標準轉換成低電平差分信號(LVDS)輸出。系統采用與CCD 相機相匹配的National semiconductor芯片組DS90C031W/ML 來完成TTL電平信號和LDVS信號之間的轉換,轉換接口芯片如圖2 所示,一個接口轉換芯片可以將4個信號轉換成4對符合TIA/EIA-644 標準的LVDS 數據流。另外還有兩個使能端,在工作時,EN接低電平, 接高電平。此芯片的最大傳輸速度可達77.7MHz,供電電壓為+5V,符合系統需要。最后輸出信號接到圖像采集系統的輸入端。在本文的設計當中,只用到驅動芯片,接收芯片放在圖像采集系統電路中。

3硬件結構

本設計的硬件電路主要由三部分組成,結構框圖如圖3所示。包括晶振電路、

CPLD、輸出接口(9片DS90C031)。整個電路的核心部分是CPLD,采用ALTERA公司的MAX7000S系列中的EPM7128SLC84-15芯片。它除了產生控制信號外,還要模擬一個灰度圖象的數據源。62MHz晶振用來產生CPLD工作所需要的時鐘。DSC90C031用來把CPLD產生的圖像信號和控制信號(TTL信號)轉化成LVDS信號,并輸出。其中每兩片能產生一個通道的8位的圖像輸出信號,共有4個通道,第9片用來轉換控制信號并輸出。

在電路設計過程中,為了提高系統的可靠性,要注意以下問題:1、CPLD器件的每個供電電壓管腳都要外接0.1μ電容來進行濾波。CPLD輸出信號也要進行濾波之后再接到DSC90C031。2、在輸出端,要使用終端電阻實現對差分傳輸線的最大匹配,阻值一般在90——130?之間,系統也需要此終端電阻來產生正常工作的差分電壓。必要時也可使用2個阻值各為50?的電阻,并在中間通過一個電容接地,以濾去共模噪聲。

4 CPLD程序設計

因為考慮到設計后期還要在CPLD前端加單片機對圖像信號的變化進行各種控制,所以要用到大約50個I/O口的操作,所以選用了ALTERA公司的MAX7000S系列中的EPM7128SLC84-15芯片,該芯片共有84個引腳,內部集成了6000門,其中典型可用門為2500個,有128個邏輯單元,60個可用I/O口,可單獨配置為輸入、輸出及雙向工作方式,2個全局時鐘及一個全局使能端和一個全局清除端。它支持多電壓工作,其傳輸延時為7.5ns,最高工作頻率高達125MHz。我們采用ALTERA公司的第三代開發軟件Max plus II進行仿真、綜合和下載。

整個程序分三個模塊:u1,u2,u3,其中u1是分頻模塊,用4輸出計數器對輸入的62M主時鐘(mclk)進行2分頻,u2是圖像數據產生模塊,用8位的計數器來產生灰度圖象數據。u3模塊是利用13位的計數器來產生控制信號,嚴格按照要求的時序關系,分別產生像元時鐘(DCLK)、行同步信號(LVAL)、外觸發信號(DTRG)。部分源程序如下:

begin

u1:fenpin port map(mclk,clr0,set,clk); //引用分頻模塊

u2:count8 port map(clk,clr1,set,countout8);//引用8位計數器

u3:count13 port map (clk,clr2,set,countout13);//引用13位計數器

set<='1';

clr1<='0';

dclk<=clk;

process(clk)

begin

if(clk'event and clk='1')then

if (countout13>=4096 and countout13<=4099)then

lval<='1';

data<=countout8;

else

lval<='0';

end if;

if(countout13=4099)then

dtrg<='1';

clr2<='1';

else

dtrg<='0';

clr2<='0';

end if;

if(countout13>=0 and countout13<=3071)then

data<=countout8;//輸出有效像元

end if;

if (countout13>=3072 and countout13<=4095)then

data<=0;//輸出零像元

end if;

end if;

end process;

end rtl;

時序仿真圖如下圖所示:

5總結

編譯仿真通過后,在頂層用原理圖進行綜合實現,然后燒入芯片進行實驗,并根據實際運行情況,對設計進行改進。如根據實際器件的延時特性,在設計中某些地方插入適當的延遲單元以保證各時延一致。

根據本文介紹的設計方案,采用CPLD技術設計的多路CCD圖像信號模擬器結構簡單,實現方便,易于修改。在圖像采集卡的測試過程中,發揮了重要作用。

-

cpld

+關注

關注

32文章

1247瀏覽量

169221 -

醫療

+關注

關注

8文章

1801瀏覽量

58662 -

模擬器

+關注

關注

2文章

869瀏覽量

43165

發布評論請先 登錄

相關推薦

怎樣通過CPLD技術設計CCD相機圖像信號模擬器

怎樣通過CPLD技術設計CCD相機圖像信號模擬器

評論