今朝,病院輸液現場一般是人工節制和看管,但輸液速度和輸液量是一個很難切確把握的值,護士經由過程動彈輸液器上的手動輪來節制輸液速度,并經由過程肉眼不雅察看估量速度,而且輸液過程中,醫護人員一般不能全程陪護,會給病人和醫務人員帶來良多平安隱患和未便。本文設計了一種集輸液節制、顯示、報警、語音通信等多種 功能的輸液節制系統。

1 系統總體設計

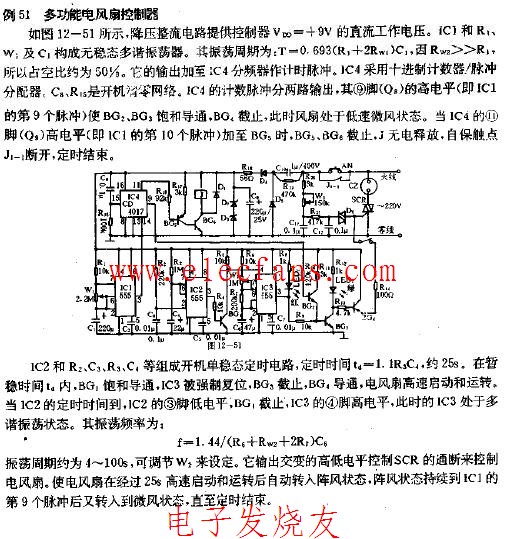

輸液監控系統原理如圖1所示,包括FPGA控制器、點滴速度檢測、余液體積檢測、執行機構、鍵盤控制、LCD顯示、語音通信(發送與接收)以及RS232總線轉換等部分。

輸液控制與語音通信是本文的主要研究內容,也是本系統穩定性和可靠性的根本保證。根據系統要求,設計中以FPGA為控制器,以光纖傳感器和容柵傳感器為檢測機構,以步進電機為執行機構。為了安全和方便,利用RS232總線增設了語音通信和輸液完成自動報警等功能。

2 硬件部分

2.1 控制器硬件設計

控制器主芯片采用Altera公司的型號為APEX系列的FPGA芯片,芯片型號為 Cyclone II EP2C35F672C6。FPGA芯片采用90 nm的低功耗設計、672-Pin FineLine BGA封裝,內置35個內嵌18×18乘法器、475個用戶管腳、4PLLs、205個差分通道(比c8高出一倍的主頻,可以達到400 MHz)典型值100萬門,最大值約160萬門。主處理器采用Altera公司的32位Nios軟核處理器,與傳統的嵌入式處理器相比,NiosⅡ處理器更加靈活。該芯片具有定制特性,可以根據自身的系統要求、性能要求和成本要求進行定制。系統總線采用AVALON總線標準。另外系統具有RS232串行通信口、鍵盤PIO、LCD顯示等外圍擴展功能,便于系統的進一步開發,縮短系統的開發周期,降低系統的開發成本[6]。

Altera 公司簡介

Altera 的可編程解決方案幫助系統和半導體公司快速高效的實現創新,突出產品優勢,贏得市場競爭。自二十年前發明世界上第一個可編程邏輯器件開始,Altera 公司秉承了創新的傳統,是世界上"可編程芯片系統" (SOPC) 解決方案倡導者。Altera 公司總部位于美國加州的圣何塞,并在全球的14個國家中擁有近2000名員工,其2005年度的年收入高達11.23億美元。Altera 將其早在1983年發明的可編程邏輯技術與軟件工具、IP 和設計服務相結合,向全世界近14,000家客戶提供超值的可編程解決方案。

Altera 一直在可編程系統級芯片,領域中處于前沿和領先的地位,結合帶有軟件工具的可編程邏輯技術、知識產權 (IP) 和技術服務,在世界范圍內為14,000多個客戶提供高質量的可編程解決方案。我們新產品系列將可編程邏輯的內在優勢 —— 靈活性、產品及時面市 —— 和更高級性能以及集成化結合在一起,專為滿足當今大范圍的系統需求而開發設計。Altera 可編程解決方案包括:業內最先進的 FPGA、CPLD 和結構化 ASIC 技術 全面內嵌的軟件開發工具 最佳的 IP 內核 可定制嵌入式處理器 現成的開發包 專家設計服務

2.2 鍵盤控制

為了操作方便,系統采用鍵盤操作。設備履行一種雙向同步串行協議,接口中最重要的4根線是數據線、地線 、電源線和時鐘線。在鍵盤內部,有一個專門負責掃描按鍵的處理器,它能檢測出某個鍵被按下或者按下后被釋放,并根據按鍵的類型產生相應的掃描碼。鍵盤發送的掃描碼有通碼(Make)和斷碼(Break)兩種類型。當鍵盤上的一個鍵被按下時,鍵盤會根據按鍵類型產生一段通碼;當鍵盤上的一個鍵按下后被釋放時,鍵盤會根據按鍵類型再產生一段斷碼。此處理器為每個按鍵分配了唯一的通碼和斷碼,這樣主機通過查找唯一的掃描碼就可以測定是哪個鍵被按下或釋放。具體方法是啟動QuartusⅡ,建立一個名為ps2_keyboard.qpf的工程,選擇器件,創建文本文件并編寫代碼,以接收來自鍵盤的掃描碼,要求對不同的按鍵做出響應,為器件進行輸入輸出管腳分配,完成后對工程進行編譯。

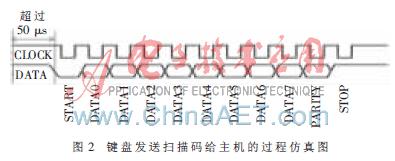

如圖2所示,鍵盤總是產生時鐘信號,從鍵盤發送到主機的數據在時鐘信號的下降沿被讀取。鍵盤的掃描碼發送給FPGA,這些掃描碼包含在鍵盤發送給主機的數據幀中。每個數據幀包括1位起始位(總是低電平)、8位數據位(即掃描碼,從低位開始發送)、1位奇偶校驗位(奇校驗)和1位結束位(總是高電平)。

2.3 傳感器

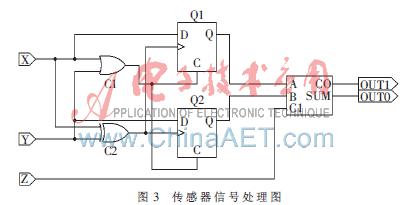

點滴速度檢測采用在茂菲氏滴管的中部外側安裝一個光纖傳感器。因為光電傳感器的紅外接收管很容易受到外界光線的干擾,并且它的直徑一般在2 mm以上,體積較大,安裝不方便。光纖傳感器測量端口面積小,可以做到直徑1 mm以內,藥液點滴時分辨率高。液滴經過時利用液滴對光線的“遮擋”使光纖接收管的接收的光束發生變化,再經過電路處理得到點滴的速度脈沖,再將這種速度脈沖采集信息發送給控制器。為了防止輸液速度過快而產生點滴連續流,設計了上下分別安裝兩個檢測光纖,從而避免了少計脈沖數而產生錯誤的處理結果。如圖3所示,電路X為光纖輸出電壓波形,Y為光纖輸出電壓波形。一般情況下,點滴離散時只有X計數,點滴連續時XY同時計數,這種方法既安全又穩定可靠。點滴離散時,XY只有一個高電平,或門C1產生的信號作為D鎖存器Q1的控制端只允許X產生的正脈沖通過,而D鎖存器Q2因為C1作用時Y信號尚在低電平,信號被屏蔽,Q2輸出低電平,門電路在計數器中作加法運算。點滴連續時XY同時輸出高電平,D鎖存器Q2也在計數。OUT0是輸出,OUT1是進位,Z是控制端輸入。

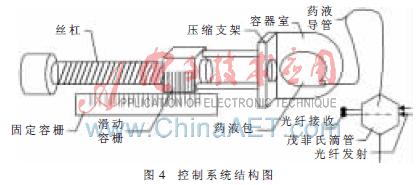

余液體積檢測采用直線式容柵傳感器,安裝位置如圖4所示。固定容柵安裝在輸液系統底座上,滑動容柵安裝在輸液系統步進電機帶動的絲杠的螺絲母上,絲杠轉動使螺母產生水平移動,測量原理如同游標卡尺,這種傳感器響應速度快、量程可以達到1 m,誤差小于0.01 mm[7]。余液體積檢測通過滑動容柵移動的距離乘以容器室的截面積而得出。

2.4 執行機構

輸液速度控制采用的控制機構由步進電機、絲杠、螺絲母、壓縮支架、容器室組成。步進電機在FPGA的控制下進行正反轉動,絲杠轉動使螺母產生水平移動,壓縮支架安裝在螺絲上,壓縮架壓縮容器室,藥液包因容器室體積變小而收縮,藥液從輸液管輸出,通過調整步進電機的步進速度,達到控制輸液速度的目的。

2.5 語音通信

立體聲CODEC芯片WM8731是一個高性能、低功耗的24位音頻立體聲接口,被廣泛應用于各種便攜式音樂播放器中。該芯片可以分別設置音頻ADC和DAC的采樣率,包含microphone-in、line-in和line-out接口,WM8731用I2C接口與FPGA連接。

語音發送接收要有一個合適的波段,本文選定為15.6 MHz。讓軟件生成一個鎖相環變頻模塊,AUDIO_DAC_ADC.v需要一個15.6 MHz的時鐘,調用FPGA上的鎖相環(PLL)資源,讓軟件生成這個模塊的。v文件,然后在de2_top.v中添加這個模塊。

添加AUDIO_DAC_ADC模塊過程為:

reg signed [15:0] audio_outR;

wire signed [15:0] audio_outL;

wire signed [15:0] audio_inL, audio_inR;

AUDIO_DAC_ADC u2 (//Audio Side

.oAUD_BCK(AUD_BCLK),

.oAUD_DATA(AUD_DACDAT),

.oAUD_LRCK(AUD_DACLRCK),

.oAUD_inL(audio_inL),/audio left data from ADC

.oAUD_inR(audio_inR),//audio right data from ADC

.iAUD_ADCDAT(AUD_ADCDAT),

.iAUD_extL(audio_outL),//audio left data to DAC

iAUD_extR(audio_outR),//audio right data to DAC

//Control Signals

.iCLK_15_6(AUD_CTRL_CLK),

.iRST_N(1′b1));

2.6 液晶顯示控制

顯示器選用唯信諾公司提供的OLED有機發光顯示器,分辨率160×128,6.5K色,用16位并行數據總線與FPGA相連。OLED的控制芯片為LGDP4216,OLED供電電壓10 V~21 V,接口供電電壓2.2 V~3.3 V。顯示區域大小可變,最大160(RGB)×128行,刷新率有7種,默認90 Hz。

2.7 RS232數據傳送與報警

使用MAX3232電平轉換芯片和9針D型連接器進行串口通信。由于系統是3.3 V供電,因此需要使用MAX3232進行電平轉換。MAX3232是3.3 V工作電源的RS232轉換芯片。護士室MAX3232適配器端口裝有三個LED燈分別用來顯示執行狀態、數據傳送、報警。串口直接連接到CyclII FPGA上。MAX3232芯片包含兩組收發器,最大數據傳輸率250 kb/s。報警功能主要是在護士室顯示,綁定在傳輸模塊上,當余液控制達到下限時發生報警。

3 軟件設計

輸液控制主程序主要由初始化模塊和各功能模塊組成,如圖5所示。初始化模塊主要完成對通信、中斷、定時的初始狀態設置。初態時,RS232通信端口設置為接收狀態,波特率設置為19 200 b/s;各功能模塊包含鍵盤控制、點滴速度檢測、步進電機控制、數據顯示、語音通信及報警等。

本系統廣泛吸取了同類系統的優點,采用的測試方法、控制方法具有安全方便、節能、可靠等特點。本系統采用Cycl-one II的FPGA進行開發,其鍵盤操作方便快捷,LCD顯示一目了然,語音通信及報警功能提高了醫患人員的安全感。本系統充分利用了鍵盤PIO、LCD顯示、ADC和DAC音頻接口、RS232串行通信口等,縮短了系統的開發周期,降低了系統的開發成本。通過實驗測試,系統各檢測傳感器、控制執行機構、顯示、報警等功能正常,性能達到了設計要求。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601838 -

控制器

+關注

關注

112文章

16203瀏覽量

177403 -

lcd

+關注

關注

34文章

4411瀏覽量

167087

發布評論請先 登錄

相關推薦

基于FPGA的多功能空調控制器設計

【 sharknaro】嵌入式WiFi智能輸液云監控系統

嵌入式WiFi輸液智能云監控系統

基于FPGA為核心的多功能輸液系統該怎么設計?

基于FPGA的輸液監控系統該怎么設計?

基于FPGA的多功能多路舵機控制器的實現

FPGA為核心的多功能輸液系統的設計

以Flash控制器為核心的FPGA在線更新功能實現設計流程介紹

采用以FPGA為控制器核心實現多功能輸液節制系統設計

采用以FPGA為控制器核心實現多功能輸液節制系統設計

評論