同步數(shù)字序列(Synchronous Digital Hierarchy)是一種全新的傳輸網(wǎng)體制,自從90年代初出現(xiàn)以來,SDH以其各方面的優(yōu)越性迅速成為通信網(wǎng)絡(luò)的骨干網(wǎng)絡(luò)。目前世界各國大多以SDH作為通信的骨干網(wǎng)絡(luò)。在我國,干線網(wǎng)絡(luò)也基本采用了SDH網(wǎng)絡(luò)。

與原有PDH(Plesinchronous Digital Hiearchy)系統(tǒng)相比,最突出的優(yōu)點就是具有強大的網(wǎng)絡(luò)管理能力。在SDH的幀結(jié)構(gòu)的各個層次中,都提供了豐富的開銷字節(jié),以實現(xiàn)對不同層次信號的全面管理。

1. SDH系統(tǒng)介紹

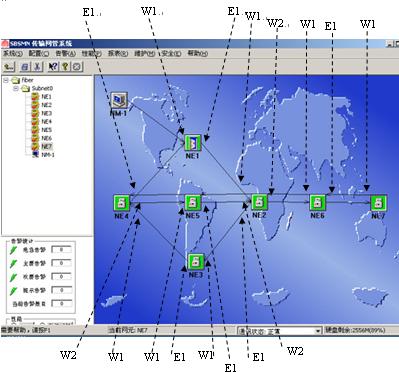

清華大學(xué)電子工程系自主開發(fā)了SDH大規(guī)模專用,它包括高階復(fù)用芯片MXH0155-2,實現(xiàn)從VC4信號到STM-1(Synchronous Transfer Module)信號的映射和解映射功能;低階映射芯片MXL021E1-3,實現(xiàn)21個2.048M的E1信號到VC4信號的映射和解映射。基于這兩個芯片,可以實現(xiàn)一個基于雙向SDH環(huán)路的ADM(ADD/DROP Multiplexer)站點,實現(xiàn)從STM-1信號中任意分插多個E1信號的功能。

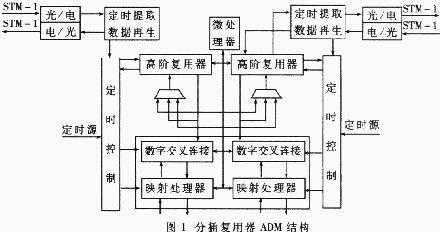

ADM系統(tǒng)以兩片MXH0155-2和一片MXL021E1-3為核心芯片,包括光收發(fā)模塊,155M時鐘恢復(fù)和綜合電路,E1信號接口處理,微處理器系統(tǒng)。系統(tǒng)結(jié)構(gòu)模塊如圖1所示。

在圖1中,兩個方向的高階復(fù)用器分別由兩片MXH0155-2實現(xiàn),兩個方向的數(shù)字交叉連接和映射處理器由一片MXL021E1-3實現(xiàn),中間的接口連接和多路選擇由一片FPGA實現(xiàn)。

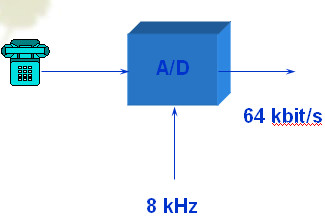

此ADM系統(tǒng)中,兩片MXH0155-2和一片MXL021E1-3都提供了微處理器接口實現(xiàn)對芯片的配置、管理和監(jiān)控,需要具有16位地址的8位微處理器。MXH0155-2工作幀頻為8KHz,微處理器系統(tǒng)需要以8KHz時鐘頻率對其進行一系列管理工作,而MXL021E1-3的工作幀頻為2KHz,需要以2KHz的時鐘頻率進行管理。MXL021E1-3還可以實現(xiàn)21個E1信號的分插功能,因此在2KHz的時鐘頻率內(nèi)需要處理兩個方向21路信號的管理和監(jiān)控。同時,此管理系統(tǒng)通過串口實現(xiàn)與計算機的通信,可以通過計算機實現(xiàn)對此ADM系統(tǒng)的配置和管理。

2 MCS-51系列DS80C320介紹

單片微型計算機已經(jīng)被應(yīng)用到國民生產(chǎn)中的許多方面,例如工業(yè)控制、日用家電等等。近年來,隨著單片機檔次的不斷提高,功能的不斷完善,其應(yīng)用也越來越廣泛,功能越來越強大,甚至可以實現(xiàn)對復(fù)雜系統(tǒng)的管理和控制。

按照以上要求,微處理器需要兩個定時中斷、一個RS232串口,同時由于需要進行監(jiān)控的內(nèi)容較多,需要一個高速微處理器,我們選用了Dallas公司的DS80C320做為處理器來實現(xiàn)對此ADM系統(tǒng)的管理。

Dallas公司的80C320單片機與MCS-51的80C32系列單片機兼容,其突出特點是它的高速性能。外部振蕩器可以達到33MHz,一個指令周期僅由四個振蕩周期組成,因此其最高指令周期可以達到33/4=8.25Mbps。

3 微處理器系統(tǒng)的硬件實現(xiàn)

此微處理器的硬件系統(tǒng)非常簡單,是單片機的最小系統(tǒng),以DS80C320為核心,加上外部程序存儲器(EPROM27512)、數(shù)據(jù)存儲器(雙口RAM)、地址鎖存器(74LS373)、3-8譯碼器(74LS138)和RS232電平轉(zhuǎn)換(MAX233)構(gòu)成。此微處理器系統(tǒng)作為ADM系統(tǒng)的一部分嵌入到系統(tǒng)中,實現(xiàn)的功能包括對三片大規(guī)模集成電路的管理,與計算機的通信和數(shù)據(jù)采集工作。

由于當(dāng)DS80C320工作到33MHz時鐘頻率時,對外圍器件要求較高,例如EPROM要求達到55ns,地址鎖存等也需要采用高速F系列的74F373等。因此選用了24.576MHz的振蕩器作為外部振蕩器,此時可以采用常用外圍器件,同時可以實現(xiàn)8KHz和2KHz中斷的嚴(yán)格定時,而且經(jīng)仿真和實驗證明可以保證足夠的處理時間要求。

4微處理器系統(tǒng)的軟件構(gòu)成

此系統(tǒng)的軟件構(gòu)成由主程序和三個中斷程序組成。主程序完成系統(tǒng)的配置工作。串口中斷完成計算機對系統(tǒng)工作模式的修改和系統(tǒng)監(jiān)控,兩個定時中斷分別以8KHz和2KHz的頻率對系統(tǒng)進行監(jiān)控和數(shù)據(jù)采集。

2KHz定時中斷的指令較多,約占了2KHz頻率即500us到2/3的時間左右,為保證8KHz定時中斷嚴(yán)格的定時關(guān)系,8KHz定時中斷的優(yōu)先級為1,要高于2KHz定時中斷優(yōu)先級,即在2KHz定時中斷處理程序中,可以嵌套進行8KHz定時中斷處理。

串口中斷程序,即計算機對系統(tǒng)進行配置和監(jiān)控時,系統(tǒng)的定時中斷可以停止,因為在系統(tǒng)正常工作時,無需計算機進行管理。此時一般是系統(tǒng)出了問題,需要人工干預(yù),要求及時反應(yīng),所以串口中斷的優(yōu)先級也設(shè)置為1。由于單片機內(nèi)部只有兩個中斷優(yōu)先級,此時8KHz中斷和串口優(yōu)先級相同,但是串口中斷可以得到及時反應(yīng)。因為當(dāng)串口工作在19200波特率時,串口發(fā)送或接收一個字節(jié)的時間也遠大于8KHz的幀頻,同時串口中斷程序和計算機程序之間采用了握手控制,保證串口數(shù)據(jù)交換的正確性。

4.1 主程序

主程序的流程為:

(1)芯片的初始配置,通過查表寫入約400個字節(jié)的數(shù)據(jù);

(2)配置DS80C320,設(shè)置計數(shù)器(串口波特率定時T1,定時中斷T0和T2都工作在重裝載模式,保證嚴(yán)格的定時關(guān)系),設(shè)置中斷優(yōu)先級,開啟計數(shù)和中斷;

(3)永久等待。

4.2 串口中斷處理程序

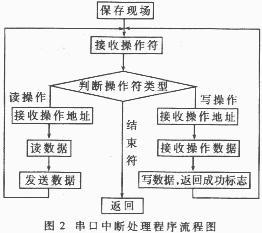

串口中斷處理程序的流程圖如圖2所示。完成功能如下:

(1)串口接收數(shù)據(jù),進入中斷處理程序,保存現(xiàn)場;

(2)根據(jù)接收數(shù)據(jù)判斷操作類型,若為讀寫操作,進入步驟(3),若接收到結(jié)束符,進入步驟(4);

(3)進行讀寫操作;返回步驟(2);

(4)結(jié)束中斷處理程序,返回。

4.3 8KHz中斷處理程序(T0定時中斷)

(1)進入中斷處理程序,保存現(xiàn)場;

(2)查詢兩片MXH0155-2,根據(jù)接收方向的告警信號來控制發(fā)送方向的數(shù)據(jù),采集接收方向的告警信號寫入雙口RAM;

(3)結(jié)束中斷處理程序,返回。

4.4 2KHz中斷處理程序(T2時鐘中斷)

(1)進入中斷處理程序,保存現(xiàn)場,內(nèi)部2000計數(shù)器加1;

(2)查詢低階映射芯片MXL021E1-3,分別查詢21路接收方向的告警信號,根據(jù)不同的告警信號對發(fā)送方向進行控制,采集21路的告警信號進行編碼并寫入雙口RAM;

(3)查詢2000計數(shù)器,當(dāng)達到2000時,計數(shù)器清零,同時對三片集成電路內(nèi)部的誤碼秒計數(shù)器進行處理,若計數(shù)值超出預(yù)期值,則給出信號劣化告警;

(4)結(jié)束中斷處理程序,返回。

通過對此微處理器系統(tǒng)的設(shè)計、仿真和實際驗證,證明了一個復(fù)雜的SDH雙向環(huán)路的ADM站點可以通過簡單的微處理器系統(tǒng)實現(xiàn)完全的管理和監(jiān)控,并為SDH大規(guī)模專用集成電路的推廣應(yīng)用奠定了基礎(chǔ)

-

處理器

+關(guān)注

關(guān)注

68文章

19178瀏覽量

229200 -

芯片

+關(guān)注

關(guān)注

454文章

50460瀏覽量

421968 -

微處理器

+關(guān)注

關(guān)注

11文章

2247瀏覽量

82331

發(fā)布評論請先 登錄

相關(guān)推薦

SDH數(shù)字微波通信技術(shù)的組成、特點及應(yīng)用介紹

SDH原理簡介

SDH環(huán)形網(wǎng)絡(luò)演變拓?fù)渲芯W(wǎng)元設(shè)備時鐘的設(shè)置

SDH網(wǎng)絡(luò)結(jié)構(gòu)和網(wǎng)絡(luò)保護機理

SDH定時與同步

SDH原理

SONET/SDH光網(wǎng)絡(luò)概念

什么是SONET/SDH光網(wǎng)絡(luò)

通信系統(tǒng)SDH自愈環(huán)網(wǎng)的分析應(yīng)用

SDH傳輸網(wǎng)的時鐘優(yōu)化

SDH技術(shù)學(xué)習(xí)要點

SDH傳輸原理PPT介紹

SDH原理和技術(shù)

SDH的信號結(jié)構(gòu)

SDH數(shù)字微波通信技術(shù)的組成、特點及應(yīng)用

SDH網(wǎng)絡(luò)的特點及應(yīng)用

SDH網(wǎng)絡(luò)的特點及應(yīng)用

評論