TCLGU21機芯高清彩電屬于數字窗系列,是在NU21機芯基礎上派生出來的,主板電路完全一樣,僅數字板。f二的倍行處理部分不一樣,NU21機芯倍行芯片采用PW1235A,該機芯采用FLI2300,不僅電路結構簡單,而且新增了許多功能。GU21機芯的代表機型是H1D34158H。

FLI2300是微科公司生產的最新總線控制型數字解碼及的數字變頻主芯片,其PAL制圖像具有以下幾種成像模式:100Hz逐點清晰、60Hz數字逐點、75Hz數字逐點、1520線數字增密;NTSC制圖像具有60Hz數字逐點成像功能。

一、數字板簡介

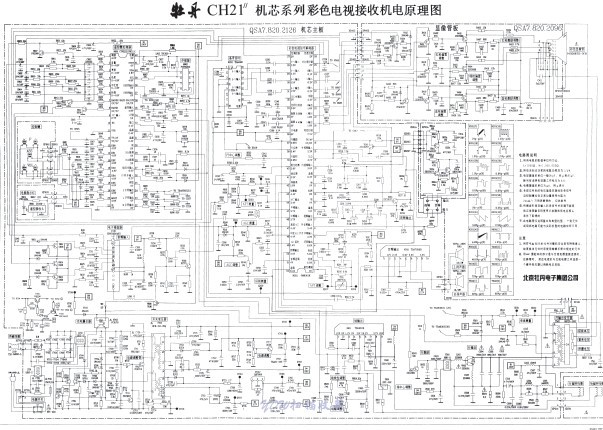

GU21機芯數字板電路主要由CPUTMP88CS38N(IC2)、24C00(IC1)、P15V330(QD11)、AD9883(UD3)、VPC3230D(UD7)、FLI2300(UD6):KM432S2030(UDl)、TDA9332H(UD2)等集成電路及一些外圍元件組成,其組成框圖見圖1。

圖1 組成框圖

GU21機芯數字板通過JP1~JP5五個插座與外部電路連接。其中,JP1為從主板送過來的隔行模擬視頻信號及ABL、FBP、VD+、VD-、VFB、EW、EHT、12V、5.2V電源等信號,輸入的模擬信號進入VPC3230進行視頻解碼;IP2為遙控信號、按鍵信號、總線數據,與主板S001A的端口相連接;JP3為RGB,及消隱信號輸出到CRT板;IP4為HDTV的信號輸入端口;JP5為VGA的RGB及HS、VS同步信號輸入端口。

所有的隔行視頻信號都輸入到視頻解碼器VPC3230D內部。VPC3230D是微科公司生產的梳狀濾波視頻處理器,該芯片集成了視頻切換、Y/C分離(4H自適應梳狀濾波器)、A/D轉換、數字解碼、pIp等功能。視頻解碼輸出支持ITU-R601/656數字輸出接口。

二、數字板信號流程分析

1.TV及隔行視頻輸入信號

一體化高頻頭輸出的TV視頻信號經電容CD131、RD130平滑濾波后,從VPC3230D(75)腳輸入;S端子的C、Y信號分別經電容CD135,CD136耦合后從(71)、(72)腳輸入;AV2的視頻信號經電容CD129耦合后,從(73)腳輸入;Cb、Y、Cr信號分別經LD21、CD139、CD123、RD111,CD128、LD28、CD138、CD132、RD21、LD22、CD141、CD140、RD122、CD130組成的濾波電路濾波后,從①~③腳輸入。輸入的視頻信號經VPC323()D視頻解碼處理后,輸出數字信號。

VPC3230D是一塊總線控制型PAL/NTSC/SECAM制彩色電視信號處理集成電路,具有功能多、外圍電路簡單、性能優良等特點。VPC3230D(13)、(14)腳為總線控制端(SCL、SDA),與外圍集成電路相連接;(15)腳外接的RD83、QD8、RDl04、DD6是一個復位控制電路,用于對芯片復位;(63)、(62)腳外接晶振XD1(20.25MHz),產生基準彩色所需信號。VPC3230D采用3.3V和5V供電。

VPC3230D(70)腳輸出視頻信號,經QD10、RD146組成的射隨電路放大后,從QD10的發射極輸出。VPC3230D(30)~(34)、(37)~(40)輸出8bit的YC信號(簡稱8bit位格式的數字信號),送往FLI2300進行精密顯像處理。

2.VGA及HDTV信號

VGA的RGB及Hs、Vs信號從端口JP5輸入,VGA的RGB信號先由FB5~FB7、CD154、CD158、CD162濾波,再由QD4~QD6射隨放大,最后送到P15V330(QD11)的②、⑤、(11)腳。

HDTV信號由端口JP4輸入,HDTV的Y、Pb、Pr信號先由FB2~FB4濾波,再送入QD11的③、⑥、⑩腳。

P15V330是一個4通道2選1高性能視頻模擬開關,具有導通電阻低、頻帶寬、低串擾等特點。VGA和HDTV信號經QD11切換后,從QD11的④、⑦、⑨腳輸出RGB信號,經RD34、CD28、RD36、CD35、RD33、CD28電容耦合后,送到AD9883(uD3)(54)、(48)、(43)腳。

AD9883是ADI公司專為平板顯示模擬前端接口設計的模數轉換集成電路,采用80腳封裝,3.3V供電電壓。該IC內置三通道8位110MHz采樣頻率的AD轉換器、同步處理器及時鐘發生器、I2C主機接口等功能模塊,其數字視頻輸出接口支持4:4:4的YUV信號輸出。輸入的YUV信號經AD9883處理后,從②~⑨腳、(12)~(19)腳、(70)~(77)腳輸出8bit的數字YUV信號,分別送到FLI2300的(21)~(28)腳,(29)腳、(32)~(35)腳、(38)~(40)腳,(18)~(20)腳、(11)~(15)腳進行處理。AD9883的(30)、(31)腳是VGA的行同步和場同步信號輸入端,(56)、(57)腳分別是SDA、SCL腳。AD9883的供電電壓為3.3V,供電腳為(33)~(35)腳。

AD9883(67)腳(DATACK)輸出數據時鐘信號,(66)腳(HSOUT)輸出行同步信號,(64)腳(VSOUT)輸出場同步信號,(65)腳輸出G復合同步信號,分別送到FLI2300④腳(IN-CLKl-PORTl)、①腳(HSYNCl-PORT1)和②腳(VSYNC-PORTI)。另外,AD9883(65)、(64)腳還分別與CPU(36)、(13)腳相連。

3.變頻處理

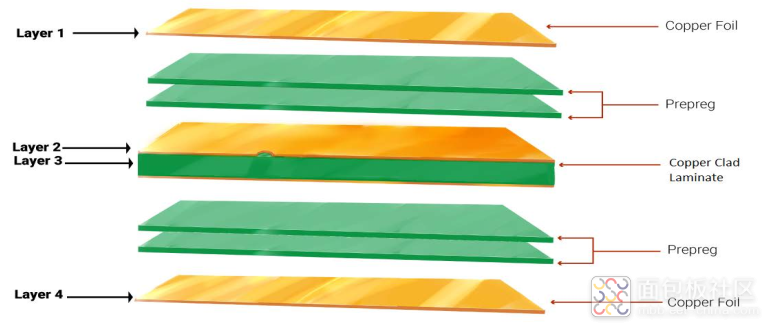

FLI2300是Genesis公司推出的高質量數字視頻格式變換器,采于CRT-TV的高整合數字視頻轉換的專利應用軟件,可進行非線性和任意圖形縮放比例、幀頻比例轉換,其應用框圖如圖2所示。

圖2 應用框圖

FLI230()①、②腳為TV信號的Hs和Vs同步信號輸入端,(191)、(192)腳外接13.5MHz晶體振蕩器(XD3),(45)、(46)腳(SCL、SDA)是時鐘、數據總線控制端,(47)腳是復位控制信號輸入端,3.3V電壓經RD74、CD66降壓后產生一個復位信號,起到復位信號的作用。

VPC3230D(31)~(34)腳和(37)~(40)腳輸出的8bit數字視頻信號,經FLI2300變頻處理后,從(176)、(173)、(170)腳輸出模擬的RGB信號。

【提示】模擬信號經VPC3230D、AD9883轉換為數字信號,但信號頻率沒有改變。只有經FLI2300處理后,圖像信號行頻才變換為31.125kHz,場頻才變換為所選掃描方式對應的場頻。

KM432S2030C是一個幀存儲器,主要通過16位地址線和16位的數據線與FLI2300相連接,它既接收FLI2300處理后的圖像信號,也接受從FL12300讀出的數據信號。

4.RGB控制電路

所有的顯示處理由集成電路TDA9332H(UD2)完成。FLI2300的(176)、(173)、(170)腳輸出的模擬RGB信號送到TDA9332H(30)~(32)腳,作為第一基色信號。TDA9332H的(35)~(37)腳輸入的是第二基色輸入信號(R2、G2、B2),可以是屏顯(OSD)信號,也可以是圖文電視(Text)信號,但要求輸入信號的幅度為0.7V.在IC內部電視信號與屏顯信號之間的切換通過疊加功能和快速消隱功能實現。

另外,第二基色輸入信號僅受亮度調整控制。

TDA9332H(43)腳是暗電流控制腳(BCL),彩色顯像管暗電流調整實際是調整彩色顯像管的截止電平,它通過調整三個電子槍的截止電平,使彩色顯像管電子束處于不發射電子的截止狀態。

5.同步電路與掃描信號處理電路

TDA9332H⑧腳輸出的行激勵信號由VCO分頻產生。為了重顯穩定的圖像,(24)腳(HS信號)輸入行同步信號,在內接時間常數的鎖相環(PLL)電路作用下,使壓控振蕩器的頻率與之同步。

行激勵信號的頻率(fH或2fH由(12)腳(HSEL)接地或開路進行選擇。(23)、(24)腳輸入的場激勵脈沖(VD)和行激勵脈沖(HD)的極性TDA9332H內部進行檢測,其極性由總線的狀態位讀出。

第二鑒相環路通過比較VCO提供的基準脈沖和(13)腳輸入的行逆程信號的相位,產生行激勵脈沖HD,環路的時間常數由IC內部設定。TDA9332H(14)腳輸入的行相位校正信號用來補償由束電流變化引起的水平位移。TDA9332H⑩、(11)腳分別為總線SCL和SDA端。

6.場掃描電路與光柵幾何失真校正

TDA9332H①、②腳輸出場激勵信號,③腳輸出東西(E-W)枕形失真校正信號,這些信號均由場頻電路產生。場鋸齒波發生器需在(15)、(16)腳外接誤差非常小的電阻和電容,以確保鋸齒波電壓幅度穩定。

TDA9332H還具有超高壓(EHT)補償功能,④腳輸入的EHTIN信號可以控制水平、垂直幾何失真校正電路的輸出信號幅度,以維持光柵水平、垂直以及幾何失真校正效果不變。TDA9332H的⑤腳為放電保護輸入端,防止顯像管打火損壞行輸出管。

-

處理器

+關注

關注

68文章

19166瀏覽量

229151 -

濾波器

+關注

關注

160文章

7729瀏覽量

177690 -

TCL

+關注

關注

10文章

1715瀏覽量

88471

發布評論請先 登錄

相關推薦

TCLGU21機芯數字板的組成及信號流程分析

TCLGU21機芯數字板的組成及信號流程分析

評論