英特爾? 至強(qiáng)融核? 處理器是一款能為要求最苛刻的高性能計(jì)算應(yīng)用程序提供大規(guī)模并行處理和矢量化服務(wù)的可引導(dǎo)主機(jī)處理器。能效型集成架構(gòu)提供比類似平臺(tái)高得多的每單元計(jì)算能力,有效優(yōu)化總體擁有成本。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

處理器

+關(guān)注

關(guān)注

68文章

19169瀏覽量

229156 -

英特爾

+關(guān)注

關(guān)注

60文章

9889瀏覽量

171535 -

主機(jī)

+關(guān)注

關(guān)注

0文章

985瀏覽量

35068 -

計(jì)算

+關(guān)注

關(guān)注

2文章

445瀏覽量

38737

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

英特爾推出Intel Xeon Phi協(xié)同處理器 為探索未來帶來新架構(gòu)

為了替高效能運(yùn)算開創(chuàng)新的時(shí)代,英特爾公司推出累積多年研究與合作的成果—Intel Xeon Phi協(xié)同處理器(coprocessor),為製造業(yè)、生命科學(xué)、能源與其他領(lǐng)域的創(chuàng)新突破帶來

發(fā)表于 11-14 08:46

?2305次閱讀

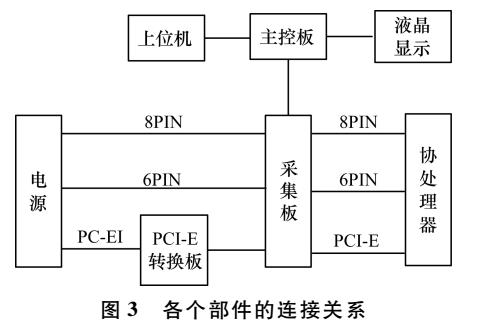

Xeon Phi協(xié)處理器的功耗測量

供電通道的實(shí)時(shí)電壓和電流,通過計(jì)算獲得協(xié)處理器實(shí)時(shí)功耗,并在實(shí)測數(shù)據(jù)的基礎(chǔ)上分別分析Xeon Phi協(xié)處

發(fā)表于 02-05 15:57

?0次下載

英特爾Xeon與英特爾Xeon Phi?協(xié)處理器的并行程序模型

and their optimized use on clusters of Intel? Xeon and Intel? Xeon Phi? coprocessor. "Advanced Parallel Program M

英特爾Xeon Phi?協(xié)處理器(編譯7第4部分)

Intel? Xeon? & Xeon? Phi? Webinar:

This two day webinar series introduces you to the world

英特爾Xeon Phi?協(xié)處理器(編譯7第1部分)

Intel? Xeon? & Xeon? Phi? Webinar:

This two day webinar series introduces you to the world

英特爾Xeon Phi?協(xié)處理器(編譯7第3部分)

Intel? Xeon? & Xeon? Phi? Webinar:

This two day webinar series introduces you to the world

英特爾XEON Phi?協(xié)處理器:第1部分

Welcome and Introduction, Intel? Xeon Phi? coprocessor, Part 1

英特爾Xeon Phi?協(xié)處理器(編譯7第6部分)

Intel? Xeon? & Xeon? Phi? Webinar:

This two day webinar series introduces you to the world

英特爾Xeon Phi?協(xié)處理器:介紹

look at the hardware architecture of the Intel? Xeon Phi? coprocessor

英特爾Xeon Phi?協(xié)處理器車間:優(yōu)化第1部分

This module looks at basic optimization techniques for the Intel Xeon Phi coprocessor.

英特爾Xeon Phi?協(xié)處理器車間:編程模型(2)

? Xeon Phi coprocessor HW abstraction, programming model options, using standardized libraries such as Intel? MKL, high level view of of

英特爾Xeon Phi?協(xié)處理器車間:編程模型(4)

? Xeon Phi coprocessor HW abstraction,

Section 4: Architecturally independent vs dependent programming approaches

英特爾Xeon Phi?協(xié)處理器車間:編程模型(3)

? Xeon Phi coproce

Section 3: Array notation, and Intel? CilkTM Plus task parallelism, pure auto-vectorization, semi-automatic vector

英特爾至強(qiáng)處理器和Xeon Phi協(xié)處理器集群的性能驗(yàn)證

性能驗(yàn)證-ON-Intel的Xeon的處理器和Xeon的PHI-協(xié)處理器簇

英特爾至強(qiáng)Phi協(xié)處理器上的Fortran應(yīng)用程序的開發(fā)

此網(wǎng)絡(luò)研討會(huì)介紹了開發(fā)用于Windows *的英特爾?至強(qiáng)融核?協(xié)處理器的Fortran應(yīng)用程序的開發(fā)環(huán)境。

英特爾Xeon Phi?協(xié)處理器車間:編程模型(1)

英特爾Xeon Phi?協(xié)處理器車間:編程模型(1)

評(píng)論