說到PCB板,很多朋友會(huì)想到它在我們周圍隨處可見,從一切的家用電器,電腦內(nèi)的各種配件,到各種數(shù)碼產(chǎn)品,只要是電子產(chǎn)品幾乎都會(huì)用到PCB板,那么到底什么是PCB板呢?

PCB板就是PrintedCircuitBlock,即印制電路板,供電子組件安插,有線路的基版。通過使用印刷方式將鍍銅的基版印上防蝕線路,并加以蝕刻沖洗出線路。

工程師的巨大福利,首款P_C_B分析軟件,點(diǎn)擊免費(fèi)領(lǐng)取

PCB板可以分為單層板、雙層板和多層板。各種電子元件都是被集成在PCB板上的,在最基本的單層PCB上,零件都集中在一面,導(dǎo)線則都集中在另一面。這么一來我們就需要在板子上打洞,這樣接腳才能穿過板子到另一面,所以零件的接腳是焊在另一面上的。因?yàn)槿绱耍@樣的PCB的正反面分別被稱為零件面(ComponentSide)與焊接面(SolderSide)。

雙層板可以看作把兩個(gè)單層板相對粘合在一起組成,板的兩面都有電子元件和走線。有時(shí)候需要把一面的單線連接到板的另一面,這就要通過導(dǎo)孔(via)。導(dǎo)孔是在PCB上,充滿或涂上金屬的小洞,它可以與兩面的導(dǎo)線相連接。現(xiàn)在很多電腦主板都在用4層甚至6層PCB板,而顯卡一般都在用了6層PCB板,很多高端顯卡像nVIDIAGeForce4Ti系列就采用了8層PCB板,這就是所謂的多層PCB板。在多層PCB板上也會(huì)遇到連接各個(gè)層之間線路的問題,也可以通過導(dǎo)孔來實(shí)現(xiàn)。

由于是多層PCB板,所以有時(shí)候?qū)Э撞恍枰┩刚麄€(gè)PCB板,這樣的導(dǎo)孔叫做埋孔(Buriedvias)和盲孔(Blindvias),因?yàn)樗鼈冎淮┩钙渲袔讓印Cた资菍讓觾?nèi)部PCB與表面PCB連接,不須穿透整個(gè)板子。埋孔則只連接內(nèi)部的PCB,所以光是從表面是看不出來的。在多層板PCB中,整層都直接連接上地線與電源。所以我們將各層分類為信號層(Signal),電源層(Power)或是地線層(Ground)。如果PCB上的零件需要不同的電源供應(yīng),通常這類PCB會(huì)有兩層以上的電源與電線層。采用的PCB板層數(shù)越多,成本也就越高。當(dāng)然,采用更多層的PCB板對提供信號的穩(wěn)定性很有幫助。

專業(yè)的PCB板制作過程相當(dāng)復(fù)雜,拿4層PCB板為例。主板的PCB大都是4層的。制造的時(shí)候是先將中間兩層各自碾壓、裁剪、蝕刻、氧化電鍍后,這4層分別是元器件面、電源層、地層和焊錫壓層。再將這4層放在一起碾壓成一塊主板的PCB。接著打孔、做過孔。洗凈之后,將外面兩層的線路印上、敷銅、蝕刻、測試、阻焊層、絲印。最后將整版PCB(含許多塊主板)沖壓成一塊塊主板的PCB,再通過測試后進(jìn)行真空包裝。

如果PCB制作過程中銅皮敷著得不好,會(huì)有粘貼不牢現(xiàn)象,容易隱含短路或電容效應(yīng)(容易產(chǎn)生干擾)。PCB上的過孔也是必須注意的。如果孔打得不是在正中間,而是偏向一邊,就會(huì)產(chǎn)生不均勻匹配,或者容易與中間的電源層或地層接觸,從而產(chǎn)生潛在短路或接地不良因素。

銅線布線過程

制作的第一步是建立出零件間聯(lián)機(jī)的布線。我們采用負(fù)片轉(zhuǎn)印方式將工作底片表現(xiàn)在金屬導(dǎo)體上。這項(xiàng)技巧是將整個(gè)表面鋪上一層薄薄的銅箔,并且把多余的部份給消除。追加式轉(zhuǎn)印是另一種比較少人使用的方式,這是只在需要的地方敷上銅線的方法,不過我們在這里就不多談了。正光阻劑是由感光劑制成的,它在照明下會(huì)溶解。有很多方式可以處理銅表面的光阻劑,不過最普遍的方式,是將它加熱,并在含有光阻劑的表面上滾動(dòng)。它也可以用液態(tài)的方式噴在上頭,不過干膜式提供比較高的分辨率,也可以制作出比較細(xì)的導(dǎo)線。遮光罩只是一個(gè)制造中PCB層的模板。

在PCB板上的光阻劑經(jīng)過UV光曝光之前,覆蓋在上面的遮光罩可以防止部份區(qū)域的光阻劑不被曝光。這些被光阻劑蓋住的地方,將會(huì)變成布線。在光阻劑顯影之后,要蝕刻的其它的裸銅部份。蝕刻過程可以將板子浸到蝕刻溶劑中,或是將溶劑噴在板子上。一般用作蝕刻溶劑使用三氯化鐵等。蝕刻結(jié)束后將剩下的光阻劑去除掉。

1.布線寬度和電流

一般寬度不宜小于0.2mm(8mil)

在高密度高精度的PCB上,間距和線寬一般0.3mm(12mil)。

當(dāng)銅箔的厚度在50um左右時(shí),導(dǎo)線寬度1~1.5mm (60mil) = 2A

公共地一般80mil,對于有微處理器的應(yīng)用更要注意。

2.到底多高的頻率才算高速板?

當(dāng)信號的上升/下降沿時(shí)間< 3~6倍信號傳輸時(shí)間時(shí),即認(rèn)為是高速信號.

對于數(shù)字電路,關(guān)鍵是看信號的邊沿陡峭程度,即信號的上升、下降時(shí)間,

按照一本非常經(jīng)典的書《High Speed Digtal Design>的理論,信號從10%上升到90%的時(shí)間小于6倍導(dǎo)線延時(shí),就是高速信號!------即!即使8KHz的方波信號,只要邊沿足夠陡峭,一樣是高速信號,在布線時(shí)需要使用傳輸線路論

3.PCB板的堆疊與分層

四層板有以下幾種疊層順序。下面分別把各種不同的疊層優(yōu)劣作說明:

第一種情況

GND

S1+POWER

S2+POWER

GND

第二種情況

SIG1

GND

POWER

SIG2

第三種情況

GND

S1

S2

POWER

注:S1 信號布線一層,S2 信號布線二層;GND 地層 POWER 電源層

第一種情況,應(yīng)當(dāng)是四層板中最好的一種情況。因?yàn)橥鈱邮堑貙樱瑢MI有屏蔽作用,同時(shí)電源層同地層也可靠得很近,使得電源內(nèi)阻較小,取得最佳郊果。但第一種情況不能用于當(dāng)本板密度比較大的情況。因?yàn)檫@樣一來,就不能保證第一層地的完整性,這樣第二層信號會(huì)變得更差。另外,此種結(jié)構(gòu)也不能用于全板功耗比較大的情況。

第二種情況,是我們平時(shí)最常用的一種方式。從板的結(jié)構(gòu)上,也不適用于高速數(shù)字電路設(shè)計(jì)。因?yàn)樵谶@種結(jié)構(gòu)中,不易保持低電源阻抗。以一個(gè)板2毫米為例:要求Z0=50ohm. 以線寬為8mil.銅箔厚為35цm。這樣信號一層與地層中間是0.14mm。而地層與電源層為1.58mm。這樣就大大的增加了電源的內(nèi)阻。在此種結(jié)構(gòu)中,由于輻射是向空間的,需加屏蔽板,才能減少EMI。

第三種情況,S1層上信號線質(zhì)量最好。S2次之。對EMI有屏蔽作用。但電源阻抗較大。此板能用于全板功耗大而該板是干擾源或者說緊臨著干擾源的情況下。

4.阻抗匹配

反射電壓信號的幅值由源端反射系數(shù)ρs和負(fù)載反射系數(shù)ρL 決定

ρL = (RL - Z0) / (RL + Z0) 和 ρS = (RS - Z0) / (RS + Z0)

在上式中,若RL=Z0則負(fù)載反射系數(shù)ρL=0。若 RS=Z0源端反射系數(shù)ρS=0。

由于普通的傳輸線阻抗Z0通常應(yīng)滿足50Ω的要求50Ω左右,而負(fù)載阻抗通常在幾千歐姆到幾十千歐姆。因此,在負(fù)載端實(shí)現(xiàn)阻抗匹配比較困難。然而,由于信號源端(輸出)阻抗通常比較小,大致為十幾歐姆。

因此在源端實(shí)現(xiàn)阻抗匹配要容易的多。如果在負(fù)載端并接電阻,電阻會(huì)吸收部分信號對傳輸不利(我的理解).當(dāng)選擇TTL/CMOS標(biāo)準(zhǔn) 24mA驅(qū)動(dòng)電流時(shí),其輸出阻抗大致為13Ω。若傳輸線阻抗Z0=50Ω,那么應(yīng)該加一個(gè)33Ω的源端匹配電阻。13Ω+33Ω=46Ω (近似于50Ω,弱的欠阻尼有助于信號的setup時(shí)間)

當(dāng)選擇其他傳輸標(biāo)準(zhǔn)和驅(qū)動(dòng)電流時(shí),匹配阻抗會(huì)有差異。在高速的邏輯和電路設(shè)計(jì)時(shí),對一些關(guān)鍵的信號,如時(shí)鐘、控制信號等,我們建議一定要加源端匹配電阻。

這樣接了信號還會(huì)從負(fù)載端反射回來,因?yàn)樵炊俗杩蛊ヅ洌瓷浠貋淼男盘柌粫?huì)再反射回去。

5.電源線和地線布局注意事項(xiàng)

電源線盡量短,走直線,而且最好走樹形、不要走環(huán)形

地線環(huán)路問題:對于數(shù)字電路來說,地線環(huán)路造成的地線環(huán)流也就是幾十毫伏級別的,而TTL的抗干擾門限是1.2V,CMOS電路更可以達(dá)到1/2電源電壓,也就是說地線環(huán)流根本就不會(huì)對電路的工作造成不良影響。相反,如果地線不閉合,問題會(huì)更大,因?yàn)閿?shù)字電路在工作的時(shí)候產(chǎn)生的脈沖電源電流會(huì)造成各點(diǎn)的地電位不平衡,比如本人實(shí)測74LS161在反轉(zhuǎn)時(shí)地線電流1.2A(用2Gsps示波器測出,地電流脈沖寬度7ns)。

在大脈沖電流的沖擊下,如果采用枝狀地線(線寬25mil)分布,地線間各個(gè)點(diǎn)的電位差將會(huì)達(dá)到百毫伏級別。而采用地線環(huán)路之后,脈沖電流會(huì)散布到地線的各個(gè)點(diǎn)去,大大降低了干擾電路的可能。采用閉合地線,實(shí)測出各器件的地線最大瞬時(shí)電位差是不閉合地線的二分之一到五分之一。當(dāng)然不同密度不同速度的電路板實(shí)測數(shù)據(jù)差異很大,我上面所說,指的是大約相當(dāng)于Protel 99SE所附帶的Z80 Demo板的水平;對于低頻模擬電路,我認(rèn)為地線閉合后的工頻干擾是從空間感應(yīng)到的,這是無論如何也仿真和計(jì)算不出來的。

如果地線不閉合,不會(huì)產(chǎn)生地線渦流,beckhamtao所謂“但地線開環(huán)這個(gè)工頻感應(yīng)電壓會(huì)更大。”的理論依據(jù)何在?舉兩個(gè)實(shí)例,7年前我接手別人的一個(gè)項(xiàng)目,精密壓力計(jì),用的是14位A/D轉(zhuǎn)換器,但實(shí)測只有11位有效精度,經(jīng)查,地線上有15mVp-p的工頻干擾,解決方法就是把PCB的模擬地環(huán)路劃開,前端傳感器到A/D的地線用飛線作枝狀分布,后來量產(chǎn)的型號PCB重新按照飛線的走線生產(chǎn),至今未出現(xiàn)問題。

第二個(gè)例子,一個(gè)朋友熱愛發(fā)燒,自己DIY了一臺功放,但輸出始終有交流聲,我建議其將地線環(huán)路切開,問題解決。事后此位老兄查閱數(shù)十種“Hi-Fi名機(jī)”PCB圖,證實(shí)無一種機(jī)器在模擬部分采用地線環(huán)路。

6.印制電路板設(shè)計(jì)原則和抗干擾措施

印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著電于技術(shù)的飛速發(fā)展,PGB的密度越來越高。PCB設(shè)計(jì)的好壞對抗干擾能力影響很大。因此,在進(jìn)行PCB設(shè)計(jì)時(shí).必須遵守PCB設(shè)計(jì)的一般原則,并應(yīng)符合抗干擾設(shè)計(jì)的要求。

PCB設(shè)計(jì)的一般原則

要使電子電路獲得最佳性能,元器件的布且及導(dǎo)線的布設(shè)是很重要的。為了設(shè)計(jì)質(zhì)量好、造價(jià)低的PCB.應(yīng)遵循以下一般原則:

1.布局

首先,要考慮PCB尺寸大小。PCB尺寸過大時(shí),印制線條長,阻抗增加,抗噪聲能力下降,成本也增加;過小,則散熱不好,且鄰近線條易受干擾。在確定PCB尺寸后.再確定特殊元件的位置。最后,根據(jù)電路的功能單元,對電路的全部元器件進(jìn)行布局。

在確定特殊元件的位置時(shí)要遵守以下原則:

(1)盡可能縮短高頻元器件之間的連線,設(shè)法減少它們的分布參數(shù)和相互間的電磁干擾。易受干擾的元器件不能相互挨得太近,輸入和輸出元件應(yīng)盡量遠(yuǎn)離。

(2)某些元器件或?qū)Ь€之間可能有較高的電位差,應(yīng)加大它們之間的距離,以免放電引出意外短路。帶高電壓的元器件應(yīng)盡量布置在調(diào)試時(shí)手不易觸及的地方。

(3)重量超過15g的元器件、應(yīng)當(dāng)用支架加以固定,然后焊接。那些又大又重、發(fā)熱量多的元器件,不宜裝在印制板上,而應(yīng)裝在整機(jī)的機(jī)箱底板上,且應(yīng)考慮散熱問題。熱敏元件應(yīng)遠(yuǎn)離發(fā)熱元件。

(4)對于電位器、可調(diào)電感線圈、可變電容器、微動(dòng)開關(guān)等可調(diào)元件的布局應(yīng)考慮整機(jī)的結(jié)構(gòu)要求。若是機(jī)內(nèi)調(diào)節(jié),應(yīng)放在印制板上方便于調(diào)節(jié)的地方;若是機(jī)外調(diào)節(jié),其位置要與調(diào)節(jié)旋鈕在機(jī)箱面板上的位置相適應(yīng)。

(5)應(yīng)留出印制扳定位孔及固定支架所占用的位置。

根據(jù)電路的功能單元,對電路的全部元器件進(jìn)行布局時(shí),要符合以下原則:

(1)按照電路的流程安排各個(gè)功能電路單元的位置,使布局便于信號流通,并使信號盡可能保持一致的方向。

(2)以每個(gè)功能電路的核心元件為中心,圍繞它來進(jìn)行布局。元器件應(yīng)均勻、 整齊、緊湊地排列在PCB上.盡量減少和縮短各元器件之間的引線和連接。

(3)在高頻下工作的電路,要考慮元器件之間的分布參數(shù)。一般電路應(yīng)盡可能使元器件平行排列。這樣,不但美觀.而且裝焊容易.易于批量生產(chǎn)。

(4)位于電路板邊緣的元器件,離電路板邊緣一般不小于2mm。電路板的最佳形狀為矩形。長寬比為3:2成4:3。電路板面尺寸大于200x150mm時(shí).應(yīng)考慮電路板所受的機(jī)械強(qiáng)度。

2.布線

布線的原則如下:

(1)輸入輸出端用的導(dǎo)線應(yīng)盡量避免相鄰平行。最好加線間地線,以免發(fā)生反饋藕合。

(2)印制攝導(dǎo)線的最小寬度主要由導(dǎo)線與絕緣基扳間的粘附強(qiáng)度和流過它們的電流值決定。當(dāng)銅箔厚度為 0.05mm、寬度為 1 ~ 15mm 時(shí).通過 2A的電流,溫度不會(huì)高于3℃,因此.導(dǎo)線寬度為1.5mm可滿足要求。對于集成電路,尤其是數(shù)字電路,通常選0.02~0.3mm導(dǎo)線寬度。當(dāng)然,只要允許,還是盡可能用寬線.尤其是電源線和地線。導(dǎo)線的最小間距主要由最壞情況下的線間絕緣電阻和擊穿電壓決定。對于集成電路,尤其是數(shù)字電路,只要工藝允許,可使間距小至5~8mm。

(3)印制導(dǎo)線拐彎處一般取圓弧形,而直角或夾角在高頻電路中會(huì)影響電氣性能。此外,盡量避免使用大面積銅箔,否則.長時(shí)間受熱時(shí),易發(fā)生銅箔膨脹和脫落現(xiàn)象。必須用大面積銅箔時(shí),最好用柵格狀.這樣有利于排除銅箔與基板間粘合劑受熱產(chǎn)生的揮發(fā)性氣體。

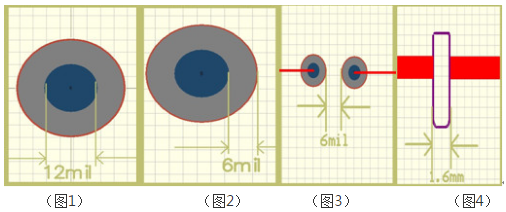

3.焊盤

焊盤中心孔要比器件引線直徑稍大一些。焊盤太大易形成虛焊。焊盤外徑D一般不小于(d+1.2)mm,其中d為引線孔徑。對高密度的數(shù)字電路,焊盤最小直徑可取(d+1.0)mm。

PCB及電路抗干擾措施

印制電路板的抗干擾設(shè)計(jì)與具體電路有著密切的關(guān)系,這里僅就PCB抗干擾設(shè)計(jì)的幾項(xiàng)常用措施做一些說明。

1.電源線設(shè)計(jì)

根據(jù)印制線路板電流的大小,盡量加租電源線寬度,減少環(huán)路電阻。同時(shí)、使電源線、地線的走向和數(shù)據(jù)傳遞的方向一致,這樣有助于增強(qiáng)抗噪聲能力。

2.地線設(shè)計(jì)

地線設(shè)計(jì)的原則是:

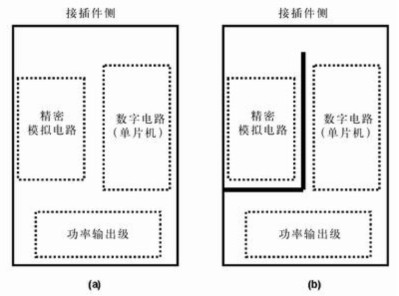

(1)數(shù)字地與模擬地分開。若線路板上既有邏輯電路又有線性電路,應(yīng)使它們盡量分開。低頻電路的地應(yīng)盡量采用單點(diǎn)并聯(lián)接地,實(shí)際布線有困難時(shí)可部分串聯(lián)后再并聯(lián)接地。高頻電路宜采用多點(diǎn)串聯(lián)接地,地線應(yīng)短而租,高頻元件周圍盡量用柵格狀大面積地箔。

(2)接地線應(yīng)盡量加粗。若接地線用很紉的線條,則接地電位隨電流的變化而變化,使抗噪性能降低。因此應(yīng)將接地線加粗,使它能通過三倍于印制板上的允許電流。如有可能,接地線應(yīng)在2~3mm以上。

(3)接地線構(gòu)成閉環(huán)路。只由數(shù)字電路組成的印制板,其接地電路布成團(tuán)環(huán)路大多能提高抗噪聲能力。

3.退藕電容配置

PCB設(shè)計(jì)的常規(guī)做法之一是在印制板的各個(gè)關(guān)鍵部位配置適當(dāng)?shù)耐伺弘娙荨?/p>

退藕電容的一般配置原則是:

(1)電源輸入端跨接10 ~100uf的電解電容器。如有可能,接100uF以上的更好。

(2)原則上每個(gè)集成電路芯片都應(yīng)布置一個(gè)0.01pF的瓷片電容,如遇印制板空隙不夠,可每4~8個(gè)芯片布置一個(gè)1 ~ 10pF的但電容。

(3)對于抗噪能力弱、關(guān)斷時(shí)電源變化大的器件,如 RAM、ROM存儲器件,應(yīng)在芯片的電源線和地線之間直接接入退藕電容。

(4)電容引線不能太長,尤其是高頻旁路電容不能有引線。

此外,還應(yīng)注意以下兩點(diǎn):

(1)在印制板中有接觸器、繼電器、按鈕等元件時(shí).操作它們時(shí)均會(huì)產(chǎn)生較大火花放電,必須采用附圖所示的 RC 電路來吸收放電電流。一般 R 取 1 ~ 2K,C取2.2 ~ 47UF。

(2)CMOS的輸入阻抗很高,且易受感應(yīng),因此在使用時(shí)對不用端要接地或接正電源。

7.實(shí)現(xiàn)PCB高效自動(dòng)布線的設(shè)計(jì)技巧和要點(diǎn)

盡管現(xiàn)在的EDA工具很強(qiáng)大,但隨著PCB尺寸要求越來越小,器件密度越來越高,PCB設(shè)計(jì)的難度并不小。如何實(shí)現(xiàn)PCB高的布通率以及縮短設(shè)計(jì)時(shí)間呢?本文介紹PCB規(guī)劃、布局和布線的設(shè)計(jì)技巧和要點(diǎn)。 現(xiàn)在PCB設(shè)計(jì)的時(shí)間越來越短,越來越小的電路板空間,越來越高的器件密度,極其苛刻的布局規(guī)則和大尺寸的組件使得設(shè)計(jì)師的工作更加困難。為了解決設(shè)計(jì)上的困難,加快產(chǎn)品的上市,現(xiàn)在很多廠家傾向于采用專用EDA工具來實(shí)現(xiàn)PCB的設(shè)計(jì)。但專用的EDA工具并不能產(chǎn)生理想的結(jié)果,也不能達(dá)到100%的布通率,而且很亂,通常還需花很多時(shí)間完成余下的工作。

現(xiàn)在市面上流行的EDA工具軟件很多,但除了使用的術(shù)語和功能鍵的位置不一樣外都大同小異,如何用這些工具更好地實(shí)現(xiàn)PCB的設(shè)計(jì)呢?在開始布線之前對設(shè)計(jì)進(jìn)行認(rèn)真的分析以及對工具軟件進(jìn)行認(rèn)真的設(shè)置將使設(shè)計(jì)更加符合要求。下面是一般的設(shè)計(jì)過程和步驟。

1、確定PCB的層數(shù)

電路板尺寸和布線層數(shù)需要在設(shè)計(jì)初期確定。如果設(shè)計(jì)要求使用高密度球柵數(shù)組(BGA)組件,就必須考慮這些器件布線所需要的最少布線層數(shù)。布線層的數(shù)量以及層疊(stack-up)方式會(huì)直接影響到印制線的布線和阻抗。板的大小有助于確定層疊方式和印制線寬度,實(shí)現(xiàn)期望的設(shè)計(jì)效果。

多年來,人們總是認(rèn)為電路板層數(shù)越少成本就越低,但是影響電路板的制造成本還有許多其它因素。近幾年來,多層板之間的成本差別已經(jīng)大大減小。在開始設(shè)計(jì)時(shí)最好采用較多的電路層并使敷銅均勻分布,以避免在設(shè)計(jì)臨近結(jié)束時(shí)才發(fā)現(xiàn)有少量信號不符合已定義的規(guī)則以及空間要求,從而被迫添加新層。在設(shè)計(jì)之前認(rèn)真的規(guī)劃將減少布線中很多的麻煩。

2、設(shè)計(jì)規(guī)則和限制

自動(dòng)布線工具本身并不知道應(yīng)該做些什幺。為完成布線任務(wù),布線工具需要在正確的規(guī)則和限制條件下工作。不同的信號線有不同的布線要求,要對所有特殊要求的信號線進(jìn)行分類,不同的設(shè)計(jì)分類也不一樣。每個(gè)信號類都應(yīng)該有優(yōu)先級,優(yōu)先級越高,規(guī)則也越嚴(yán)格。規(guī)則涉及印制線寬度、過孔的最大數(shù)量、平行度、信號線之間的相互影響以及層的限制,這些規(guī)則對布線工具的性能有很大影響。認(rèn)真考慮設(shè)計(jì)要求是成功布線的重要一步。

3、組件的布局

為最優(yōu)化裝配過程,可制造性設(shè)計(jì)(DFM)規(guī)則會(huì)對組件布局產(chǎn)生限制。如果裝配部門允許組件移動(dòng),可以對電路適當(dāng)優(yōu)化,更便于自動(dòng)布線。所定義的規(guī)則和約束條件會(huì)影響布局設(shè)計(jì)。

在布局時(shí)需考慮布線路徑(routing channel)和過孔區(qū)域。這些路徑和區(qū)域?qū)υO(shè)計(jì)人員而言是顯而易見的,但自動(dòng)布線工具一次只會(huì)考慮一個(gè)信號,通過設(shè)置布線約束條件以及設(shè)定可布信號線的層,可以使布線工具能像設(shè)計(jì)師所設(shè)想的那樣完成布線。

4、扇出設(shè)計(jì)

在扇出設(shè)計(jì)階段,要使自動(dòng)布線工具能對組件引腳進(jìn)行連接,表面貼裝器件的每一個(gè)引腳至少應(yīng)有一個(gè)過孔,以便在需要更多的連接時(shí),電路板能夠進(jìn)行內(nèi)層連接、在線測試(ICT)和電路再處理。

為了使自動(dòng)布線工具效率最高,一定要盡可能使用最大的過孔尺寸和印制線,間隔設(shè)置為50mil較為理想。要采用使布線路徑數(shù)最大的過孔類型。進(jìn)行扇出設(shè)計(jì)時(shí),要考慮到電路在線測試問題。測試夾具可能很昂貴,而且通常是在即將投入全面生產(chǎn)時(shí)才會(huì)訂購,如果這時(shí)候才考慮添加節(jié)點(diǎn)以實(shí)現(xiàn)100%可測試性就太晚了。

經(jīng)過慎重考慮和預(yù)測,電路在線測試的設(shè)計(jì)可在設(shè)計(jì)初期進(jìn)行,在生產(chǎn)過程后期實(shí)現(xiàn),根據(jù)布線路徑和電路在線測試來確定過孔扇出類型,電源和接地也會(huì)影響到布線和扇出設(shè)計(jì)。為降低濾波電容器連接線產(chǎn)生的感抗,過孔應(yīng)盡可能靠近表面貼裝器件的引腳,必要時(shí)可采用手動(dòng)布線,這可能會(huì)對原來設(shè)想的布線路徑產(chǎn)生影響,甚至可能會(huì)導(dǎo)致你重新考慮使用哪種過孔,因此必須考慮過孔和引腳感抗間的關(guān)系并設(shè)定過孔規(guī)格的優(yōu)先級。

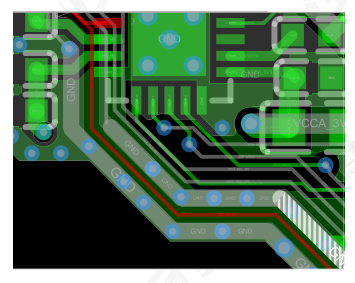

5、手動(dòng)布線以及關(guān)鍵信號的處理

盡管本文主要論述自動(dòng)布線問題,但手動(dòng)布線在現(xiàn)在和將來都是印刷電路板設(shè)計(jì)的一個(gè)重要過程。采用手動(dòng)布線有助于自動(dòng)布線工具完成布線工作。如圖2a和圖2b所示,通過對挑選出的網(wǎng)絡(luò)(net)進(jìn)行手動(dòng)布線并加以固定,可以形成自動(dòng)布線時(shí)可依據(jù)的路徑。

無論關(guān)鍵信號的數(shù)量有多少,首先對這些信號進(jìn)行布線,手動(dòng)布線或結(jié)合自動(dòng)布線工具均可。關(guān)鍵信號通常必須通過精心的電路設(shè)計(jì)才能達(dá)到期望的性能。布線完成后,再由有關(guān)的工程人員來對這些信號布線進(jìn)行檢查,這個(gè)過程相對容易得多。檢查通過后,將這些線固定,然后開始對其余信號進(jìn)行自動(dòng)布線。

6、自動(dòng)布線

對關(guān)鍵信號的布線需要考慮在布線時(shí)控制一些電參數(shù),比如減小分布電感和EMC等,對于其它信號的布線也類似。所有的EDA廠商都會(huì)提供一種方法來控制這些參數(shù)。在了解自動(dòng)布線工具有哪些輸入?yún)?shù)以及輸入?yún)?shù)對布線的影響后,自動(dòng)布線的質(zhì)量在一定程度上可以得到保證。

應(yīng)該采用通用規(guī)則來對信號進(jìn)行自動(dòng)布線。通過設(shè)置限制條件和禁止布線區(qū)來限定給定信號所使用的層以及所用到的過孔數(shù)量,布線工具就能按照工程師的設(shè)計(jì)思想來自動(dòng)布線。如果對自動(dòng)布線工具所用的層和所布過孔的數(shù)量不加限制,自動(dòng)布線時(shí)將會(huì)使用到每一層,而且將會(huì)產(chǎn)生很多過孔。

在設(shè)置好約束條件和應(yīng)用所創(chuàng)建的規(guī)則后,自動(dòng)布線將會(huì)達(dá)到與預(yù)期相近的結(jié)果,當(dāng)然可能還需要進(jìn)行一些整理工作,同時(shí)還需要確保其它信號和網(wǎng)絡(luò)布線的空間。在一部分設(shè)計(jì)完成以后,將其固定下來,以防止受到后邊布線過程的影響。

采用相同的步驟對其余信號進(jìn)行布線。布線次數(shù)取決于電路的復(fù)雜性和你所定義的通用規(guī)則的多少。每完成一類信號后,其余網(wǎng)絡(luò)布線的約束條件就會(huì)減少。但隨之而來的是很多信號布線需要手動(dòng)干預(yù)。現(xiàn)在的自動(dòng)布線工具功能非常強(qiáng)大,通常可完成100%的布線。但是當(dāng)自動(dòng)布線工具未完成全部信號布線時(shí),就需對余下的信號進(jìn)行手動(dòng)布線。

7、自動(dòng)布線的設(shè)計(jì)要點(diǎn)包括:

7.1 略微改變設(shè)置,試用多種路徑布線;

7.2 保持基本規(guī)則不變,試用不同的布線層、不同的印制線和間隔寬度以及不同線寬、不同類型的過孔如盲孔、埋孔等,觀察這些因素對設(shè)計(jì)結(jié)果有何影響;

7.3讓布線工具對那些默認(rèn)的網(wǎng)絡(luò)根據(jù)需要進(jìn)行處理;

7.4信號越不重要,自動(dòng)布線工具對其布線的自由度就越大。

8、布線的整理

如果你所使用的EDA工具軟件能夠列出信號的布線長度,檢查這些數(shù)據(jù),你可能會(huì)發(fā)現(xiàn)一些約束條件很少的信號布線的長度很長。這個(gè)問題比較容易處理,通過手動(dòng)編輯可以縮短信號布線長度和減少過孔數(shù)量。在整理過程中,你需要判斷出哪些布線合理,哪些布線不合理。同手動(dòng)布線設(shè)計(jì)一樣,自動(dòng)布線設(shè)計(jì)也能在檢查過程中進(jìn)行整理和編輯。

9、電路板的外觀

以前的設(shè)計(jì)常常注意電路板的視覺效果,現(xiàn)在不一樣了。自動(dòng)設(shè)計(jì)的電路板不比手動(dòng)設(shè)計(jì)的美觀,但在電子特性上能滿足規(guī)定的要求,而且設(shè)計(jì)的完整性能得到保證。

-

電源

+關(guān)注

關(guān)注

184文章

17583瀏覽量

249485 -

元器件

+關(guān)注

關(guān)注

112文章

4692瀏覽量

92000 -

PCB板

+關(guān)注

關(guān)注

27文章

1442瀏覽量

51508

原文標(biāo)題:不用找了!PCB設(shè)計(jì)注意事項(xiàng)及經(jīng)驗(yàn)大全都在這了

文章出處:【微信號:Mouser-Community,微信公眾號:貿(mào)澤電子設(shè)計(jì)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

PCB設(shè)計(jì)中對電流回路的注意事項(xiàng)

PCB參考設(shè)計(jì)規(guī)范 PCB設(shè)計(jì)注意事項(xiàng)

PCB設(shè)計(jì)有哪些注意事項(xiàng)!

PCB設(shè)計(jì)注意事項(xiàng)及經(jīng)驗(yàn)大全

混合信號PCB設(shè)計(jì)有什么注意事項(xiàng)?

pcb設(shè)計(jì)注意事項(xiàng)

淺談PCB板設(shè)計(jì)注意事項(xiàng)

觸摸按鍵測試板PCB設(shè)計(jì)注意事項(xiàng)

PCB設(shè)計(jì)涉及的參數(shù)及注意事項(xiàng)

PCB設(shè)計(jì)注意事項(xiàng)及經(jīng)驗(yàn)大全

PCB設(shè)計(jì)注意事項(xiàng)及經(jīng)驗(yàn)大全

評論