電子封裝是集成電路芯片生產(chǎn)完成后不可缺少的一道工序,是器件到系統(tǒng)的橋梁。封裝這一生產(chǎn)環(huán)節(jié)對(duì)微電子產(chǎn)品的質(zhì)量和競(jìng)爭(zhēng)力都有極大的影響。按目前國(guó)際上流行的看法認(rèn)為,在微電子器件的總體成本中,設(shè)計(jì)占了三分之一,芯片生產(chǎn)占了三分之一,而封裝和測(cè)試也占了三分之一,真可謂三分天下有其一。

封裝研究在全球范圍的發(fā)展是如此迅猛,而它所面臨的挑戰(zhàn)和機(jī)遇也是自電子產(chǎn)品問(wèn)世以來(lái)所從未遇到過(guò)的;封裝所涉及的問(wèn)題之多之廣,也是其它許多領(lǐng)域中少見(jiàn)的,它是從材料到工藝、從無(wú)機(jī)到聚合物、從大型生產(chǎn)設(shè)備到計(jì)算力學(xué)等一門(mén)綜合性非常強(qiáng)的新型高科技學(xué)科。

什么是封裝

封裝最初的定義是保護(hù)電路芯片免受周?chē)h(huán)境的影響(包括物理、化學(xué)的影響)。

芯片封裝是利用(膜技術(shù))及(微細(xì)加工技術(shù)),將芯片及其他要素在框架或基板上布置、粘貼固定及連接,引出接線端子并通過(guò)可塑性絕緣介質(zhì)灌封固定,構(gòu)成整體結(jié)構(gòu)的工藝。

電子封裝工程:將基板、芯片封裝體和分立器件等要素,按電子整機(jī)要求進(jìn)行連接和裝配,實(shí)現(xiàn)一定電氣、物理性能,轉(zhuǎn)變?yōu)榫哂姓麢C(jī)或系統(tǒng)形式的整機(jī)裝置或設(shè)備。

集成電路封裝能保護(hù)芯片不受或者少受外界環(huán)境的影響,并為之提供一個(gè)良好的工作條件,以使集成電路具有穩(wěn)定、正常的功能。

芯片封裝能實(shí)現(xiàn)電源分配;信號(hào)分配;散熱通道;機(jī)械支撐;環(huán)境保護(hù)。

封裝技術(shù)的層次:

第一層次,又稱為芯片層次的封裝,是指把集成電路芯片與封裝基板或引腳架之間的粘貼固定電路連線與封裝保護(hù)的工藝,使之成為易于取放輸送,并可與下一層次的組裝進(jìn)行連接的模塊元件。

第二層次,將數(shù)個(gè)第一層次完成的封裝與其他電子元器件組成一個(gè)電子卡的工藝。

第三層次,將數(shù)個(gè)第二層次完成的封裝組成的電路卡組合成在一個(gè)主電路版上使之成為一個(gè)部件或子系統(tǒng)的工藝。

第四層次,將數(shù)個(gè)子系統(tǒng)組裝成為一個(gè)完整電子廠品的工藝過(guò)程。

他們依次是芯片互連級(jí)(零級(jí)封裝)、一級(jí)封裝(多芯片組件)、二級(jí)封裝(PWB或卡)三級(jí)封裝(母板)。

封裝的分類(lèi)

按照封裝中組合集成電路芯片的數(shù)目,芯片封裝可分為:?jiǎn)涡酒庋b與多芯片封裝兩大類(lèi);

按照密封的材料區(qū)分,可分為高分子材料和陶瓷為主的種類(lèi);

按照器件與電路板互連方式,封裝可區(qū)分為引腳插入型和表面貼裝型兩大類(lèi);

按照引腳分布形態(tài)區(qū)分,封裝元器件有單邊引腳,雙邊引腳,四邊引腳,底部引腳四種。

常見(jiàn)的單邊引腳有單列式封裝與交叉引腳式封裝;

雙邊引腳元器件有雙列式封裝小型化封裝;

四邊引腳有四邊扁平封裝;

底部引腳有金屬罐式與點(diǎn)陣列式封裝。

封裝的名詞解釋

SIP:?jiǎn)瘟惺椒庋b SQP:小型化封裝 MCP:金屬鑵式封裝

DIP:雙列式封裝 CSP:芯片尺寸封裝 QFP:四邊扁平封裝

PGA:點(diǎn)陣式封裝 BGA:球柵陣列式封裝 LCCC:無(wú)引線陶瓷芯片載體

封裝技術(shù)的發(fā)展階段

半導(dǎo)體行業(yè)對(duì)芯片封裝技術(shù)水平的劃分存在不同的標(biāo)準(zhǔn),目前國(guó)內(nèi)比較通行的標(biāo)準(zhǔn)是采取封裝芯片與基板的連接方式來(lái)劃分,總體來(lái)講,集成電路封裝封裝技術(shù)的發(fā)展可分為四個(gè)階段:

第一階段:20世紀(jì)80年代以前(插孔原件時(shí)代)。

封裝的主要技術(shù)是針腳插裝(PTH),其特點(diǎn)是插孔安裝到PCB上,主要形式有SIP、DIP、PGA,它們的不足之處是密度、頻率難以提高,難以滿足高效自動(dòng)化生產(chǎn)的要求。

第二階段:20世紀(jì)80年代中期(表面貼裝時(shí)代)。

表面貼裝封裝的主要特點(diǎn)是引線代替針腳,引線為翼形或丁形,兩邊或四邊引出,節(jié)距為1.27到0.4mm,適合于3-300條引線,表面貼裝技術(shù)改變了傳統(tǒng)的PTH插裝形式,通過(guò)細(xì)微的引線將集成電路貼裝到PCB板上。主要形式為SOP(小外型封裝)、PLCC(塑料有引線片式載體)、PQFP(塑料四邊引線扁平封裝)、J型引線QFJ和SOJ、LCCC(無(wú)引線陶瓷芯片載體)等。它們的主要優(yōu)點(diǎn)是引線細(xì)、短,間距小,封裝密度提高;電氣性能提高;體積小,重量輕;易于自動(dòng)化生產(chǎn)。它們所存在的不足之處是在封裝密度、I/O數(shù)以及電路頻率方面還是難以滿足ASIC、微處理器發(fā)展的需要。

第三階段:20世紀(jì)90年代出現(xiàn)了第二次飛躍,進(jìn)入了面積陣列封裝時(shí)代。

該階段主要的封裝形式有焊球陣列封裝(BGA)、芯片尺寸封裝(CSP)、無(wú)引線四邊扁平封裝(PQFN)、多芯片組件(MCM)。BGA技術(shù)使得在封裝中占有較大體積和重量的管腳被焊球所替代,芯片與系統(tǒng)之間的連接距離大大縮短,BGA技術(shù)的成功開(kāi)發(fā),使得一直滯后于芯片發(fā)展的封裝終于跟上芯片發(fā)展的步伐。CSP技術(shù)解決了長(zhǎng)期存在的芯片小而封裝大的根本矛盾,引發(fā)了一場(chǎng)集成電路封裝技術(shù)的革命。

第四階段:進(jìn)入21世紀(jì),迎來(lái)了微電子封裝技術(shù)堆疊式封裝時(shí)代,它在封裝觀念上發(fā)生了革命性的變化,從原來(lái)的封裝元件概念演變成封裝系統(tǒng)。

目前,以全球半導(dǎo)體封裝的主流正處在第三階段的成熟期,PQFN和BGA等主要封裝技術(shù)進(jìn)行大規(guī)模生產(chǎn),部分產(chǎn)品已開(kāi)始在向第四階段發(fā)展。

微機(jī)電系統(tǒng)(MEMS)芯片就是采用堆疊式的三維封裝。

封裝工藝流程

1.封裝工藝流程 一般可以分為兩個(gè)部分,用塑料封裝之前的工藝步驟成為前段操作,在成型之后的工藝步驟成為后段操作

2.芯片封裝技術(shù)的基本工藝流程 硅片減薄 硅片切割 芯片貼裝,芯片互聯(lián) 成型技術(shù) 去飛邊毛刺 切筋成型 上焊錫打碼等工序

3.硅片的背面減薄技術(shù)主要有磨削,研磨,化學(xué)機(jī)械拋光,干式拋光,電化學(xué)腐蝕,濕法腐蝕,等離子增強(qiáng)化學(xué)腐蝕,常壓等離子腐蝕等

4.先劃片后減薄:在背面磨削之前將硅片正面切割出一定深度的切口,然后再進(jìn)行背面磨削。

5.減薄劃片:在減薄之前,先用機(jī)械或化學(xué)的方式切割處切口,然后用磨削方法減薄到一定厚度之后采用ADPE腐蝕技術(shù)去除掉剩余加工量實(shí)現(xiàn)裸芯片的自動(dòng)分離。

6.芯片貼裝的方式四種:共晶粘貼法,焊接粘貼法,導(dǎo)電膠粘貼法,和玻璃膠粘貼法。

共晶粘貼法:利用金-硅合金(一般是69%Au,31%的Si),363度時(shí)的共晶熔合反應(yīng)使IC芯片粘貼固定。

7.為了獲得最佳的共晶貼裝所采取的方法,IC芯片背面通常先鍍上一層金的薄膜或在基板的芯片承載座上先植入預(yù)芯片

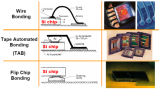

8.芯片互連常見(jiàn)的方法有,打線鍵合,載在自動(dòng)鍵合(TAB)和倒裝芯片鍵合。

9.打線鍵合技術(shù)有,超聲波鍵合,熱壓鍵合,熱超聲波鍵合。

10.TAB的關(guān)鍵技術(shù):1芯片凸點(diǎn)制作技術(shù)2TAB載帶制作技術(shù)3載帶引線與芯片凸點(diǎn)的內(nèi)引線焊接和載帶外引線焊接技術(shù)。

11.凸點(diǎn)芯片的制作工藝,形成凸點(diǎn)的技術(shù):蒸發(fā)/濺射涂點(diǎn)制作法,電鍍凸點(diǎn)制作法置球及模板印刷制作,焊料凸點(diǎn)發(fā),化學(xué)鍍涂點(diǎn)制作法,打球凸點(diǎn)制作法,激光法。

12.塑料封裝的成型技術(shù),1轉(zhuǎn)移成型技術(shù),2噴射成型技術(shù),3預(yù)成型技術(shù)但最主要的技術(shù)是轉(zhuǎn)移成型技術(shù),轉(zhuǎn)移技術(shù)使用的材料一般為熱固性聚合物。

13.減薄后的芯片有如下優(yōu)點(diǎn):1、薄的芯片更有利于散熱;2、減小芯片封裝體積;3、提高機(jī)械性能、硅片減薄、其柔韌性越好,受外力沖擊引起的應(yīng)力也越小;4、晶片的厚度越薄,元件之間的連線也越短,元件導(dǎo)通電阻將越低,信號(hào)延遲時(shí)間越短,從而實(shí)現(xiàn)更高的性能;5、減輕劃片加工量減薄以后再切割,可以減小劃片加工量,降低芯片崩片的發(fā)生率。

14. 波峰焊:波峰焊的工藝流程包括上助焊劑、預(yù)熱以及將PCB板在一個(gè)焊料波峰上通過(guò),依靠表面張力和毛細(xì)管現(xiàn)象的共同作用將焊劑帶到PCB板和元器件引腳上,形成焊接點(diǎn)。

波峰焊是將熔融的液態(tài)焊料,借助于泵的作用,在焊料槽液面形成特定形狀的焊料波,裝了元器件的PCB置于傳送鏈上,經(jīng)某一特定的角度以及一定的進(jìn)入深度穿過(guò)焊料波峰而實(shí)現(xiàn)焊點(diǎn)的焊接過(guò)程。

再流焊:是通過(guò)預(yù)先在PCB焊接部位施放適量和適當(dāng)形式的焊料,然后貼放表面組裝元器件,然后通過(guò)重新熔化預(yù)先分配到印制板焊盤(pán)上的焊膏,實(shí)現(xiàn)表面組裝元器件焊端或引腳與印制板焊盤(pán)之間機(jī)械與電氣連接的一種成組或逐點(diǎn)焊接工藝。

15.打線鍵合(WB):將細(xì)金屬線或金屬帶按順序打在芯片與引腳架或封裝基板的焊墊上形成電路互連。打線鍵合技術(shù)有超聲波鍵合、熱壓鍵合、熱超聲波鍵合。

載帶自動(dòng)鍵合(TAB):將芯片焊區(qū)與電子封裝外殼的I/O或基板上的金屬布線焊區(qū)用具有引線圖形金屬箔絲連接的技術(shù)工藝。

倒裝芯片鍵合(FCB):芯片面朝下,芯片焊區(qū)與基板焊區(qū)直接互連的一種方法。

16. 芯片互連:將芯片焊區(qū)與電子封裝外殼的I/O或基板上的金屬布線焊區(qū)相連接,只有實(shí)現(xiàn)芯片與封裝結(jié)構(gòu)的電路連接才能發(fā)揮已有的功能。

先進(jìn)封裝技術(shù)SIP

隨著物聯(lián)網(wǎng)時(shí)代和全球終端電子產(chǎn)品漸漸走向多功能整合及低功耗設(shè)計(jì),因而使得可將多顆裸晶整合在單一封裝中的SiP技術(shù)日益受到關(guān)注。除了既有的封測(cè)大廠積極擴(kuò)大SiP制造產(chǎn)能外,晶圓代工業(yè)者與IC基板廠也競(jìng)相投入此一技術(shù),以滿足市場(chǎng)需求。

SIP的定義

根據(jù)國(guó)際半導(dǎo)體路線組織(ITRS)的定義: SiP 為將多個(gè)具有不同功能的有源電子元件與可選無(wú)源器件,以及諸如 MEMS 或者光學(xué)器件等其他器件優(yōu)先組裝到一起,實(shí)現(xiàn)一定功能的單個(gè)標(biāo)準(zhǔn)封裝件,形成一個(gè)系統(tǒng)或者子系統(tǒng)。

因此,從架構(gòu)上來(lái)講, SiP 是將多種功能芯片,包括處理器、存儲(chǔ)器等功能芯片集成在一個(gè)封裝內(nèi),從而實(shí)現(xiàn)一個(gè)基本完整的功能。

SOC的定義

將原本不同功能的 IC,整合在一顆芯片中。藉由這個(gè)方法,不單可以縮小體積,還可以縮小不同 IC 間的距離,提升芯片的計(jì)算速度。SoC稱為系統(tǒng)級(jí)芯片,也有稱片上系統(tǒng),意指它是一個(gè)產(chǎn)品,是一個(gè)有專用目標(biāo)的集成電路,其中包含完整系統(tǒng)并有嵌入軟件的全部?jī)?nèi)容。同時(shí)它又是一種技術(shù),用以實(shí)現(xiàn)從確定系統(tǒng)功能開(kāi)始,到軟/硬件劃分,并完成設(shè)計(jì)的整個(gè)過(guò)程。

隨著封裝技術(shù)持續(xù)演進(jìn),加上終端電子產(chǎn)品朝向輕薄短小趨勢(shì),因此,對(duì)SiP需求亦逐漸提升。

SiP生產(chǎn)線須由基板、晶片、模組、封裝、測(cè)試、系統(tǒng)整合等生態(tài)系共同組成,才能夠順利發(fā)展。反之,若缺乏完整生態(tài)系,便難以推動(dòng)SiP技術(shù)具體實(shí)現(xiàn)。

由于SiP技術(shù)可將多種晶片封裝于單一封裝體內(nèi)而自成系統(tǒng),因此具有高整合性與微型化特色,適合應(yīng)用于體積小、多功能、低功耗等特性的電子產(chǎn)品。

以各種應(yīng)用來(lái)看,若將原本各自獨(dú)立的封裝元件改成以SiP技術(shù)整合,便能縮小封裝體積以節(jié)省空間,并縮短元件間的連接線路而使電阻降低,提升電性效果,最終呈現(xiàn)微小封裝體取代大片電路載板的優(yōu)勢(shì),又仍可維持各別晶片原有功能。因此,高整合性與微型化特色,使SiP成為近年來(lái)封裝技術(shù)發(fā)展趨勢(shì)。

此外,因SiP是將相關(guān)電路以封裝體完整包覆,因此可增加電路載板的抗化學(xué)腐蝕與抗應(yīng)力(Anti-stress)能力,可提高產(chǎn)品整體可靠性,對(duì)產(chǎn)品壽命亦能提升。

相較于SoC來(lái)說(shuō),SiP毋須進(jìn)行新型態(tài)晶片設(shè)計(jì)與驗(yàn)證,而是將現(xiàn)有不同功能的晶片,以封裝技術(shù)進(jìn)行整合 。

大致上來(lái)說(shuō),現(xiàn)階段SiP常用的基本封裝技術(shù),包括普遍應(yīng)用于智慧型手機(jī)的Package on Package(PoP)技術(shù),將邏輯IC與記憶體IC進(jìn)行封裝體堆疊。將主動(dòng)與被動(dòng)元件內(nèi)埋于基板的嵌入式技術(shù)(Embedded),以及多晶片封裝(MCP)、多晶片模組(MCM)、Stacking Die、PiP、TSV 2.5D IC、TSV 3D IC等,也屬于SiP技術(shù)范疇。

智慧型手機(jī)扮演SiP成長(zhǎng)驅(qū)動(dòng)主力

與個(gè)人電腦時(shí)代相比,行動(dòng)裝置產(chǎn)品對(duì)SiP的需求較為普遍 。就以智慧型手機(jī)來(lái)說(shuō),上網(wǎng)功能已是基本配備,因此與無(wú)線網(wǎng)路相關(guān)的Wi-Fi模組便會(huì)使用到SiP技術(shù)進(jìn)行整合。

基于安全性與保密性考量所發(fā)展出的指紋辨識(shí)功能,其相關(guān)晶片封裝亦需要SiP協(xié)助整合與縮小空間,使得指紋辨識(shí)模組開(kāi)始成為SiP廣泛應(yīng)用的市場(chǎng);另外,壓力觸控也是智慧型手機(jī)新興功能之一,內(nèi)建的壓力觸控模組(Force Touch)更是需要SiP技術(shù)的協(xié)助。

除此之外,將應(yīng)用處理器(AP)與記憶體進(jìn)行整合的處理器模組,以及與感測(cè)相關(guān)的MEMS模組等,亦是SiP技術(shù)的應(yīng)用范疇。

穿戴裝置/物聯(lián)網(wǎng)驅(qū)動(dòng)SiP需求上揚(yáng)

全球終端電子產(chǎn)品的發(fā)展不斷地朝向輕薄短小、多功能、低功耗等趨勢(shì)邁進(jìn), SiP的成長(zhǎng)潛力越來(lái)越大。2015年Apple Watch等穿戴式產(chǎn)品問(wèn)世后,SiP技術(shù)擴(kuò)及應(yīng)用到穿戴式產(chǎn)品。

此外, 在萬(wàn)物聯(lián)網(wǎng)的趨勢(shì)下,必然會(huì)串聯(lián)組合各種行動(dòng)裝置、穿戴裝置、智慧交通、智慧醫(yī)療,以及智慧家庭等網(wǎng)路,多功能異質(zhì)晶片整合預(yù)估將有龐大需求,低功耗也會(huì)是重要趨勢(shì)。

封裝技術(shù)作為信息產(chǎn)業(yè)的重要基礎(chǔ)在在產(chǎn)品中發(fā)揮著很大的作用。具體來(lái)說(shuō)有封裝市場(chǎng)巨大,決定產(chǎn)品性能、可靠性、壽命、成本等。現(xiàn)代電子信息產(chǎn)業(yè)的競(jìng)爭(zhēng)在某種意義上主要就是電子封裝業(yè)的競(jìng)爭(zhēng),它在一定程度上決定著現(xiàn)代工業(yè)化的水平。

-

集成電路

+關(guān)注

關(guān)注

5382文章

11396瀏覽量

360950 -

電路

+關(guān)注

關(guān)注

172文章

5852瀏覽量

171942 -

SiP

+關(guān)注

關(guān)注

5文章

500瀏覽量

105266 -

封裝

+關(guān)注

關(guān)注

126文章

7794瀏覽量

142741 -

soc

+關(guān)注

關(guān)注

38文章

4124瀏覽量

217966

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

人工智能半導(dǎo)體及先進(jìn)封裝技術(shù)發(fā)展趨勢(shì)

高功率半導(dǎo)體激光器的散熱秘籍:過(guò)渡熱沉封裝技術(shù)揭秘

一文解讀全球汽車(chē)半導(dǎo)體市場(chǎng)的未來(lái)發(fā)展

半導(dǎo)體封裝技術(shù)基礎(chǔ)詳解(131頁(yè)P(yáng)PT)

半導(dǎo)體封裝技術(shù)的類(lèi)型和區(qū)別

led封裝和半導(dǎo)體封裝的區(qū)別

養(yǎng)老院人員定位管理技術(shù)手段、作用及發(fā)展趨勢(shì)

知語(yǔ)科技反無(wú)人機(jī)技術(shù)手段有哪些?

半導(dǎo)體封裝技術(shù)的可靠性挑戰(zhàn)與解決方案

半導(dǎo)體發(fā)展的四個(gè)時(shí)代

易卜半導(dǎo)體創(chuàng)新推出Chiplet封裝技術(shù),彌補(bǔ)國(guó)內(nèi)技術(shù)空白,助力高算力芯片發(fā)展

知語(yǔ)云智能科技揭秘:光學(xué)干擾技術(shù)全景解讀

一文了解芯片封裝及底部填充(Underfill)技術(shù)(上)

半導(dǎo)體先進(jìn)封裝技術(shù)

揭秘DIP:半導(dǎo)體封裝技術(shù)的璀璨明珠

一文深度解讀半導(dǎo)體封裝技術(shù)原理、流程、技術(shù)手段

一文深度解讀半導(dǎo)體封裝技術(shù)原理、流程、技術(shù)手段

評(píng)論