人工智能(ArtificialIntelligence,AI)的概念早在上個(gè)世紀(jì)五十年代已經(jīng)出現(xiàn)。但是直到二十一世紀(jì),得益于深度學(xué)習(xí)算法的發(fā)展、硬件運(yùn)算力的提升、以及越來(lái)越多可供訓(xùn)練的樣本數(shù)據(jù)的獲得,人工智能才得到了真正的爆發(fā)。尤其是在圖像、視頻和語(yǔ)音識(shí)別方面的應(yīng)用,人工智能表現(xiàn)得愈發(fā)強(qiáng)大。支持強(qiáng)大的深度學(xué)習(xí)算法的背后,所依靠的是集成電路芯片的運(yùn)算能力。在性能和靈活性的取舍中,CPU、GPU、FPGA和ASIC分別有著不同的表現(xiàn)。其中定制的AI加速芯片往往能夠通過(guò)深度的軟硬件結(jié)合達(dá)到極致的能效比和吞吐量。本文分析了專用AI芯片的特點(diǎn),實(shí)現(xiàn)過(guò)程中性能、功耗、面積等方面的挑戰(zhàn),以及應(yīng)對(duì)這些挑戰(zhàn)的解決方案。

人工智能是一個(gè)非常廣泛的領(lǐng)域,也并不是一個(gè)新的概念。早在上世紀(jì)50年代,也就是計(jì)算機(jī)誕生不久,就已經(jīng)有不少學(xué)者開(kāi)始了這方面的研究,發(fā)展出了非常多的分支科。近十年來(lái),這一名詞更多地被提及則是因?yàn)樯疃葘W(xué)習(xí)領(lǐng)域取得的巨大進(jìn)展,掀起了從算法、軟件層面一直到硬件、芯片層面的不斷創(chuàng)新。

Source:https://www.edureka.co/blog/what-is-deep-learning

圖一

圖一展示了人工智能涉及到的三個(gè)領(lǐng)域之間的關(guān)系:

1.人工智能(Artificial Intelligence,AI),是研究使計(jì)算機(jī)來(lái)模擬人的思維過(guò)程和智能行為的學(xué)科,是最廣義的一個(gè)概念,包括模式識(shí)別、規(guī)劃推理、復(fù)雜系統(tǒng)、專家系統(tǒng)、模糊控制、自然語(yǔ)言處理等非常多的研究領(lǐng)域。但是現(xiàn)階段能夠?qū)崿F(xiàn)的人工智能實(shí)際上并不真正擁有思維,只是表現(xiàn)起來(lái)類似人的行為,仍然屬于弱人工智能的范疇。

2.機(jī)器學(xué)習(xí)(Machine Learning,ML),是人工智能的一個(gè)分支,研究如何讓計(jì)算機(jī)不通過(guò)顯式的編程而通過(guò)數(shù)據(jù)進(jìn)行自主學(xué)習(xí)的能力。人工神經(jīng)網(wǎng)絡(luò)是這一領(lǐng)域眾多算法的其中一個(gè),一度并沒(méi)有得到比較大的發(fā)展,直到深度神經(jīng)網(wǎng)絡(luò)算法的出現(xiàn)。

3.深度學(xué)習(xí)(Deep Learning,DL)是機(jī)器學(xué)習(xí)的一個(gè)分支,同時(shí)也是二十一世紀(jì)人工智能爆發(fā)的最大的推手。深度學(xué)習(xí)是利用深度神經(jīng)網(wǎng)絡(luò)(DeepNeuralNetwork,DNN)來(lái)解決特征表達(dá)的一種學(xué)習(xí)過(guò)程。在圖像、視頻、語(yǔ)音識(shí)別領(lǐng)域,最新的深度學(xué)習(xí)算法已經(jīng)做到了比人類更好的表現(xiàn)。這來(lái)源于深度神經(jīng)網(wǎng)絡(luò)更多級(jí)數(shù)的隱藏層,如圖二所示:

Source:https://www.quora.com/What-is-the-difference-between-Neural-Networks-and-Deep-Learning

圖二

這些隱藏層互相連接,使得輸入信息的特征能夠被識(shí)別、提取和傳播。如圖三所示,過(guò)去幾年主流的神經(jīng)網(wǎng)絡(luò)的層數(shù)和所需參數(shù)的數(shù)量呈現(xiàn)快速增長(zhǎng)的趨勢(shì)。比如,2015年的Residual Net可以達(dá)到152層,所有參數(shù)加起來(lái)超過(guò)1.5億個(gè)。

Source:http://speech.ee.ntu.edu.tw/~tlkagk/talk.html

圖三

這帶來(lái)的問(wèn)題主要是什么呢?是計(jì)算量的激增!神經(jīng)網(wǎng)絡(luò)的訓(xùn)練是通過(guò)用大量的樣本數(shù)據(jù),對(duì)每一個(gè)參數(shù)做梯度下降、反向傳播等迭代計(jì)算,從而逐步確從而逐步確定所有的參數(shù)值。對(duì)于龐大參數(shù)量的神經(jīng)網(wǎng)絡(luò),可想而知計(jì)算量會(huì)是一個(gè)天文數(shù)字。即使是訓(xùn)練完的模型想要使用,也必然躲不開(kāi)大量的卷積、矩陣乘法等運(yùn)算,計(jì)算量依然不小。

一、人工智能芯片的目的

為了在可接受的功耗、成本限制下,解決深度學(xué)習(xí)巨大計(jì)算量的問(wèn)題,人們開(kāi)始設(shè)計(jì)研究專用的人工智能加速芯片。需要注意的是,人工智能芯片(或AI芯片)并不是芯片本身具有智能,而是用于加速深度學(xué)習(xí)算法的一種專用加速芯片。那么我們?yōu)槭裁床挥脗鹘y(tǒng)的CPU來(lái)計(jì)算呢?這就涉及到性能和靈活性之間的矛盾。

圖四列出了幾種不同類型用于計(jì)算的芯片。橫軸是性能,縱軸是靈活性。

Source: https://cloud.tencent.com/developer/article/1006018

圖四

前面我們已經(jīng)知道,深度學(xué)習(xí)巨大的運(yùn)算量,大多數(shù)是乘法和加法,那么普通的CPU就足以完成任務(wù)。事實(shí)上也確實(shí)是這樣的。早期在神經(jīng)網(wǎng)規(guī)模不大的時(shí)候人們的確是用CPU進(jìn)行運(yùn)算的。但是CPU有一個(gè)很大問(wèn)題,就是運(yùn)算性能比較低。相對(duì)于動(dòng)則幾百萬(wàn)參數(shù)的神經(jīng)網(wǎng)絡(luò)來(lái)說(shuō),計(jì)算能力嚴(yán)重不足。這是因?yàn)镃PU的強(qiáng)項(xiàng)是并不是運(yùn)算,而是邏輯,比如分支預(yù)測(cè)。CPU作為通用處理器靈活性是極佳的,不考慮性能的話,理論上可以運(yùn)行任意結(jié)構(gòu)的深度學(xué)習(xí)算法。

GPU大規(guī)模的并行運(yùn)算使得其計(jì)算能力顯著高于CPU。并且GPU的設(shè)計(jì)也使得它可以承擔(dān)通用的科學(xué)計(jì)算,具有不錯(cuò)的靈活性。但是這些通用性也使得它在功耗上的表現(xiàn)并不能令人滿意,同時(shí)成本也非常高昂。

要追求極致的功耗、性能、成本,只能為深度學(xué)習(xí)算法量身定制專用的加速芯片,即ASIC。由于是專用芯片,幾乎就沒(méi)有太多的靈活性了。AI芯片所有的軟硬件優(yōu)化都是為了某些特定的深度學(xué)習(xí)算法所定制的。但是也正是由于專用的原因,可以不用考慮那些為了通用性所作出的妥協(xié),提高性能、功耗方面的表現(xiàn)。

當(dāng)然還有一種為大家所熟知的方案,就是FPGA,試圖在性能和靈活性當(dāng)中找到一個(gè)新的平衡點(diǎn)。

所以需不需要AI芯片?其實(shí)是性能和靈活性的一種權(quán)衡。當(dāng)我們需要計(jì)算更快、功耗更小、成本更低的芯片的時(shí)候,AI芯片就是我們唯一的選擇。

需要注意的是,這里所說(shuō)的性能,指的并不是只我們通常所說(shuō)的“主頻”。它包括兩方面的考量。

首先是能效,指的是,在一定的功耗下,單位時(shí)間能提供的運(yùn)算次數(shù)。

其次是吞吐量。深度學(xué)習(xí)算法主要的計(jì)算是矩陣的乘法、加法。這種極其規(guī)律的算法本身就是高度結(jié)構(gòu)化的。所以人們充分利用這種結(jié)構(gòu)化,提高硬件的效率和并行度,使得在主頻相同的情況下,數(shù)據(jù)的吞吐量大幅提高。

二、人工智能芯片的應(yīng)用

在很多場(chǎng)景下,即使是終端設(shè)備,我們也是需要這樣的專用AI芯片的。比如無(wú)人駕駛汽車,并不能依賴于數(shù)據(jù)上傳服務(wù)器,計(jì)算完成后再下載結(jié)果。汽車需要實(shí)時(shí)的、極低延遲的反應(yīng)。再比如終端設(shè)備,它的特性決定了我們不可能使用大功耗的GPU,同時(shí)對(duì)芯片成本也有比較嚴(yán)格的要求。

人工智能芯片的應(yīng)用場(chǎng)景可以分為以下4種情形,如圖五所示。

圖五

縱軸分為推理(Inference)和訓(xùn)練(Training)。橫軸分為終端(Device)和云端(Cloud)。其中終端推理和云端訓(xùn)練是應(yīng)用最為廣泛的兩個(gè)場(chǎng)景。不僅是傳統(tǒng)互聯(lián)網(wǎng)和半導(dǎo)體巨頭們,近年來(lái)涌現(xiàn)了眾多的初創(chuàng)公司在這AI芯片這個(gè)領(lǐng)域發(fā)力。其中包括越來(lái)越多的中國(guó)的初創(chuàng)公司正在進(jìn)入這個(gè)市場(chǎng)。

從市場(chǎng)劃分來(lái)看,又可以分為下面五個(gè)方向,如圖六所示(數(shù)據(jù)來(lái)源47家AI初創(chuàng)公司)。

·視覺(jué)增強(qiáng)(含安防監(jiān)控)

·深度學(xué)習(xí)

·語(yǔ)音識(shí)別

·云

圖六

三、人工智能芯片實(shí)現(xiàn)的挑戰(zhàn)

人工智能芯片在失去一些靈活性的條件下,盡可能達(dá)到更高的能效、吞吐量,更低的延遲和成本。因此從指標(biāo)上來(lái)說(shuō),AI芯片實(shí)現(xiàn)過(guò)程中的挑戰(zhàn)依然來(lái)源于:

1.性能(Performance)

2.功耗(Power)

3.面積(Area)

但是AI芯片的特點(diǎn)使得我們可以觀察到它與其他類型芯片不同的一些挑戰(zhàn)。結(jié)合這一特點(diǎn),所應(yīng)用的實(shí)現(xiàn)方法也更具有針對(duì)性。

1.性能的挑戰(zhàn)自然是源于對(duì)AI芯片極致指標(biāo)的追求。

由于AI芯片重運(yùn)算和流水線設(shè)計(jì)的特征,加上眾多的旁路設(shè)計(jì),時(shí)序路徑上,數(shù)據(jù)通路(Datapath)的長(zhǎng)短差異非常明顯。到達(dá)同一個(gè)寄存器的路徑有的很長(zhǎng)但有的很短。這都導(dǎo)致當(dāng)把時(shí)鐘頻率推到極限的情況下,時(shí)序非常難以收斂。同時(shí),由于芯片面積的極致優(yōu)化,會(huì)導(dǎo)致density和congestion變得更高,使得時(shí)序優(yōu)化捉襟見(jiàn)肘。無(wú)論是buffer的插入、cell的upsize都受到空間的局限。對(duì)于Setup Check來(lái)說(shuō),useful skew是必不可少的優(yōu)化手段,如圖七所示。

圖七

但是useful skew的使用,在優(yōu)化了setup timing的同時(shí),大量的時(shí)鐘偏斜也導(dǎo)致hold check變得更加難以修復(fù)。

在面積緊縮的條件下,工具勢(shì)必不得不通過(guò)輾轉(zhuǎn)騰挪,把繞線資源緊缺,也就是congestion嚴(yán)重的地方的standard cell推開(kāi),使其變得稀疏來(lái)緩解congestion的問(wèn)題。而繞線資源不那么緊缺的地方,standard cell的密度就相應(yīng)變得更高。而這些區(qū)域,hold timing的修復(fù)會(huì)變得更為困難,因?yàn)樾辢old 通常是通過(guò)增加delay cell來(lái)實(shí)現(xiàn)的,需要足夠的空間。

制約性能的挑戰(zhàn)還包括時(shí)鐘樹帶來(lái)的影響。AI芯片大量的寄存器堆使得它需要一個(gè)足夠大的時(shí)鐘樹來(lái)驅(qū)動(dòng)這些同步電路。當(dāng)芯片density比較低的時(shí)候,時(shí)鐘樹的插入不會(huì)帶來(lái)太大的影響。但是極致的面積要求導(dǎo)致哪怕是幾千個(gè)buffer的插入,也會(huì)對(duì)timing產(chǎn)生比較大的跳變,即Pre-CTS和Post-CTS的correlation問(wèn)題。

要解決這個(gè)問(wèn)題,需要工具能夠在CTS之前就做出對(duì)于真實(shí)時(shí)鐘樹的預(yù)測(cè),在Pre-CTS優(yōu)化的時(shí)候就把時(shí)鐘樹這一重要因素考慮進(jìn)去。這不僅僅可以幫助工具更早地看到時(shí)鐘樹buffer所占的空間,還可以更精準(zhǔn)地對(duì)useful skew做出預(yù)判。

Clock Gating目前仍然是對(duì)于降低動(dòng)態(tài)功耗最有效的方法之一。AI芯片自然也不會(huì)吝嗇對(duì)于Clock Gating的使用。Clock Gating Cell(通常是Integrated Clock Gate,ICG)的enable path常常是時(shí)序優(yōu)化的瓶頸。特別是高層ICG的時(shí)序,如果在Pre-CTS階段不做一些額外處理的話,是難以修復(fù)的(圖八)。這依然是要求工具能夠提前對(duì)真實(shí)時(shí)鐘樹有一個(gè)預(yù)估,對(duì)useful skew的使用有所選擇。

圖八

2.AI芯片在功耗的表現(xiàn)上有幾個(gè)特點(diǎn):

1)動(dòng)態(tài)功耗占據(jù)主導(dǎo)(圖九)

當(dāng)然,根據(jù)芯片設(shè)計(jì)、流片工藝和signoffcorner的不同,功耗也會(huì)有不同的變化。但是動(dòng)態(tài)功耗相比于靜態(tài)功耗,在AI芯片中的占比是要高得多的。比如,一個(gè)典型的比例是,動(dòng)態(tài)功耗要占到總功耗的80%。這就意味著我們?cè)趯?shí)現(xiàn)的過(guò)程中,可以給與動(dòng)態(tài)功耗以更高的優(yōu)先級(jí)。

圖九

還有一點(diǎn)值得注意的是,動(dòng)態(tài)功耗由兩部分組成:開(kāi)關(guān)功耗(SwitchingPower)和內(nèi)部功耗(InternalPower)。開(kāi)關(guān)功耗指的是net上由于高低電平翻轉(zhuǎn),對(duì)負(fù)載電容充放電所帶來(lái)的功耗。內(nèi)部功耗則是standardcell內(nèi)部翻轉(zhuǎn)過(guò)程中產(chǎn)生的功耗,包括CMOS瞬時(shí)短路電流帶來(lái)的功耗和cell內(nèi)部的電容負(fù)載的功耗。AI芯片中的開(kāi)關(guān)功耗和內(nèi)部功耗更趨向于接近1:1的比例。也就意味著,除了通過(guò)對(duì)面積減少,降低transition來(lái)優(yōu)化內(nèi)部功耗之外,在開(kāi)關(guān)功耗的優(yōu)化上也有大量的工作可以做。比如,可以減少繞線的長(zhǎng)度,可以restructure、pin swapping等邏輯優(yōu)化。Innovus 18.1最新的版本有很多這些特殊處理的地方!

2)極不平衡的翻轉(zhuǎn)率

關(guān)于功耗的另一個(gè)特點(diǎn)是net上的翻轉(zhuǎn)率是極不平衡的。為了盡可能接近芯片真實(shí)的工作場(chǎng)景,翻轉(zhuǎn)率的數(shù)值應(yīng)該通過(guò)對(duì)網(wǎng)表的仿真,得到波形(VCD文件),然后折算出net的翻轉(zhuǎn)率(TCF或者SAIF文件)。對(duì)于AI芯片來(lái)說(shuō),仿真應(yīng)當(dāng)運(yùn)行真實(shí)場(chǎng)景中的深度學(xué)習(xí)算法。算法通常涉及到多個(gè)步驟(讀寫、卷積、池化……),則需要對(duì)各個(gè)步驟根據(jù)所運(yùn)行時(shí)間的比例,求取加權(quán)平均后的求取加權(quán)平均后的翻轉(zhuǎn)率。這樣可以比較準(zhǔn)確地反映出芯片工作時(shí)的平均動(dòng)態(tài)功耗。

通過(guò)這種方法的到的翻轉(zhuǎn)率,可以明顯觀察到,不同net直接的翻轉(zhuǎn)率有著天壤之別(圖十)。有一部分net翻轉(zhuǎn)率非常高,幾乎和時(shí)鐘頻率相近。他們幾乎一直處于翻轉(zhuǎn)的狀態(tài)。而有一部分net的翻轉(zhuǎn)率非常低,很久才翻轉(zhuǎn)一次。甚至在典型的深度學(xué)習(xí)算法運(yùn)行過(guò)程中,一次也沒(méi)有翻轉(zhuǎn)過(guò),是一些非常安靜的net。

圖十

對(duì)于如此不同的net,我們?cè)趦?yōu)化的時(shí)候自然不能一視同仁。一個(gè)很自然的想法就是,對(duì)于高翻轉(zhuǎn)率的net,希望工具能盡可能減小它的線長(zhǎng),從而降低負(fù)載電容。這樣它在不停地翻轉(zhuǎn)時(shí),開(kāi)關(guān)功耗可以小一些。而對(duì)于非常安靜的那些net,即使繞線長(zhǎng)度長(zhǎng)一些,只要并沒(méi)有帶來(lái)timing的問(wèn)題,也是可以接受的。并不需要?jiǎng)佑妙~外的資源去優(yōu)化這些net。因?yàn)樗麄兊姆D(zhuǎn)并不會(huì)花費(fèi)多少功耗。

AI芯片的對(duì)于大吞吐量的追求使得它通常擁有流水線結(jié)構(gòu)和并行的總線。如果可以充分利用這種結(jié)構(gòu)也能夠進(jìn)一步優(yōu)化動(dòng)態(tài)功耗的表現(xiàn)。一個(gè)例子是,如果我們把版圖上位置相近并且功能相同的寄存器替換為Multi-bit Flip Flop(圖十一),動(dòng)態(tài)功耗,特別是clock上的動(dòng)態(tài)功耗是可以減少的。

圖十一

之所以要求位置相近是因?yàn)椴幌M鎿Q對(duì)timing帶來(lái)影響。根據(jù)情況的不同,可以是2-bit、4-bit甚至8-bit的替換。這一點(diǎn)對(duì)于AI芯片并不難實(shí)現(xiàn)。因?yàn)榭偩€上的寄存器在版圖上的分布,由于前后連接關(guān)系的相似性常常會(huì)聚攏成堆,甚至多個(gè)寄存器在place之后自動(dòng)就形成一個(gè)陣列。那很多MBFF的替換原地就可以進(jìn)行,而對(duì)timing和routing不會(huì)帶來(lái)什么影響。工具需要能夠自動(dòng)完成這一替換,并且在后續(xù)的時(shí)序優(yōu)化中正確處理這些cell,在需要分拆的時(shí)候還原成單個(gè)寄存器。

3. AI芯片面積上的挑戰(zhàn)表現(xiàn)在density和congestion上。

下圖是幾種類型芯片網(wǎng)表結(jié)構(gòu)上的橫向?qū)Ρ龋?/p>

比如FlipFlop Ratio對(duì)比:

圖十二

(欲知其他特性詳情,請(qǐng)參加Cadence/ARM聯(lián)合研討會(huì))。

AI芯片以上的特點(diǎn),對(duì)工具應(yīng)對(duì)high density、high congestion的能力提出了巨大的挑戰(zhàn)。不僅要處理局部的routingcongestion,還需要面對(duì)全局的大面積擁塞。在確保routing沒(méi)有問(wèn)題的情況下,時(shí)序的功耗的目標(biāo)仍然需要滿足。

不同的Floorplan會(huì)對(duì)congestion以及timing的格局帶來(lái)完全不同的變化。對(duì)極限指標(biāo)的追求還需要從Floorplan上著手。需要工具提供更加自動(dòng)、智能的方法,幫助Floorplan的優(yōu)化,并且這種優(yōu)化是需要全局考慮性能、功耗和面積的。

四、人工智能芯片實(shí)現(xiàn)的解決方案

針對(duì)前一節(jié)分析得出了AI芯片的特點(diǎn),以及實(shí)現(xiàn)過(guò)程中的各種挑戰(zhàn),本節(jié)介紹了基于Cadence數(shù)字后端實(shí)現(xiàn)平臺(tái)Innovus的優(yōu)化解決方案,幫助芯片設(shè)計(jì)者更快地收斂到預(yù)期的性能、功耗和面積目標(biāo)。

對(duì)于AI芯片開(kāi)關(guān)功耗占比較多、翻轉(zhuǎn)率差異較大的特點(diǎn),基于真實(shí)仿真翻轉(zhuǎn)率文件(Activity File)的動(dòng)態(tài)功耗優(yōu)化是非常重要的。在翻轉(zhuǎn)率驅(qū)動(dòng)的功耗優(yōu)化方案上,最新的Innovus 18.1版本有著諸多的特性。比如:

·Power Optimization (activity-driven)

·Activity-Driven Placement

·Slack and Power-driven Placement

·Clock Power-Driven Placement

·High power effort CCopt

·Power-Driven Routing

·…

這里展示了在某款A(yù)I芯片核心模塊上,逐步開(kāi)啟幾種優(yōu)化手段所得到的最終signoff功耗結(jié)果。

圖十三

從結(jié)果可以看到,動(dòng)態(tài)功耗得到了顯著的降低。特別是SPP和CPD,充分利用了翻轉(zhuǎn)率文件提供的信息,優(yōu)先考慮高翻轉(zhuǎn)率的Net,使其線長(zhǎng)更短,降低功耗負(fù)載。而對(duì)于低翻轉(zhuǎn)率的Net,允許放松線長(zhǎng)的約束。

因此在沒(méi)有影響timing的情況下,可以獲得明顯的開(kāi)關(guān)功耗的優(yōu)化。(更多的數(shù)據(jù)分析和細(xì)節(jié)展示,請(qǐng)參加Cadence和ARM的聯(lián)合研討會(huì)了解詳情)

然后,讓我們看看Innovus對(duì)于Congestion的解決方案。

正如前文的分析,AI芯片中大量的FlipFlop和多管腳單元,加上極致的面積目標(biāo),所以congestion往往變成了壓死性能的最大的稻草。

圖十四顯示了版圖的大部分區(qū)域都有非常嚴(yán)重的congestion問(wèn)題。這種大范圍的congestion是很難通過(guò)單純的router的優(yōu)化來(lái)解決的。更需要placer和router的相互配合,在flow的各個(gè)階段通過(guò)對(duì)congestion的評(píng)估、把high congestion的區(qū)域cell density變得稀疏,同時(shí)保證timing得以滿足。

圖十四

從圖十五可以看到,Innovus的High effort congestion repair非常好地給出了我們所期待的結(jié)果。中間congestion最嚴(yán)重的區(qū)域(紅色的congestion marker),cell被盡量推開(kāi)了,density降到很低(灰色部分)。推開(kāi)的cell向四周擠進(jìn)了congestion并不嚴(yán)重的區(qū)域。這些區(qū)域的density變得更高(黃色、綠色的部分),但是并沒(méi)有關(guān)系,因?yàn)檫@些區(qū)域的繞線比較少,不會(huì)對(duì)congestion造成太大的問(wèn)題。

圖十五

但是圖十五中在垂直方向的congestion依然過(guò)于嚴(yán)重了,雖然憑借Nanoroute的優(yōu)化仍然可以全部繞通,但是不可避免會(huì)產(chǎn)生routing 的detour和timing的損失。

然,何以解憂?這里會(huì)用到Innovus的一個(gè)獨(dú)門秘器,18.1亮點(diǎn)之一,行業(yè)唯一的解決方案。

效果如圖十六,Timing、Density和DRC都得到了明顯的提升。本來(lái)由于嚴(yán)重的congestion導(dǎo)致無(wú)法修復(fù)的大量Holdviolation也得以大幅改善。

·Performance:4%

·Wire Length :4.7%

·Area:0.3%

圖十六

-

芯片

+關(guān)注

關(guān)注

453文章

50387瀏覽量

421783 -

人工智能

+關(guān)注

關(guān)注

1791文章

46845瀏覽量

237535

原文標(biāo)題:研發(fā)分享:人工智能芯片的挑戰(zhàn)與實(shí)現(xiàn)

文章出處:【微信號(hào):gh_fca7f1c2678a,微信公眾號(hào):Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SOC芯片設(shè)計(jì)的挑戰(zhàn)與解決方案

邊緣計(jì)算的技術(shù)挑戰(zhàn)與解決方案

HTTP海外安全挑戰(zhàn)與解決方案:保護(hù)跨國(guó)數(shù)據(jù)傳輸

MCT8316A-設(shè)計(jì)挑戰(zhàn)和解決方案應(yīng)用說(shuō)明

MCF8316A-設(shè)計(jì)挑戰(zhàn)和解決方案應(yīng)用說(shuō)明

ai煙火檢測(cè)解決方案

瑞薩電子推出Reality AI Explorer Tier,用于開(kāi)發(fā)AI與TinyML解決方案

risc-v多核芯片在AI方面的應(yīng)用

自動(dòng)駕駛發(fā)展問(wèn)題及解決方案淺析

DC電源模塊在醫(yī)療設(shè)備中的應(yīng)用挑戰(zhàn)與解決方案

聯(lián)想集團(tuán)舉辦芯片創(chuàng)新發(fā)展研討會(huì),論道研發(fā)存算“芯”挑戰(zhàn)

邊緣AI開(kāi)發(fā)的挑戰(zhàn)及ST的解決方案

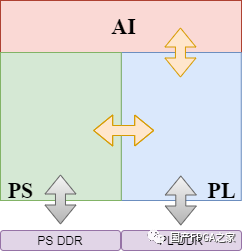

國(guó)產(chǎn)FPAI芯片的AI系統(tǒng)方案

淺析AI芯片的挑戰(zhàn)與解決方案

淺析AI芯片的挑戰(zhàn)與解決方案

評(píng)論