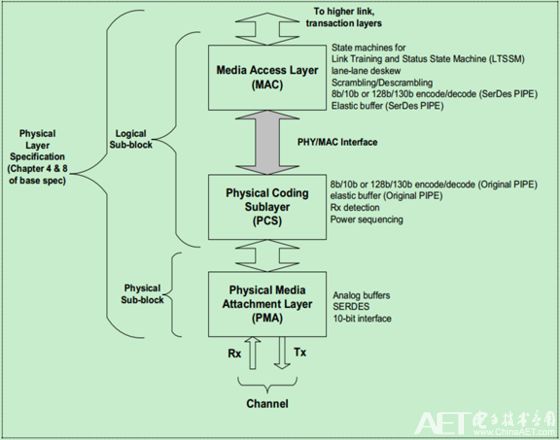

PCIe物理層接口(Physical Interface for PCI Express,PIPE)定義了物理層中的,媒介層(Media Access Layer,MAC)和物理編碼子層(Physical Coding Sub-layer,PCS)之間的統一接口,旨在為提供一種統一的行業標準。如下圖所示:

其中MAC和PCS都屬于PCIe中的物理層邏輯子層部分,而PMA(Physical Media Attachment Layer)則屬于物理層電氣子層。需要注意的是,PIPE規范是由Intel提出的行業建議,并非PCI-SIG規定的PCIe標準之一。PCIe設備廠家完全可以自主選擇是否采用PIPE規范。

由于業界通常采用SerDes器件(包括FPGA中集成的SerDes模塊)來實現PCIe中的PCS和PMA,所以往往MAC(以及事務層和數據鏈路層等)和PCS/PMA是獨立設計的,甚至是不同廠家設計的。為這之間提供統一的行業標準——PIPE,有助于使不同廠家之間的設備有更好的兼容性。當然,也有很多PCIe設備完全是由一個廠家設計的(如部分基于PCIe的ASIC等),此時是否采用PIPE的必要性就不是那么重要了。

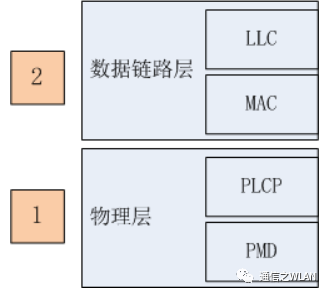

隨著高速串行技術的發展,各種串行通信技術的物理層逐漸走向了統一,用戶甚至可以基于FPGA中的SerDes/PCS完成多種高速串行通信接口的設計。這些通信接口的區別往往只是體現在高層協議(數據鏈路層與事務層等),在物理層上(尤其是物理層電氣子層上)基本上是一致的。

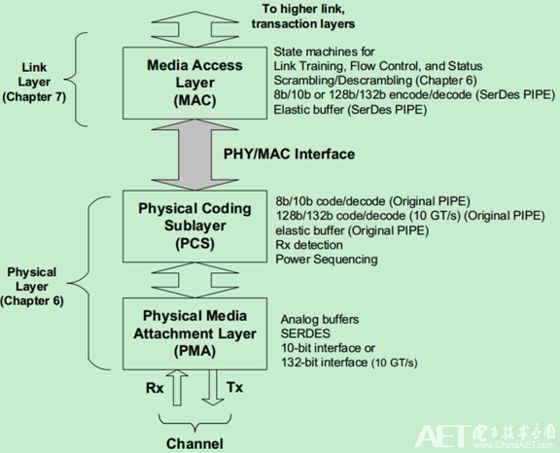

雖然PIPE規范最早是用于PCIe總線中的(從命名方式就可以看出來),但是該規范的后續版本逐漸開始支持了其他的串行接口。以Intel發布的最新版本的PIPE Spec為例(v5.1),該版本涉及PCI Express、SATA、USB、DisplayPort和Converged IO等多種高速串行接口。

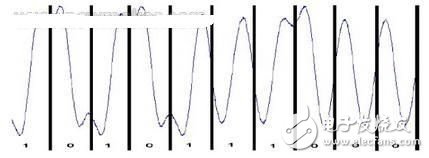

USB中的PHY/MAC接口,如下圖所示:

詳細的PHY/MAC接口(PIPE)的示意圖如下(PCIe、USB等):

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601805 -

PCIe

+關注

關注

15文章

1217瀏覽量

82436 -

物理層

+關注

關注

1文章

148瀏覽量

34286

原文標題:【博文連載】PCIe掃盲——PCI Express物理層接口(PIPE)

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CAN總線不同的物理層

什么是以太網物理層?Ethernet物理層有哪些功能?

WCDMA系統的物理層(FDD)

物理層網絡編碼分組的機會中繼

PCIe物理層的基本概念

WLAN物理層關鍵通信技術

PCIe物理層接口定義了物理層中的,媒介層和物理編碼子層之間的統一接口

PCIe物理層接口定義了物理層中的,媒介層和物理編碼子層之間的統一接口

評論