本文主要是關(guān)于tms320c6748的相關(guān)介紹,并著重tms320c6748的結(jié)構(gòu)進(jìn)行了詳盡的闡述。

tms320c6748

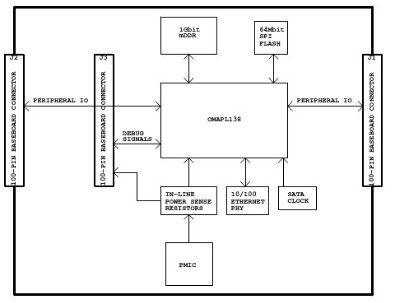

TMS320C6748是德州儀器 (TI) 推出浮點(diǎn)功能的全新高性能處理器 ,這款芯片也是業(yè)界功耗最低的浮點(diǎn)數(shù)字信號(hào)處理器 (DSP),可充分滿足高能效、連通性設(shè)計(jì)對(duì)高集成度外設(shè)、更低熱量耗散以及更長(zhǎng)電池使用壽命的需求。不僅具備通用并行端口 (uPP),同時(shí)也是 TI 首批集成串行高級(jí)技術(shù)附件 (SATA)的器件。 廣州創(chuàng)龍推出的TL6748-EVM評(píng)估套件為開(kāi)發(fā)者使用TI TMS320C6748處理器提供了完善的軟件開(kāi)發(fā)環(huán)境,系統(tǒng)支持:裸機(jī)、SYS/BIOS、DSP/BIOS。提供參考底板原理圖,DSP C6748入門教程、豐富的Demo程序、完整的軟件開(kāi)發(fā)包,以及詳細(xì)的C6748系統(tǒng)開(kāi)發(fā)文檔,方便用戶快速評(píng)估TMS320C6748處理器、設(shè)計(jì)系統(tǒng)驅(qū)動(dòng)及其定制應(yīng)用軟件,也大大降低產(chǎn)品開(kāi)發(fā)周期,讓客戶產(chǎn)品快速上市。主要面向電力、通信、工控、音視頻處理等數(shù)據(jù)采集處理行業(yè)。 TL6748-EVM評(píng)估套件是一個(gè)功能豐富的開(kāi)發(fā)板,為嵌入式設(shè)計(jì)人員提供快捷簡(jiǎn)單的實(shí)踐方式來(lái)評(píng)估TMS320C674x系列處理器,是一個(gè)完整的實(shí)驗(yàn)評(píng)估平臺(tái)。

德州儀器 (TI) 推出浮點(diǎn)功能的全新高性能處理器 —— TMS320C6748,這款芯片也是業(yè)界功耗最低的浮點(diǎn)數(shù)字信號(hào)處理器 (DSP),可充分滿足高能效、連通性設(shè)計(jì)對(duì)高集成度外設(shè)、更低熱量耗散以及更長(zhǎng)電池使用壽命的需求。不僅具備通用并行端口 (uPP),同時(shí)也是 TI 首批集成串行高級(jí)技術(shù)附件 (SATA)的器件。

廣州創(chuàng)龍推出的TL6748-EVM評(píng)估套件為開(kāi)發(fā)者使用TI TMS320C6748處理器提供了完善的軟件開(kāi)發(fā)環(huán)境,系統(tǒng)支持:裸機(jī)、SYS/BIOS、DSP/BIOS。提供參考底板原理圖,DSP C6748入門教程、豐富的Demo程序、完整的軟件開(kāi)發(fā)包,以及詳細(xì)的C6748系統(tǒng)開(kāi)發(fā)文檔,方便用戶快速評(píng)估TMS320C6748處理器、設(shè)計(jì)系統(tǒng)驅(qū)動(dòng)及其定制應(yīng)用軟件,也大大降低產(chǎn)品開(kāi)發(fā)周期,讓客戶產(chǎn)品快速上市。主要面向電力、通信、工控、音視頻處理等數(shù)據(jù)采集處理行業(yè)。

TL6748-EVM評(píng)估套件是一個(gè)功能豐富的開(kāi)發(fā)板,為嵌入式設(shè)計(jì)人員提供快捷簡(jiǎn)單的實(shí)踐方式來(lái)評(píng)估TMS320C674x系列處理器,是一個(gè)完整的實(shí)驗(yàn)評(píng)估平臺(tái)。

處理器

TMS320C6748圖冊(cè)TMS320C6748,C6000系列浮點(diǎn)DSP處理器(Pin to Pin兼容OMAPL138,AM1808處理器)

主頻:456MHz

存儲(chǔ)器

128M/256M/512MByte 工業(yè)級(jí)NAND Flash

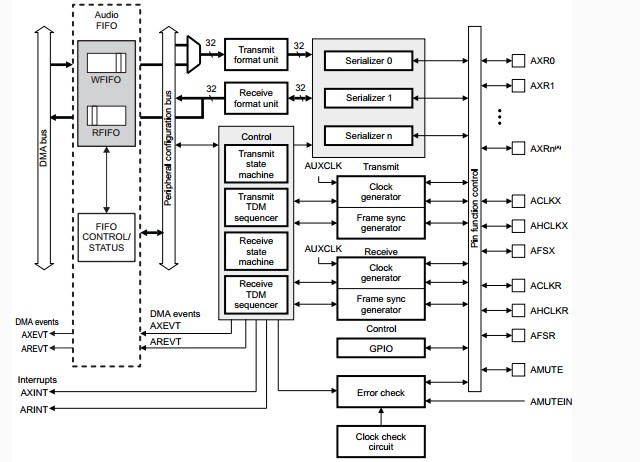

1個(gè)3.5mm Line in音頻輸入接口

1個(gè)3.5mm Mic in音頻輸入接口

1個(gè)3.5mm Line out音頻輸出接口

外設(shè)接口

串口、USB接口:

UART2,3線串口,RS232電平

1個(gè)RS485接口(RS485和UART1復(fù)用)

1 x USB2.0 OTG(Mini USB-B母座接口)

4 x USB1.1 HOST(2 x 雙層USB Type A座)

其他外設(shè)接口:

1個(gè)標(biāo)準(zhǔn)SD卡座(SD/MMC信號(hào),支持1.8V及3.3V邏輯電壓)

1個(gè)10/100Mbps以太網(wǎng)絡(luò)接口(RJ45連接器)

1個(gè)SATA接口(7pin SATA硬盤接口)

1個(gè)RTC座(RC1220 RTC座)

1 個(gè)JTAG接口(14Pin TI Rev B JTAG接口)

擴(kuò)展接口:(2x IDC3簡(jiǎn)易牛角座(2x 25pin規(guī)格))

1路SPI總線

1路IIC總線

1路UART信號(hào)

1路VPIF總線

1路uPP總線

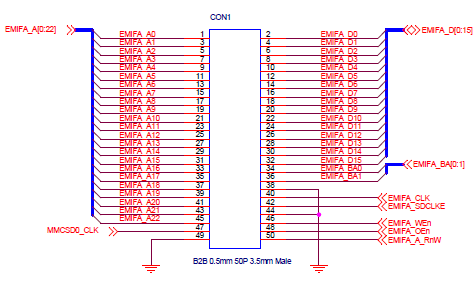

1路EMIF總線

可設(shè)置多個(gè)GPIO

輸入接口

1個(gè)非屏蔽中斷按鍵

1個(gè)可編程按鍵

1個(gè)復(fù)位按鍵

2個(gè)電源指示燈

1個(gè)系統(tǒng)指示燈

4個(gè)可編程指示燈

顯示單元

一個(gè)VGA接口

一個(gè)24bit真彩色LCD接口(50pinFPC排座;含4電阻式線觸摸屏接口,分辨率可支持1366x768)

電氣參數(shù)

工作電壓:3.8V~5.5V(典型值:5V)

工作溫度:-45~85℃

環(huán)境濕度:20% ~ 90% ,非冷凝

開(kāi)發(fā)板:180mm*130mm

核心板:55mm*33mm

電氣指標(biāo):+5V@150mA

核心板功耗

電壓:5V

電流:98mA

功耗:0.49W

淺談tms320c6748最小系統(tǒng)設(shè)計(jì)和cache配置

處理器的cache是一塊存儲(chǔ)靠近處理器數(shù)據(jù)的高速存儲(chǔ)區(qū)。這幫助常用的指令和數(shù)據(jù)的快速訪問(wèn)從而提高計(jì)算性能。Cache可以視為平坦式記憶體,即認(rèn)為cache是CPU靠近的可以很快訪問(wèn)的存儲(chǔ)器

存儲(chǔ)組織結(jié)構(gòu)

圖1的左邊的模型是一個(gè)平坦式記憶體系統(tǒng)架構(gòu),假設(shè)CPU和片內(nèi)存儲(chǔ)空間都運(yùn)行在300 MHz,存儲(chǔ)訪問(wèn)的延時(shí)只有在CPU訪問(wèn)外存的時(shí)候才存在,而memory stall不會(huì)在訪問(wèn)片內(nèi)存儲(chǔ)區(qū)時(shí)發(fā)生。如果CPU的頻率是600 MHz,那么在訪問(wèn)這部分片內(nèi)存儲(chǔ)區(qū)的時(shí)候還是存在等待周期的。不幸的是,想在片內(nèi)實(shí)現(xiàn)足夠大的存儲(chǔ)區(qū)能運(yùn)行在600 MHz會(huì)非常昂貴的,如果仍然讓片內(nèi)的存儲(chǔ)區(qū)運(yùn)行在300 MHz,那么訪問(wèn)這些存儲(chǔ)區(qū)的適合會(huì)有一個(gè)周期的延時(shí)。

一個(gè)解決方法是使用分層的存儲(chǔ)架構(gòu),有一個(gè)快速的靠近CPU的存儲(chǔ)區(qū),訪問(wèn)沒(méi)有stall但是size很小,往外的內(nèi)存空間很大,但是離CPU較遠(yuǎn),訪問(wèn)需要比較大的stall,靠近CPU的存儲(chǔ)區(qū)可以視為cache。

訪問(wèn)定位的規(guī)律

當(dāng)然,這種解決方案只有在CPU在大部分的訪問(wèn)都是只針對(duì)最靠近它的存儲(chǔ)區(qū)時(shí)才是有效的,幸運(yùn)的是,根據(jù)訪問(wèn)定位的規(guī)律,這一條可以保證。訪問(wèn)的定位規(guī)律表明程序在一個(gè)相對(duì)小的時(shí)間窗口對(duì)僅需要一個(gè)相對(duì)較小size的數(shù)據(jù)和代碼。數(shù)據(jù)定位的兩條規(guī)律:

?空間關(guān)聯(lián)性:當(dāng)一個(gè)數(shù)據(jù)被訪問(wèn)時(shí),它臨近的數(shù)據(jù)又很大可能會(huì)被后續(xù)的存儲(chǔ)訪問(wèn);

?時(shí)間關(guān)聯(lián)性:一個(gè)存儲(chǔ)區(qū)被訪問(wèn)時(shí),在下一個(gè)臨近的時(shí)間點(diǎn)還會(huì)被訪問(wèn)。

空間關(guān)聯(lián)性揭示了計(jì)算機(jī)程序的創(chuàng)建規(guī)律:通常情況下相關(guān)的數(shù)據(jù)被編譯鏈接到臨近的連續(xù)區(qū)域。例如首先處理一個(gè)數(shù)組的第一個(gè)元素,然后處理第二個(gè),這就是空間關(guān)聯(lián)性。類似的,時(shí)間關(guān)聯(lián)性主要源于程序中存在占用時(shí)間非常多的循環(huán),通常循環(huán)的代碼被連續(xù)執(zhí)行非常多次,一般循環(huán)內(nèi)訪問(wèn)的數(shù)據(jù)也相當(dāng)。

圖2是空間關(guān)聯(lián)性的說(shuō)明,一個(gè)6-tap的FIR濾波器的數(shù)據(jù)訪問(wèn)模式。如計(jì)算輸出y[0],從輸入緩沖區(qū)x[]讀取6個(gè)采樣點(diǎn),當(dāng)?shù)谝粋€(gè)訪問(wèn)發(fā)生時(shí),cache控制器讀取x[0]以及后續(xù)地址的若干個(gè)數(shù)據(jù)(取決于cache line的長(zhǎng)度),從速度慢的存儲(chǔ)器加載一個(gè)cache line的數(shù)據(jù)需要一定的時(shí)鐘周期的CPU stall。這種加載的一個(gè)動(dòng)機(jī)是x[0]后續(xù)的數(shù)據(jù)后面就要被訪問(wèn)到。這個(gè)對(duì)于FIR濾波器是顯然的,因?yàn)楹竺娴?個(gè)采樣點(diǎn)(x[1]-x[5])就要被用到。后面的這5次存儲(chǔ)訪問(wèn)就只需要訪問(wèn)高速cache就可以了。

當(dāng)計(jì)算下一個(gè)輸出y[1]時(shí),5個(gè)采樣點(diǎn)(x[1]-x[5])就可以重用了,只有一個(gè)采樣點(diǎn)(x[6])需要重新加載。所有的采樣點(diǎn)都在cache內(nèi)了,訪問(wèn)時(shí)不會(huì)有CPU stall了,這也就是剛才提到的時(shí)間關(guān)聯(lián)性,即上一步利用的數(shù)據(jù)在下一次處理中還是可能會(huì)被用到的。

Cache就是利用數(shù)據(jù)訪問(wèn)的時(shí)間和空間關(guān)聯(lián)性建立的,它讓對(duì)速度較慢的外存的訪問(wèn)次數(shù)盡可能的降低,而讓大部分的數(shù)據(jù)訪問(wèn)都由更高層次的cache存儲(chǔ)區(qū)來(lái)完成。

存儲(chǔ)區(qū)的速度

Cache系統(tǒng)通常包含以下3級(jí):

?第一級(jí)(L1)在CPU片內(nèi),運(yùn)行在CPU時(shí)鐘頻率;

?第二級(jí)(L2)也在片內(nèi),但是比L1稍慢,容量較L1大;

?第三級(jí) (L3)是外存,最慢容量也最大。

每一層次的cache有不同的數(shù)據(jù)訪問(wèn)性能,相對(duì)的性能比較可以參考下面的表格。

當(dāng)處理器從存儲(chǔ)區(qū)請(qǐng)求數(shù)據(jù)訪問(wèn)時(shí),首先在最高層次的cache內(nèi)查找,然后再?gòu)拇胃呒?jí)別的存儲(chǔ)區(qū)查找。當(dāng)請(qǐng)求在cache內(nèi)時(shí)就是cache命中,否則是一次cache miss。因而Cache系統(tǒng)的性能將取決于cache命中的比率。對(duì)于任意級(jí)別的cache,命中率越高性能越好。比如一個(gè)內(nèi)存訪問(wèn)的L1 cache命中率為70%,L2 20%, 其他來(lái)自L3,那么以圖3所示的性能下,平均一次內(nèi)存的訪問(wèn)時(shí)間為

(0.7 * 4) + (0.2 * 5) + (0.05 * 30) + (0.05 * 220) = 16.30 ns 考慮圖4所示的TI TMS320C64x DSP的存儲(chǔ)架構(gòu),兩級(jí)的片內(nèi)cache加上片外外存。一級(jí)Cache分成程序(L1P)和數(shù)據(jù)(L1D) cache,每個(gè)容量為16 Kbytes。L1緩存數(shù)據(jù)訪問(wèn)不會(huì)有存儲(chǔ)stall。L2存儲(chǔ)區(qū)分成L2 SRAM和L2 cache,無(wú)論是哪種配置,L2存儲(chǔ)區(qū)都需要兩個(gè)CPU周期完成一次數(shù)據(jù)訪問(wèn)。不同的DSP,L2的容量不同,如TMS320C6454 DSP,L2的大小為1Mbytes。最后是C64x DSP最大高達(dá)2GBytes的外存,外存的訪問(wèn)速度取決于使用的存儲(chǔ)器類型,但一般外存的頻率在100 MHz左右。圖4中的所有的cache(紅色)和數(shù)據(jù)通路都由cache控制器自動(dòng)維護(hù)。

Cache的更新

Cache一直是主存的一個(gè)拷貝,因而需要cache能隨時(shí)反映主存的內(nèi)容。如果數(shù)據(jù)在cache內(nèi)被更新,而主存里沒(méi)有更新,這個(gè)cache內(nèi)的數(shù)據(jù)就被稱為污染(dirty)數(shù)據(jù),而數(shù)據(jù)在主存被更新但是cache內(nèi)沒(méi)有更新,這時(shí)cache內(nèi)的數(shù)據(jù)被稱為過(guò)時(shí)的(stale)數(shù)據(jù)。

Cache控制器使用一系列的技術(shù)來(lái)維護(hù)cache的一致性。偵聽(tīng)“Snoop”和強(qiáng)制更新“snarf” 是兩種常用的技術(shù)。偵聽(tīng)是讓cache決定主存內(nèi)的數(shù)據(jù)的處理影響到被cache的地址的數(shù)據(jù)。強(qiáng)制更新是把數(shù)據(jù)從主存拷貝到cache存儲(chǔ)器。

Cache通常比主存容量小得多,因而cache最終總會(huì)被填滿,這時(shí)新進(jìn)入的數(shù)據(jù)總要代替那些已經(jīng)在cache內(nèi)的數(shù)據(jù)了。有很多種策略決定那些已經(jīng)在cache內(nèi)的數(shù)據(jù)被代替更新如隨機(jī)代替,先進(jìn)先出(FIFO)以及最遲不用的策略(LRU),大部分的處理器都采用LRU,即把least-recently-used數(shù)據(jù)替換為最新的數(shù)據(jù)。這種策略由于考慮到數(shù)據(jù)訪問(wèn)的是時(shí)間相關(guān)性而非常有效。

直接映射的cache

Caches要么是直接映射的“direct-mapped”,要不就是組相關(guān)的“set-associative”。圖5是C64x的L1P cache,包含了512個(gè)32字節(jié)的cache lines。每個(gè)外存地址總是映射到同一個(gè)cache line,如:

?地址0000h 到 001Fh總是映射到cache line 0

?地址0020h 到 003Fh總是映射到cache line 1

?地址3FE0h 到 3FFFh總是映射到cache line 511.

當(dāng)開(kāi)始訪問(wèn)地址4000h,cache容量被完全占用,因而地址4000h 到 401fh又映射到cache line 0.

為了保存從外存拷貝的數(shù)據(jù)信息,每個(gè)L1P的cache行包含如下信息:

?有效位,表明當(dāng)前cacheline是否包含有效數(shù)據(jù);

?標(biāo)簽區(qū)域,對(duì)應(yīng)于外存地址的高18位,由于每個(gè)cache行的數(shù)據(jù)可以由外存若干地址拷貝而來(lái),如line 0保存可以來(lái)自地址0000h 到 001fh的數(shù)據(jù)也可以來(lái)自地址4000h 到 401fh。

?組號(hào),對(duì)應(yīng)于地址的5到13 bit;對(duì)于直接映射的cache而言,組號(hào)對(duì)應(yīng)于cache line號(hào)。這個(gè)組號(hào)對(duì)于組相關(guān)的cache是非常復(fù)雜的。

當(dāng)CPU開(kāi)始訪問(wèn)地址0020h時(shí),假設(shè)cache已經(jīng)被完全被設(shè)定無(wú)效了(invalidated),即沒(méi)有cache line包含有效數(shù)據(jù)。此時(shí)cache控制器開(kāi)始根據(jù)當(dāng)前地址的組(即地址的第5到13比特)來(lái)看對(duì)應(yīng)的哪個(gè)cache line。對(duì)于地址0020h來(lái)說(shuō)是cache line 1.然后cache控制器檢查line 1的標(biāo)簽位,確認(rèn)其是否對(duì)應(yīng)于地址0020h到0039h,最后檢查有效位,發(fā)現(xiàn)其值為0,即該地址的數(shù)據(jù)并不在cache內(nèi),此時(shí)cache控制器標(biāo)記一次cache miss。這次的miss讓控制器從外存加載整個(gè)cacheline(0020h-0039h),同時(shí)更新標(biāo)簽tag位,并把有效位設(shè)置為1,同時(shí)加載的數(shù)據(jù)傳遞給CPU,此次數(shù)據(jù)訪問(wèn)結(jié)束。

當(dāng)還需要繼續(xù)訪問(wèn)地址0020h時(shí),cache控制器會(huì)繼續(xù)檢查組號(hào)和標(biāo)簽域,并和存在標(biāo)簽RAM的值比較,同時(shí)有效位的值為1,意味著此次是一個(gè)cache hit。

結(jié)語(yǔ)

關(guān)于tms320c6748的相關(guān)介紹就到這了,如有不足之處歡迎指正。

-

Cache

+關(guān)注

關(guān)注

0文章

129瀏覽量

28298 -

TMS320C6748

+關(guān)注

關(guān)注

3文章

42瀏覽量

13093

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TMS320C6748/C6748 DSP開(kāi)發(fā)板——廣州創(chuàng)龍

【TL6748 DSP申請(qǐng)】基于TMS320C6748的視頻監(jiān)控系統(tǒng)

求TMS320C6748相關(guān)資料

TMS320C6748 Fixed/Floating-Poi

基于StarterWare的TMS320C6748裸機(jī)程序開(kāi)發(fā)入門詳解教程

TMS320C6748固定和浮點(diǎn)DSP硅修訂2.3_2.1_2.0_1.1_1.0_英版

TMS320C6748 TMS320C6748 Fixed/Floating Point DSP

tms320c6748主要參數(shù)和原理圖 tms320c6748 IO圖淺析

TMS320C6748和TMS320C6747芯片對(duì)比

TMS320C6748 OMAPL138核心板連接器引腳分布圖免費(fèi)下載

德州儀器DSP的TMS320C6748技術(shù)手冊(cè)

TMS320C6748定點(diǎn)和浮點(diǎn)DSP數(shù)據(jù)表

使用TPS650061為TMS320C6742、TMS320C6746和TMS320C6748供電

TMS320C6748/46/42配套產(chǎn)品

淺談tms320c6748最小系統(tǒng)設(shè)計(jì)和cache配置

淺談tms320c6748最小系統(tǒng)設(shè)計(jì)和cache配置

評(píng)論