“XX工,麻煩你把這組數據線的間距調大一些,我擔心串擾會比較大”

“間距我已經按照3H處理了而且布線空間也沒辦法調整了”

“這個DDR4是要跑2400M的,麻煩您調整一個合適的間距,盡量不要出問題”

但是怎樣才是合適的符合設計要求的間距,在layout工程師眼里一直都是一個玄學的命題,只能放飛想象的翅膀,而不是一個可以用數字量化的結果。就好像串擾,也是一個抽象的世界,所以每每遇到這種問題,大家就只能佛系一點啦。

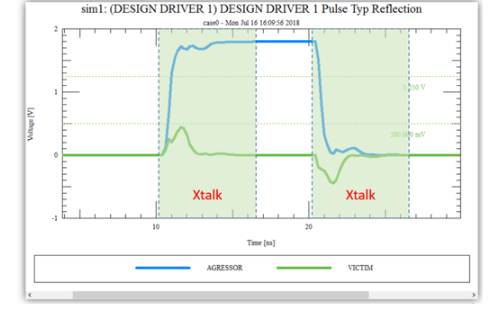

對于串擾,我們可能了解是怎么產生的,以及變化的趨勢,但實際上,在遇到間距太近沒有空間調整,或者雙帶線層疊的時候,我們能做的就是盡量拉開間距,卻沒有太直觀的辦法評估多大的間距會是比較符合要求的。在沒有測試參數,沒有仿真結果的情況下,是不是只能靠拍腦袋了呢?此時,Allegro17.2中的功能——線間耦合串擾分析“duang”就適時出場。這個功能可以幫layout工程師去衡量間距和串擾之間的平衡(編者注:即評估間距對串擾的影響),用具體的參數告訴大家,怎樣的間距才是符合設計要求的。還是一樣用一個例子來說明新功能的實用性。

如下圖所示DDR3信號,工作頻率為1600Mbps,按照客戶要求設置了比較嚴格的等長要求±5mil,由于空間的影響,部分地方間距壓縮到5mil才能完成時序等長,這個間距和我們平時的設計規范是違背的(編者注:即平時的設計規范是超要求的),這種時候就需要準確的數據,用嚴謹的態度去說服客戶修改等長要求,下面我們用線間耦合串擾分析去看一下5mil的間距對于信號的影響大不大。

首先選擇Coupling Workflow,開始設置其他參數。選擇需要分析的網絡,設置耦合閾值為2%,意味著耦合率為2%以下時忽略不計。一般的遵循的規則是耦合率應該為5%以下,當耦合率高于5%以上時,信號間距就需要調整了。設置比較簡單,傻瓜式操作,對于英語渣的我而言,可以說是非常的人性化了。選擇start analysis。

結果也是通過兩種方式顯示:coupling Vision,比較直觀的一種方式,把鼠標放置在相應的線段上時,也會顯示相應的耦合系數。

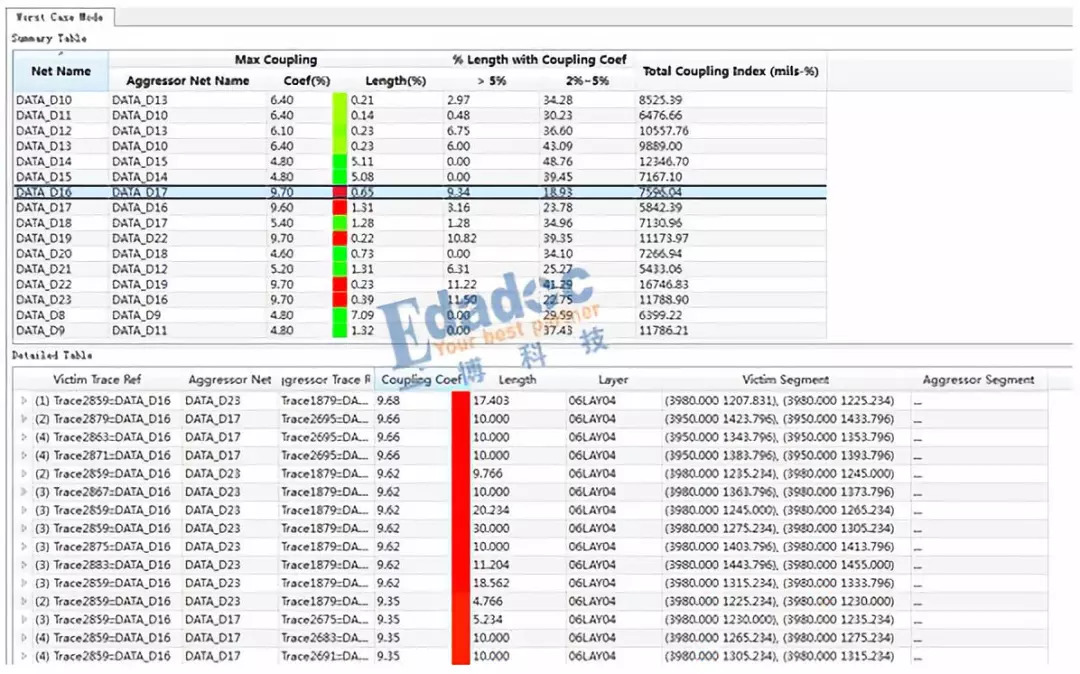

另一種結果顯示方式是coupling table,數據比較清晰具體,主要關注的是最大耦合系數以及耦合系數大于5%的部分線長比例。

從上面的結果可以看到,部分網絡的耦合系數達到9.7%,串擾太大,對信號質量可能影響會比較大。但這些地方都比較短,比較容易調整,所以可以選擇適當放寬等長規則到±25mil,把間距拉開到9mil,這是可以滿足時序,調整也比較小的一種方式,結果如下圖,耦合系數均在5%以下。

這種數據讓我們在設計的時候,能夠清楚的了解到自己板子的實際情況,不需要靠想象去完成板子的修改,也有直觀的數據指導修改,修改點清晰明了,對于提升設計效率以及設計的準確性是有很大幫助的。

-

DDR3

+關注

關注

2文章

274瀏覽量

42180 -

PCB設計

+關注

關注

394文章

4670瀏覽量

85289 -

allegro

+關注

關注

42文章

650瀏覽量

144968 -

串擾

+關注

關注

4文章

189瀏覽量

26932 -

可制造性設計

+關注

關注

10文章

2065瀏覽量

15470 -

華秋DFM

+關注

關注

20文章

3493瀏覽量

4376

原文標題:怎樣才是符合設計要求的線間距?——Allegro17.2新功能

文章出處:【微信號:CadencePCB,微信公眾號:CadencePCB和封裝設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高速差分過孔之間的串擾分析

信號串擾消除方案之PCB設計IDA Crosstalk分析功能

如何設計符合要求的間距?避免串擾Allegro17.2新功能實例分析

如何設計符合要求的間距?避免串擾Allegro17.2新功能實例分析

評論