集微網(wǎng)消息,9月19日,2018年中國閃存市場峰會(CFMS2018)在深圳舉行,長江存儲總經(jīng)理?xiàng)钍繉幉┦恳浴皠?chuàng)新Xtacking?架構(gòu):釋放3D NAND潛能”為主題,介紹長江存儲Xtacking?架構(gòu)的技術(shù)優(yōu)勢和長江存儲3D NAND新進(jìn)展。

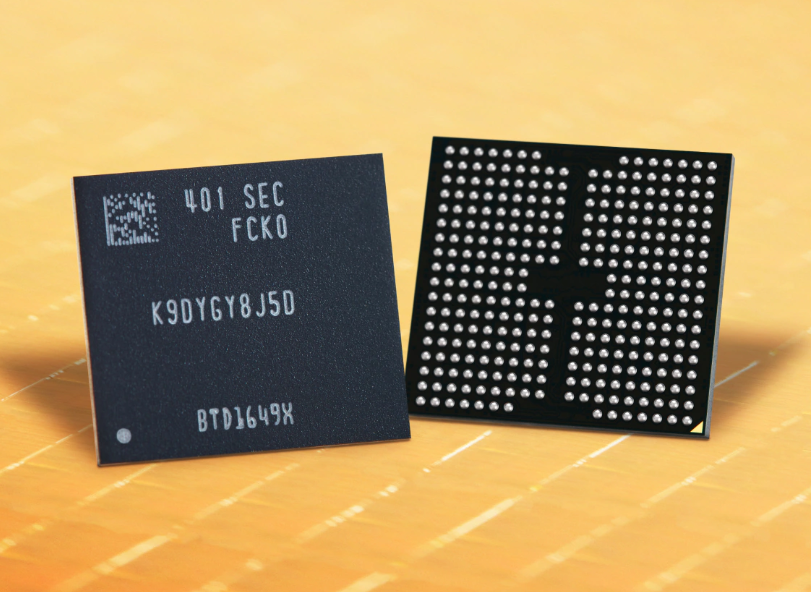

如今我們終端設(shè)備需要存儲的數(shù)據(jù)越來越多,隨著人工智能的應(yīng)用,要求分析數(shù)據(jù)的速率也越來越快。楊士寧表示,閃存市場增長的很快,64層3D NAND已經(jīng)量產(chǎn),這相當(dāng)于最新的蘋果 A12芯片7nm工藝技術(shù);實(shí)際上,NAND也是根據(jù)摩爾定律往前推進(jìn),我們終端設(shè)備需要的數(shù)據(jù)越來越多,分析的速率也越來越快,技術(shù)也需要不斷突破。

“雖然長江存儲是個新公司,但我們也希望創(chuàng)新,來為這個產(chǎn)業(yè)做貢獻(xiàn)。”楊士寧表示,長江存儲創(chuàng)新的Xtacking?架構(gòu)技術(shù)將為3D NAND閃存帶來更高的I/O性能,更高的存儲密度,以及更短的產(chǎn)品上市周期。

“Xtacking?架構(gòu)在業(yè)界算是比較新的技術(shù),且在可靠性、穩(wěn)定性等測試上都很好;不過,現(xiàn)在我們3D NAND還沒有批量出貨,等大批量出貨之后,才能算是成功,我們預(yù)計(jì)能在2019年批量出貨。” 楊士寧說到。

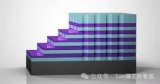

Xtacking?一個新的架構(gòu),通過Xtacking?,周邊控制電路設(shè)計(jì)可以隨意選擇邏輯電路的先進(jìn)工藝。采用Xtacking?,可在一片晶圓上獨(dú)立加工負(fù)責(zé)數(shù)據(jù)輸入輸出及記憶單元操作的外圍電路。這樣的邏輯電路加工工藝,可以讓NAND獲取所期望的高I/O接口速度和功能。

在傳統(tǒng)3D NAND架構(gòu)中,外圍電路約占芯片面積的20~30%,降低了芯片的存儲密度。隨著3D NAND技術(shù)堆疊到128層甚至更高,外圍電路可能會占到芯片整體面積的50%以上。通過Xtacking?技術(shù)將外圍電路置于存儲單元之上,從而實(shí)現(xiàn)比傳統(tǒng)3D NAND更高的存儲密度。

“在研發(fā)周期上,采用Xtacking?架構(gòu)架構(gòu),3D NAND產(chǎn)品研發(fā)周期至少減短三個月,生產(chǎn)周期可縮短20%,從而大幅縮短3D NAND產(chǎn)品的上市時(shí)間。”據(jù)悉,通過Xtacking?架構(gòu)技術(shù)可充分利用存儲單元和外圍電路的獨(dú)立加工優(yōu)勢,實(shí)現(xiàn)了并行的、模塊化的產(chǎn)品設(shè)計(jì)及制造,可縮短3D NAND產(chǎn)品開發(fā)時(shí)間。

雖然長江存儲成立才僅僅2年多時(shí)間,但在IC制造方面已經(jīng)有10多年的經(jīng)驗(yàn)積累。長江存儲NAND產(chǎn)品是在武漢新芯的基礎(chǔ)上發(fā)展起來的,而武漢新芯是12年前成立的,一開始跟中芯國際有過合作。

楊士寧表示,我們最早是從9層堆棧的NAND芯片驗(yàn)證開始做,現(xiàn)在我們64層堆棧的3D NAND芯片驗(yàn)證剛剛?cè)〉贸晒ΑT谖磥淼陌l(fā)展中,長江存儲將主要注重大規(guī)模存儲器研發(fā)設(shè)計(jì)和制造,我們第一代NAND產(chǎn)品已經(jīng)量產(chǎn)上市,客戶的反饋還是非常正面的,我們希望第二代3D NAND產(chǎn)品將于明年量產(chǎn)上市后,開始賺錢。

本文來源:集微網(wǎng)

-

3D

+關(guān)注

關(guān)注

9文章

2864瀏覽量

107341 -

長江存儲

+關(guān)注

關(guān)注

5文章

323瀏覽量

37839

發(fā)布評論請先 登錄

相關(guān)推薦

預(yù)期提前,鎧俠再次加速,3D NAND準(zhǔn)備沖擊1000層

美光第九代3D TLC NAND閃存技術(shù)的SSD產(chǎn)品開始出貨

三星HBM3E批量出貨在即,DDR5市場或迎供應(yīng)緊張與價(jià)格上漲

紫光展銳助力全球首款A(yù)I裸眼3D手機(jī)發(fā)布

三星已成功開發(fā)16層3D DRAM芯片

3D NAND閃存來到290層,400層+不遠(yuǎn)了

三星量產(chǎn)第九代V-NAND閃存芯片,突破最高堆疊層數(shù)紀(jì)錄

三星即將量產(chǎn)290層V-NAND閃存

鎧俠計(jì)劃2030-2031年推出千層級3D NAND閃存,并開發(fā)存儲級內(nèi)存(SCM)

三星將推出GDDR7產(chǎn)品及280層堆疊的3D QLC NAND技術(shù)

ad中3d封裝放到哪個層

3D視覺的三大優(yōu)勢

提高3D NAND閃存存儲密度的四項(xiàng)基本技術(shù)

Xtacking? 架構(gòu)取得三大技術(shù)突破,64層3D NAND預(yù)計(jì)明年批量出貨

Xtacking? 架構(gòu)取得三大技術(shù)突破,64層3D NAND預(yù)計(jì)明年批量出貨

評論