SGMII接口(開啟自協商)調試分為三個步驟,先測試SGMII最基本功能仿真、再測試SGMII最基本功能自回環上板、最后直接測試開啟自協商功能后上板

1、測試SGMII基本功能仿真:

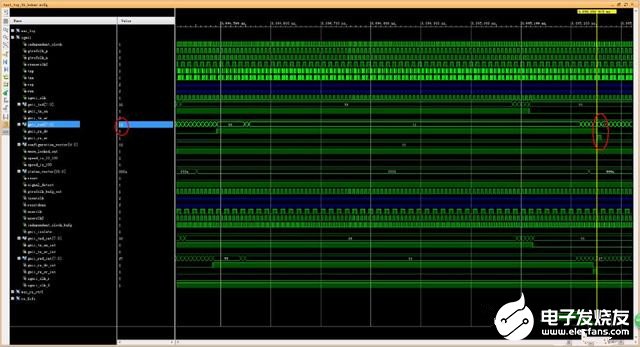

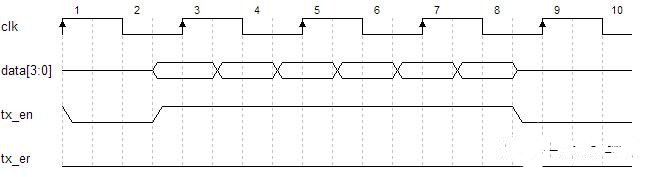

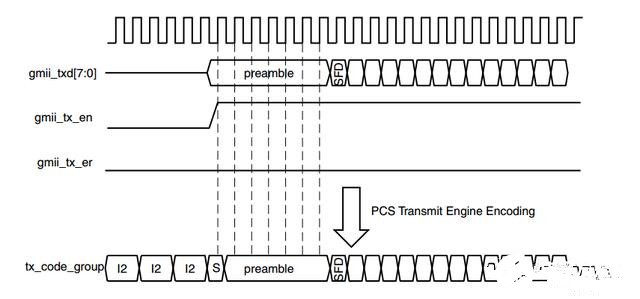

(1) 打開sgmii IP,將接口選擇為sgmii接口,關閉MDIO接口,其它選項默認,生成IP核;(2) 根據IP核生成example design,將speed_is_10_100、speed_is_100設置為0(1000Mbps模式),將configuration_vector設置為5‘b00010(關閉SGMII自協商,開啟PMA回環,具體參考手冊63頁table2-39),將userclk2作為跟GMII接口同步的時鐘(用來驅動MAC GMII接口側,也可以用來驅動其它模塊);(3) 開啟仿真,測試自回環(也可以通過修改參數測試外環或2個SGMII互通),一般PMA回環要3.1ms左右才能通,外環或互通要3.5ms左右;(4) 仿真時會發現gmii_rxd信號每隔一幀數據會少一個時鐘的前導碼如圖1,這個不用擔心,為正常現象,1G MAC仍然能正常接收數據,產生這個的具體原因不詳(手冊有介紹,不過內容偏向于底層編碼原因,具體不太了解,手冊只是簡單說明了一下表面原因,手冊221頁說明此問題),同時有的數據幀gmii_rx_dv信號拉低后gmii_rx_er信號會拉高一個時鐘(對應的gmii_rxd數據為8‘h0f),如圖2,這個也不用擔心,手冊224頁對其有說明(具體說是為幀擴展),由于gmii_rx_er拉高處gmii_rx_dv拉低,所以不是幀錯誤(此處需要適當修改原版1G MAC的代碼,使1G MAC中gmii_rxd、gmii_rx_dv、gmii_rx_er同步打拍,原設計中沒有同步打拍)。

圖1

圖2

注意:SGMII開啟自協商后要仿真非常長時間才能互通(8.1ms),因此推薦直接上板。

1、測試SGMII基本功能上板:

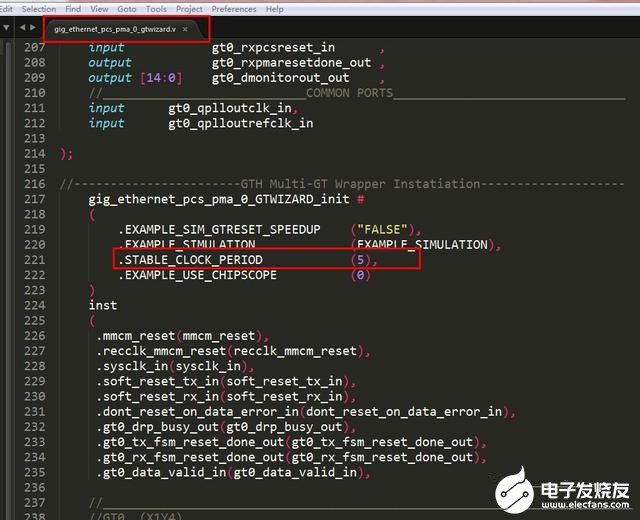

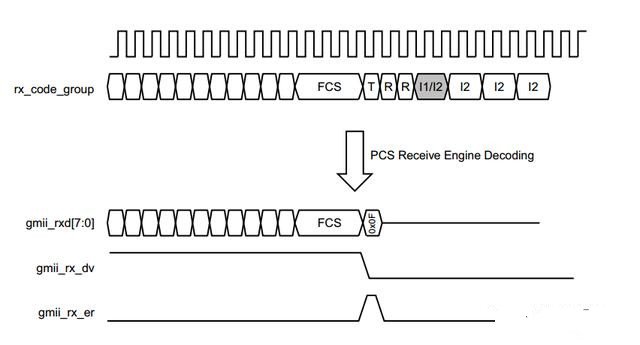

(1)SGMII接口的independent_clock默認是200MHZ,可以用PLL生成,也可以查閱手冊修改IP內部參數來設置為其它頻率,具體修改參考手冊36頁描述(修改后如何操作IP參考RapidIO調試手冊),只需修改一個參數就可以(修改時鐘頻率會影響仿真通過時間),如圖3;(2)上板主要是測試PMA回環版(自帶激勵源),設置好約束文件,抓取關鍵信號,直接生成bit文件,上板測試,如果沒有通,看status_vector信號,查閱手冊65頁table2-41,查找原因。

圖3

3、測試SGMII自協商功能上板:

(1)將configuration_vector參數設置為5‘b100x0(開啟自協商功能,x表示可以測PMA回環,也可指直接接PHY進行測試),自協商參數使能信號an_restart_config設置為0(該信號上升沿代表自協商參數an_adv_config_vector有效,an_restart_config為0表示使用默認參數,如果想手動配置自協商參數,可以查閱手冊64頁table2-40);(2)生成bit文件并上板測試,并觀察狀態信號status_vector。

RGMII或SGMII調試中正常的“異常”問題

1、參考資料

《pg047-gig-eth-pcs-pma》

《88e1512 data》

《AR8033d》

2、以太網接口使用場景介紹

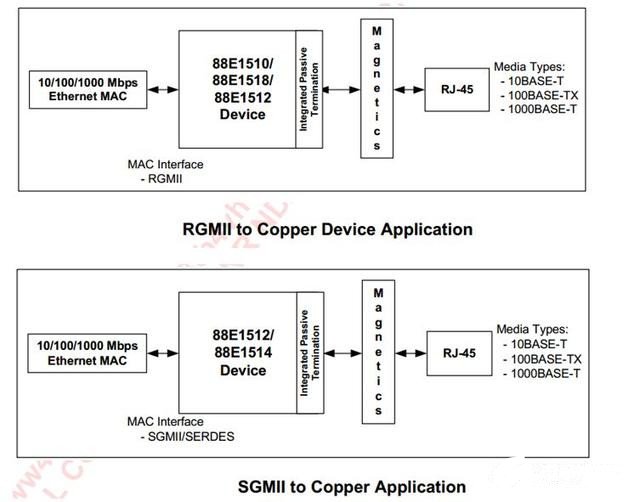

《88e1512data》PHY芯片手冊中,標準的RGMII、SGMII接口的使用場景如下兩圖所示:

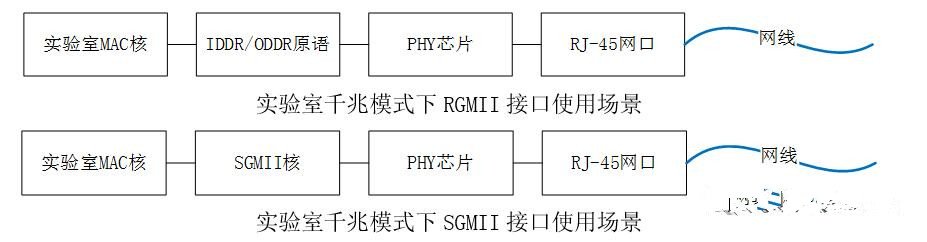

實際上,此處的10/100/1000Mbps Ethernet MAC代指的是標準的SGMII接口的MAC核和標準的RGMII接口的MAC核。而實驗室所用的MAC核為GMII接口形式的MAC核,因此實際上我們的應用場景變成了如下的兩圖:

此處的IDDR/ODDR原語、SGMII核主要功能是為實驗室MAC核提供標準的千兆GMII接口形式的數據源。在實驗的接口調試中,由于PHY芯片的各個功能模式設置、XILINX官方的SGMII核和IDDR/ODDR原語的特性不同,可能會出現一些問題。

3、PHY芯片功能模式設置

正常情況下,我們常用的PHY芯片功能模式有以下:

全雙工/半雙工模式

千兆/百兆/十兆模式

自協商速率/固定速率

RGMII/SGMII模式

交叉線/直連線模式

當交換機出現無法連接網口(連接指示燈熄滅)、數據收發錯誤等問題時,可以通過VIO、MDIO來讀取PHY芯片相應功能的寄存器的值,來確定功能模式配置是否出現問題。

4、RGMII千兆模式常見問題

此問題詳細描述見本公眾號之前文章:

RGMII接口調試使用VIO讀取PHY寄存器值

標準的RGMII千兆接口,時鐘周期為125MHz,但是數據位寬為4位,采用在時鐘的上下邊沿采樣的方式,得到1Gbps帶寬,正常工作狀態的發送時序圖如下所示:

為了確保數據采樣的正確,時鐘的邊沿必須在數據的中間進行跳變。為了實現這種發送模式,在數據發送時,控制發送時鐘,使其偏移90度(即延后2ns)。

但是有的PHY芯片中,可以選擇不同的工作模式,使得控制時鐘偏移2ns或者不偏移2ns(《88e1512》P252)。如果PHY芯片的工作模式是偏移了2ns,那我們就不用作偏移了,否則可能正好導致時鐘邊沿和數據跳邊沿對齊,出現錯誤;如果PHY芯片的工作模式是不偏移,則我們需要手動控制時鐘的偏移。RGMII數據的讀取同理,具體情況需要閱讀相應的PHY芯片手冊。

5、SGMII千兆模式下常見的“異常”問題

參見《pg047-gig-eth-pcs-pma》P219,Xilinx官方的SGMII的IP核轉換出的GMII格式數據可能會出現兩種問題:

以太網數據幀幀頭部分丟失一個前導碼;

以太網數據幀FCS域結束后,tx_er信號拉高。

丟失前導碼情況,如下圖所示:

在這種情況下,前導碼由7個55,1個D5,變成了6個55,1個D5。某些MAC核是根據55跳變到D5這種情況下作操作的,所以數據直接進MAC核,不會出現問題。但是,在TTE交換機中,分流模塊、TT平面,可能是根據gmii_tx_en信號的上升沿開始作計數,從而提出TT_ID、TYPE/LENGTH域等數據,這就可能導致錯誤。并且,以太網幀發送時,需要發送7個55,1個D5格式的前導碼。因此,我們接收到這種數據幀時,需要將前導碼補齊,再將數據幀送入后續模塊進行處理。

FCS域結束后,tx_er信號拉高,如下圖所示:

由于可能的設計缺陷,某些MAC核,會將這種數據幀當作錯誤幀丟棄。解決辦法是,在數據幀的接收部分,對tx_er信號進行處理,當rx_dv信號為高時,tx_er仍然保持原值,當rx_dv信號為低時,tx_er信號直接置零。

責任編輯:gt

-

測試

+關注

關注

8文章

5174瀏覽量

126488 -

仿真

+關注

關注

50文章

4048瀏覽量

133431 -

pll

+關注

關注

6文章

775瀏覽量

135054

發布評論請先 登錄

相關推薦

SGMII接口基本功能仿真測試及常見異常問題的解決方法

SGMII接口基本功能仿真測試及常見異常問題的解決方法

評論