1、引 言

隨著列車全面提速以及鐵路部門客貨運輸量不斷增大,鐵路線路負荷不斷加重,鐵路安全問題日益突出。目前鐵道檢測部門主要采用鐵軌檢查車檢測鐵軌質量,但是由于鐵軌檢查車價格昂貴,各機務段配備的數量有限,不能滿足鐵路檢測部門對鐵軌質量數據連續檢測和積累的要求。因此鐵道檢測部門迫切需要一種可靠性高,實時性強的小型智能系統作為鐵軌檢查車的補充。針對這種情況,本文設計了一種新型鐵路線路質量遠程實時監測系統。本系統綜合利用移動通信和嵌入式系統設計等技術,實現了鐵軌數據的實時采集、分析、傳輸,以及自動評估和報警。

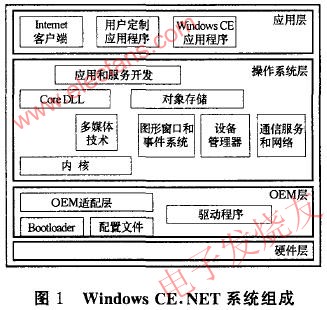

ARM技術是嵌入式系統方面的主流技術。目前市場上ARM芯片速度可達幾百兆,以此為主控芯片可在硬件上實現高速、高精度且具有一定處理能力的數據采集處理通信系統。本系統采用的Samsung公司的S3C2410處理器,結合Windows CE操作系統來實現其功能。S3C2410處理器是一款低價、低功耗、高性能的16/32位系統微處理器,在嵌入式應用領域有著良好的表現。S3C2410具有豐富的接口資源,能夠滿足本系統的設計需求。Windows CE操作系統是專門為掌上型電腦設計的電腦環境,它將便攜式技術和現有的Windows技術相結合,并提供了豐富的驅動資源。本系統在設計中采用了CMDA模塊和USB接口。原始數據可通過USB接口取出,進一步進行事后處理。本系統通過CDMA模塊連接無線網絡,將處理完畢的數據實時地送到客戶端,以實現特定信息查詢和告警功能。

2、系統工作原理

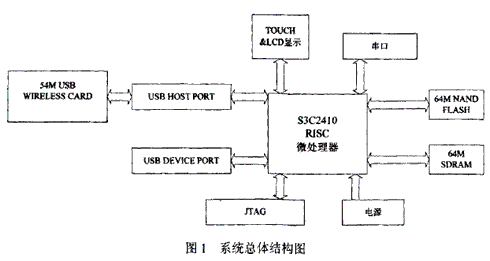

系統分為ARM處理器模塊、協處理器FPGA模塊、A/D模塊、傳感器模塊和外部通信模塊5部分,基本結構如圖1所示。ARM處理器和現場可編程門陣列(FPGA)共同組成監控系統的核心處理單元。傳感器模塊采集的模擬信號經A/D模塊量化后,存入FPGA生成的FIFO中;ARM處理器通過FPGA產生的中斷信號來讀取FIFO中的數據;數據處理完畢后ARM處理器通過FGPA控制CDMA模塊建立TCP/IP連接,連接一旦建立則通過無線網絡將數據傳回客戶端。

2.1 協處理器FPGA模塊

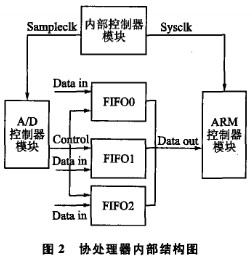

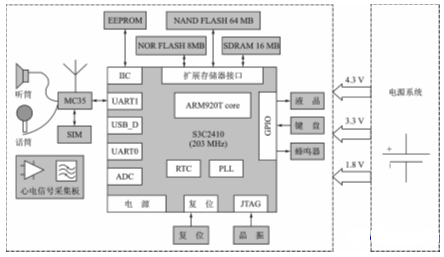

本系統的協處理器采用Xilinx公司的FPGA,型號為SPARTANIIE XC2S100E。該芯片共有2700個邏輯單元,10萬個邏輯門,片內塊RAM為40 KB。協處理器內部結構見圖2。其具體實現以下功能:

A/D模塊讀/寫時序控制;

生成3個FIFO,其主要功能是存儲經A/D編碼的數據;

提供ARM處理器控制信號。

FPGA芯片分4部分來實現上述功能:

(1) 內部控制信號產生器

FPGA對50 MHz時鐘分頻產生A/D芯片采樣時鐘Sampleclk和ARM處理器外部時鐘Sysclk;Sysclk經鎖相環電路(PLL)后產生ARM處理器工作所需的時鐘信號。

(2) ARM控制器

提供ARM處理器正常工作所必須的各種控制信號;實現ARM處理器地址總線、數據總線和外部中斷信號接入。

(3) A/D控制器

控制A/D模塊的數據轉換。產生A/D轉換起始信號(/HOLD),檢測數據轉換完成信號(/EOC),產生FIFO寫入信號,實現數據轉換通道選擇。

(4) FIFO存儲器

生成3個16位、數據深度為511的FIFO,完成A/D轉換數據的存儲。

2.2 ARM處理器模塊

ARM處理器模塊由FLASH、SDRAM和S3C2410共同構建。本系統選配用Samsung公司的K9F1208U0A構建8位FLASH存儲器系統。K9F1208U0A單片容量為64 MB;選用兩片單片容量為32 MB,數據寬度為16位的HY57V561620CT,并聯構建32位SDRAM存儲器系統,共64 MB的SDRAM空間可以滿足嵌入式操作系統和各種復雜算法的運行要求。ARM處理器對各模塊的控制則是通過底層驅動控制協處理器FPGA產生各種控制信號來實現。

2.3 A/D模塊

A/D轉換芯片采用TI公司的ADS8364芯片,它具有以下性能:

6個獨立數據輸出通道;

模擬信號差分輸入;

6個獨立的16位ADC;

采樣頻率最高為250 MHz;

采樣精度到最后兩位,且抗噪性能好。

通過FPGA內產生的采樣時鐘信號控制A/D模塊的采樣頻率。FPGA輸出寬度為一個時鐘周期的低電平脈沖到/HOLD_X引腳,A/D轉換開始,經16.5個時鐘周期后A/D轉換完成。A/D模塊根據FPGA內產生的讀信號和通道選擇信號選擇相應的FIFO存儲數據。

2.4 傳感器模塊

傳感器模塊可以根據所須采集的數據來選擇。本系統主要運用于火車機車車體震動測量,所以采用3個使用ADXL105高精度單軸加速度傳感器芯片制作的加速度測量模塊。測量模塊分別安置于車體底部的垂直方向和水平方向,用于測量車體在X、Y、Z方向上的加速度。測量數據以差分信號的形式輸入到精密放大器中,經比較放大后直接送到A/D模塊中。

2.5 外部通信模塊

外部通信模塊由兩部分組成: 485通信模塊和CDMA模塊。

485通信接口采用的是MAXIM公司的MAX1490芯片。這是一款完全隔離的485數據接口芯片,單工工作方式,傳輸波特率最大可達2.5 Mbps。其輸出引腳直接與ARM處理器的串口2(UART2)相連;ARM處理器通過串口2讀取時間和坐標等相關數據的廣播信息。ARM處理器串口0(UART0)與AnyData DTGS800 CDMA模塊相連;監測數據經預處理后通過CDMA模塊發送到地面服務器。

3、軟件設計

軟件設計主要使用Embedded Visual C++語言和VHDL語言。VHDL語言用于編寫FPGA程序;ARM處理器的調試則使用C語言。

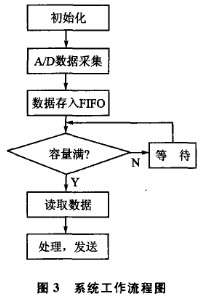

系統開始工作后ARM處理器和FPGA協處理器中的FIFO開始初始化。經A/D轉換后的數據存入3個數據輸出通道對應的FIFO中。FIFO中的數據容量達到一定限度即產生中斷,ARM處理器中的主程序產生中斷等待線程;一旦中斷產生則進入中斷服務程序,讀取數據。數據經檢測程序進行預處理后通過CDMA模塊發送出去。圖3為系統工作流程圖。

3.1 系統的同步處理

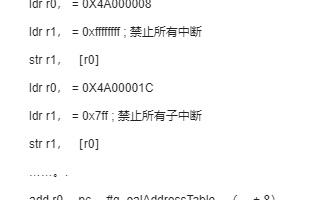

因為A/D模塊與FPGA協處理器上電即開始工作而ARM處理器完成系統加載,端口初始化大概需要10 s左右的時間。在這個過程中FIFO中存儲的數據已經被寫滿。如果ARM處理器在程序加載完成后直接使用這部分數據則會產生檢測結果與廣播信息不匹配的問題。為防止系統因各模塊工作時序混亂而出現的數據檢測錯誤的情況。在ARM完成Windows CE系統加載并進入檢測主程序后產生一個清零信號用于清除3個FIFO中的數據。實現系統的同步工作。

3.2 中斷的產生及處理

在本系統中如果對A/D轉換數據采用實時讀取的方式,則必然導致ARM處理器工作效率較低,所以在電路設計時采用了中斷方式。A/D模塊輸出數據以循環方式分別寫入3個FIFO中。一旦FIFO中可使用數據容量減小到一定限度則產生中斷,ARM處理器進入中斷服務程序并讀取FIFO中的數據。

3.3 列車廣播信息讀取

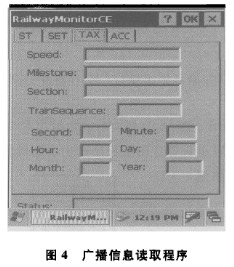

火車機車廣播信息通過監控設備不斷地發送廣播信息。信息傳輸以標準的RS485傳輸協議進行,通信波特率為9600 bps,采用10位異步通信方式:1位起始位+8位數據位+1位停止位。每組數據包由17字節數據組成,包括月日時分秒、時速、公里標、交路號和車次。數據格式為:起始位+數據位+停止位+BCC校驗。其中:起始位為1字節,固定為0x02;數據位為14字節;停止位為1字節,固定為0x03;BBC校驗為1字節,是前面15字節的“異或”校驗。

軟件實現:接收廣播信息程序的實現主要是利用了Windows的消息機制。首先初始化S3C2410芯片的UART2口,包括設置波特率為9600 bps,配置端口,并將端口與事件綁定。然后啟動線程不斷偵聽端口。如果有數據輸入則會產生讀取事件,此時線程讀取一個字節的數據,并由串口將數據發送至主線程。最后,主線程通過相應函數接收數據,數據接收完畢則對數據進行長度檢測和異或校驗。如果檢驗通過則將數據轉存入二級緩存(一級緩存繼續存放數據),并通知上級模塊讀出數據;然后清空二級緩存,等待下次數據進入。廣播信息讀取程序界面見圖4。

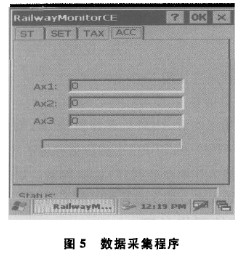

3.4 加速度數據獲取

數據采集是通過應用程序與驅動程序的交互來完成的。實現交互的方式有很多,例如可以利用callback函數(回調函數)或將函數應用程序中的數據處理函數指針傳給驅動,以及使用SETEVENT等來實現。考慮到軟件的升級,本系統采用的是SETEVENT方法。Windows CE系統與PC上的系統存在很大差異。一旦系統的某些模塊有所改動,必須重新編譯Windows CE系統和燒寫FLASH,工作量較大。使用SETEVENT的方法可在不改動驅動的情況下對應用程序進行調試,從而避免了反復燒寫FLASH。

軟件設計思路:數據采集軟件啟動后必須對FIFO中數據進行復位。因為從Windows CE系統啟動到數據采集軟件開始工作需要15 s,但 A/D模塊及FIFO模塊在系統上電后即開始工作,因此如果使用這部分數據就會造成數據與列車廣播信息的不匹配。驅動程序在響應中斷后通過SETEVENT機制通知應用程序,此時數據讀取控制權就完全交給了頂層用戶。用戶可以根據自己的需要來控制數據的讀取及處理。數據采集程序界面見圖5。

4 結束語

本文所研制的系統綜合利用了移動通信和嵌入式系統設計等技術,與傳統檢測設備相比,大大提高了線路監測的實時性及系統性。同時,該系統注重監測數據處理和檢測方法的研究,并在實際系統中加以應用。

本系統在設計時充分考慮了電路的靈活性和通用性,可根據不同的功能要求編寫相應的VHDL語言程序。系統所使用的Windows CE操作系統可以任意裁剪,這對于功能的轉換很有幫助。本系統已研制完畢,現處于現場實驗階段。

-

傳感器

+關注

關注

2548文章

50664瀏覽量

751941 -

處理器

+關注

關注

68文章

19159瀏覽量

229113 -

FPGA

+關注

關注

1626文章

21665瀏覽量

601805

發布評論請先 登錄

相關推薦

S3C2410處理器與Nand flash 的問題

基于ARM S3C2410處理器的PDA人機接口電路設計

S3C2410處理器 Bootloader(Vivi)源代碼

基于S3C2410的RTC模塊應用設計

Windows CE.NET在S3C2410處理器上的移植

基于S3C2410的土壤墑情監測系統設計[圖]

基于S3C2410處理器和IEEE802.11b實現無線溫度變送器的設計

基于S3C2410處理器對Windows CE 5.0操作系統實現BSP移植

基于Linux操作系統和S3C2410微處理器實現GPS實時導航系統的設計

基于在S3C2410處理器平臺上實現Windows CE.NET的應用設計

基于S3C2410處理器實現USB網卡無線網絡功能的實現

基于S3C2410處理器實現鐵路線路質量遠程實時監測系統的設計

基于S3C2410處理器實現鐵路線路質量遠程實時監測系統的設計

評論