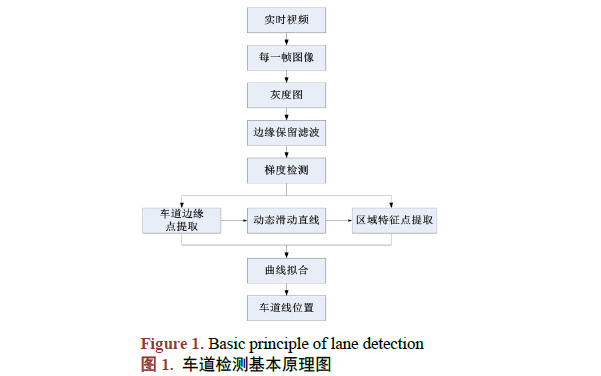

通過對攝像頭讀入的道路白線圖像進(jìn)行灰度變換,再檢測出白線的邊緣,這是實現(xiàn)智能車自動導(dǎo)航和輔助導(dǎo)航的基礎(chǔ)。行車道檢測系統(tǒng)可以應(yīng)用于智能車的防撞預(yù)警和控制。該系統(tǒng)設(shè)計重點(diǎn)是邊緣檢測電路的設(shè)計。邊緣檢測電路包括圖像輸入緩沖電路、垂直方向的邊緣檢測電路、水平方向的邊緣檢測電路及對兩部分檢測的組合,最終通過閾值選擇形成二值邊緣圖像。傳統(tǒng)的方案大多采用單片機(jī)電路實現(xiàn),設(shè)計流程和系統(tǒng)調(diào)試都比較繁瑣,開發(fā)周期長。在實時圖像處理中,由于處理速度要求較高,因此用以前的方法很難達(dá)到要求。實時圖像處理常常需要對圖像進(jìn)行求和、卷積、邊緣提取、圖像分割及特征提取等不同種類、不同層次的處理。對于一些運(yùn)算結(jié)構(gòu)簡單,但要處理大量數(shù)據(jù)的算法一般采用FPGA芯片來實現(xiàn)。通過FPGA實現(xiàn)信號處理可以取得出色的系統(tǒng)穩(wěn)定性,提高控制精度,還可以大大減少開發(fā)周期,使設(shè)計人員的設(shè)計自由度加大。本文采用Altera公司的Cyclone EP1C6作為主控芯片,利用Altera公司推出的數(shù)字信號處理開發(fā)工具DSP Builder作為設(shè)計平臺,通過DSP Builder SignalCompiler模塊讀取由DSP Builder和MegaCore模塊構(gòu)建的Simulink建模文件(.mdl),生成VHDL文件和工具命令語言(Tcl)腳本,進(jìn)行綜合、硬件實施和仿真,從而完成對整個道路邊緣檢測系統(tǒng)的設(shè)計。

1、系統(tǒng)構(gòu)成及邊緣檢測原理

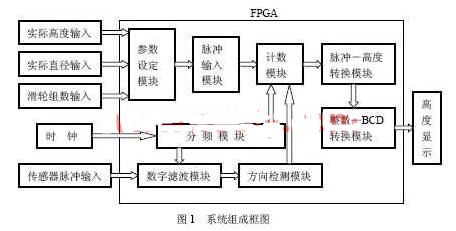

本系統(tǒng)中的主要模塊是進(jìn)行二維卷積操作的sobel邊緣檢測模塊,它相當(dāng)于硬件的協(xié)處理器。該系統(tǒng)從CF卡讀入數(shù)據(jù)到邊緣檢測模塊,使用Nios II控制數(shù)據(jù)流,采用DMA控制器在外部存儲器(SDRAM和SRAM)之間傳遞數(shù)據(jù),這些外部存儲器相當(dāng)于中間圖像數(shù)據(jù)緩沖器。系統(tǒng)結(jié)構(gòu)如圖1所示。

邊緣是指圖像中像素灰度有階躍變化或屋頂狀變化的那些像素的集合。它對圖像識別和分析十分有用,邊緣能勾劃出目標(biāo)物體輪廓,使觀察者一目了然。邊緣包含了豐富的信息(如方向、階躍性質(zhì) 、形狀等),是圖像識別中抽取的重要屬性。微分運(yùn)算有加強(qiáng)高頻分量的作用,從而使圖像輪廓更清晰。對于數(shù)字圖像,微分可用差分近似代替,沿x和y方向的一階差分可分別表示如下:

一階差分增強(qiáng)是有方向性的。為了增強(qiáng)圖像中間任何方向伸展的邊緣和輪廓,希望對圖像的某種導(dǎo)數(shù)運(yùn)算是各向同性的,而梯度運(yùn)算恰具有各向同性特性。對于圖像f(x,y)點(diǎn)上的梯度可定義為矢量:

梯度幅度具有各向同性或旋轉(zhuǎn)不變性,而且給出了該像素點(diǎn)灰度的最大變化率。采用微分銳化圖像,會使噪聲、條紋等得到增強(qiáng),這在圖像處理中會造成偽邊緣和偽輪廓,為此對銳化算子進(jìn)行了各種改進(jìn)。Sobel算子就是其中一例,它在一定程度上克服了上述問題。Sobel算子的基本思想是:以待增強(qiáng)圖像的任意像素(i,j)為中心,截取一個3×3的像素窗口。分別計算窗口中心像素在x和y方向上的梯度。Sobel算子的表達(dá)式如下:

Sx=

增強(qiáng)后圖像在(i,j)處的灰度值為:

2、基于FPGA的DSP Builder設(shè)計流程

Altera DSP Builder將The MathWorks MATLAB和Simulink系統(tǒng)級設(shè)計工具的算法開發(fā)、仿真和驗證功能與VHDL綜合、仿真和Altera開發(fā)工具整合在一起,實現(xiàn)了這些工具的集成。設(shè)計人員可以使用DSP Builder模塊迅速生成Simulink系統(tǒng)建模硬件,通過DSP Builder SignalCompiler模塊讀取由DSP Builder和MegaCore模塊構(gòu)建的Simulink建模文件(.mdl),生成VHDL文件和工具命令語言(Tcl)腳本,進(jìn)行綜合、硬件實施和仿真。

此系統(tǒng)設(shè)計首先用MATLAB建立DSP電路模型。電路模型設(shè)計完成后,就開始進(jìn)行系統(tǒng)功能的仿真,這是屬于系統(tǒng)級并且基于算法的仿真,與目標(biāo)器件無關(guān)。然后利用置于Simulink電路模型界面的DSP Builder中的Signal Complier將電路模型文件即Simulink模型文件(.mdl)轉(zhuǎn)化為RTL級的VHDL代碼表述和Tcl腳本。一旦獲得了VHDL描述,就可以在Simulink中調(diào)用Quartus II中的綜合器生成網(wǎng)表文件。下一步就是調(diào)用Quartus II中的編譯器,根據(jù)網(wǎng)表文件及設(shè)置的優(yōu)化條件進(jìn)行布線布局和優(yōu)化設(shè)計的適配操作,同時生成用于Moldelsim的時序仿真文件。將最后生成的Programmer Object File(.pof)對目標(biāo)器件進(jìn)行編程配置,即可在硬件上形成DSP系統(tǒng)。

3 、邊緣檢測系統(tǒng)的Simulink模型設(shè)計

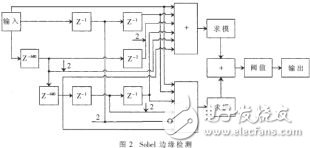

Sobel邊緣檢測模塊包括獨(dú)立且并行的水平檢測和垂直檢測兩部分。輸入緩沖通過一組延時線路轉(zhuǎn)換輸入的像素值。線路緩沖器的緩沖級數(shù)由圖像的寬度決定。本設(shè)計采用的圖像寬度是640。緩沖器的個數(shù)取決于卷積核的大小,本設(shè)計采用3×3的Sobel卷積核。垂直和水平方向的邊緣檢測幾乎是相同的,兩者之間的區(qū)別只在于從輸入緩沖器流過的數(shù)據(jù)流。最后將兩部分組合并通過閾值選擇形成一幅經(jīng)過邊緣檢測的二值圖像。Sobel邊緣檢測是流水線操作,在每一個時鐘周期都計算得到一個像素值,如圖2所示。圖中,Z-640是指本設(shè)計輸入的圖像像素寬度是640,右上角的加法模塊實現(xiàn)的是垂直方向的邊緣檢測,右下角的加法模塊實現(xiàn)的是水平方向的邊緣檢測。對于一般的灰度圖像, 其像素的灰度值一般用8位表示,考慮到計算過程中可能出現(xiàn)負(fù)數(shù)和溢出問題。因此,數(shù)據(jù)在開始計算前先在最高位補(bǔ)零,使數(shù)據(jù)寬度變?yōu)?0 位,計算完成后可再裁剪為8 位。

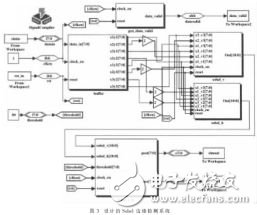

在DSP Builder中設(shè)計的Sobel邊緣檢測系統(tǒng)如圖3所示。

4 、仿真結(jié)果

建立了.mdl文件之后,在Simulink中對其進(jìn)行系統(tǒng)算法級仿真。設(shè)置Matlab各項參數(shù)和Simulink仿真參數(shù),因為本設(shè)計采用圖片的像素是640×480,所以設(shè)置仿真時間為307 201s(所有的像素數(shù)量加1)。

測試表明,仿真結(jié)果符合要求,整個系統(tǒng)算法級設(shè)計是正確的。圖4為原始的彩色圖像,圖5為經(jīng)過水平邊緣檢測和垂直邊緣檢測后沒有經(jīng)過閾值選取的圖像,圖6為經(jīng)過閾值選取后的二值圖像。Sobel算子不像普通梯度算子那樣用兩個像素的差值,而是采用兩列或兩行像素灰度加權(quán)和的差值來表示,因此有以下兩個優(yōu)點(diǎn)。

(1)由于引入了平均因素,因而對圖像中的隨機(jī)噪聲有一定的平滑作用。

(2)由于它是相隔兩行或兩列之差分,故邊緣兩側(cè)的元素得到了增強(qiáng),邊緣顯得粗而亮。

使用Modelsim進(jìn)行功能仿真,主要是調(diào)用.tcl 文件對RTL 級的VHDL 代碼仿真。由于Simulink 的仿真是算法級的,而此仿真是針對硬件結(jié)構(gòu)的,兩者之間可能存在軟件理解上的差異,所以對RTL 級VHDL 代碼的仿真是必要的。仿真結(jié)果和系統(tǒng)級仿真一致。編譯生成.pof 文件,下載到目標(biāo)芯片中,從而完成整個邊緣檢測模塊的設(shè)計。

-

dsp

+關(guān)注

關(guān)注

552文章

7962瀏覽量

348264 -

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601838 -

芯片

+關(guān)注

關(guān)注

453文章

50405瀏覽量

421812

發(fā)布評論請先 登錄

相關(guān)推薦

基于EP1C6Q240C8的FPGA芯片實現(xiàn)電子測試系統(tǒng)的設(shè)計

基于FPGA的實時邊緣檢測系統(tǒng)設(shè)計,Sobel圖像邊緣檢測,F(xiàn)PGA圖像處理

請問,如何進(jìn)行DSP編程(C語言)實現(xiàn)圖像濾波處理,及邊緣檢測??

基于FPGA的視頻實時邊緣檢測系統(tǒng)該怎么設(shè)計?

轉(zhuǎn)轍機(jī)缺口檢測怎么實現(xiàn)上傳功能?

基于DSP Builder的小波變換設(shè)計實現(xiàn)

基于CY7C68013的USB數(shù)據(jù)采集系統(tǒng)

基于DSP Builder的Chirp信號源設(shè)計

DSP Builder設(shè)計深入

基于DSP Builder的混沌保密通信研究

EP2C5T144開發(fā)板原理圖

基于Matlab/DSP Builder的系統(tǒng)實現(xiàn)

基于DSP Builder的行車道檢測設(shè)計實現(xiàn)

如何使用動態(tài)曲線進(jìn)行車道檢測算法的資料概述.

基于EP1C6芯片和DSP Builder工具實現(xiàn)行車道邊緣檢測系統(tǒng)的設(shè)計

基于EP1C6芯片和DSP Builder工具實現(xiàn)行車道邊緣檢測系統(tǒng)的設(shè)計

評論