隨著大規(guī)模集成電路技術和微型計算機技術的飛速發(fā)展,計算機化已經(jīng)成為遙測技術發(fā)展的方向和特征。傳統(tǒng)的模擬式頻分多路遙測系統(tǒng)已越來越無法適應現(xiàn)代遙測技術的發(fā)展。因為它具有以下致命的缺點:(1)解調輸出的模擬信號無法直接供計算機處理和分析;(2)系統(tǒng)參數(shù)一旦設定,就無法改變,系統(tǒng)靈活性差。為了克服以上缺點,有必要對模擬式頻分多路遙測系統(tǒng)進行根本性的變革,研制新型的數(shù)字式頻分多路副載波解調器。

幸運的是,數(shù)字信號處理技術和大規(guī)模集成電路技術的迅猛發(fā)展,為我們設計數(shù)字式頻分多路副載波解調器提供了新思路和新方法。近幾年來,現(xiàn)場可編程門陣列(FPGA)因其具有集成度高、處理速度快以及執(zhí)行效率高等優(yōu)點?1,在數(shù)字系統(tǒng)的設計中得到了廣泛應用。本文所提及的數(shù)字式頻分多路副載波解調器就是利用FPGA技術來實現(xiàn)的。

1 總體設計方案

設計的數(shù)字式頻分多路遙測系統(tǒng)副載波解調器是IRIG-CBW-E標準的,即通道中心頻率分別為128、256、384、512、640和768kHz,頻偏為32kHz,調制信號頻率范圍為100Hz~25kHz。

1.1 系統(tǒng)組成

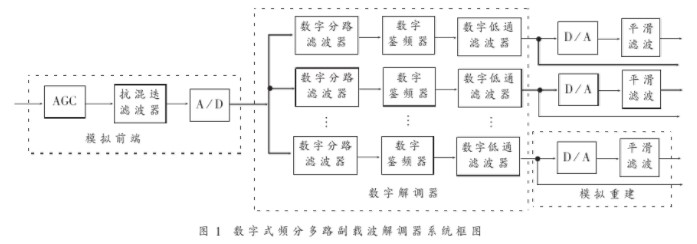

該數(shù)字式頻分多路副載波解調器應用了數(shù)字信號處理技術和頻譜搬移的思想,先將模擬調頻信號數(shù)字化,再對其進行數(shù)字式解調。解調后輸出的是數(shù)字信號,可以直接供數(shù)字化設備進行存儲和分析。另外,也可將該數(shù)字信號進行模擬重建,恢復出原始模擬信號。其組成框圖如圖1所示。

由圖1可見,數(shù)字式頻分多路副載波解調器主要由模擬前端、數(shù)字解調器和模擬重建部分等三部分構成。其中,模擬前端包括AGC電路、抗混迭濾波器及A/D變換器。

模擬前端作為模擬部分和數(shù)字部分的接口電路,主要完成多路調頻信號的預處理和A/D變換。模擬重建部分包括D/A變換器和平滑濾波器。它將解調后的數(shù)字信號轉換成模擬信號。并放大到所需電平。

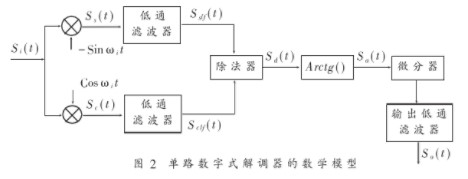

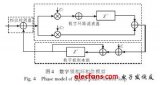

數(shù)字解調器是系統(tǒng)的核心。它由數(shù)字式分路濾波器、數(shù)字式鑒頻器以及數(shù)字式低通濾波器三部分構成。它將完成多路調頻信號的分路濾波和解調任務。圖2給出了單路數(shù)字式解調器的數(shù)學模型。

由圖2可以看出,我們并沒有采用數(shù)字式鎖相環(huán),而是采用數(shù)字信號處理(DSP)算法來實現(xiàn)解調。這種方案更適合用FPGA來實現(xiàn)。

為了便于調試,在進行硬件電路設計時,將數(shù)字解調器、A/D及D/A三部分分別放在不同的電路板上,通過雙排插頭進行連接。A/D變換器是依據(jù)數(shù)字解調器的采樣頻率和數(shù)據(jù)寬度進行選擇的。因數(shù)字解調器的采樣頻率為2.56kHz,數(shù)據(jù)位寬為8位,故選擇了易于調試的8位高速模/數(shù)轉換器TLC5510。D/A變換器選用了Maxim公司的MX7545。而數(shù)字解調器選用了Altera公司的FLEX10K系列器件。利用MAX+ plusII進行硬件仿真時,單路數(shù)字解調器共需三塊FLEX10K50,且其利用率可達75%以上。若重復采用相同的方法進行多路信號的解調,必然會使硬件資源成倍增加。顯然,這是不經(jīng)濟和不可行的。因此,如何在不增加或少增加系統(tǒng)硬件規(guī)模的前提下,完成對多路信號的解調,則成為設計過程中要著重解決的關鍵問題。

2 關鍵技術

為了在盡可能節(jié)省系統(tǒng)資源的前提下,完成多路信號的解調任務,采用了時分復用的方法。利用FPGA實現(xiàn)數(shù)字式解調器,具備了時分復用的條件。

一方面,采用的FPGA其處理數(shù)據(jù)的速度可達100MSPS,而本系統(tǒng)采樣率為2.56MHz,即要求處理速度為2.56MSPS,所以從理論上說,利用它同時處理30路以上的信號是有可能的。考慮到實際系統(tǒng)不可能工作在最大處理速度下,假定只能達到最大速度的1/3,則采用時分復用后,至少也能同時處理10路以上的信號。

另一方面,由于每一路分路濾波器(包括同相支路和正交支路)都采用64階FIR低通濾波器,其帶寬、過渡帶帶寬和阻帶衰減完全相同,也就是說沖激響應完全相同,所以構成FIR濾波器的矢量乘法器可以重復利用。每一路輸出低通濾波器也都具有相同的電路結構。在原理上,它與分路濾波器完全相同,因此這里只以分路濾波器為例進行討論。FIR濾波器主要由移位寄存器、相加器及矢量乘法器構成?2,其中矢量乘法器在FIR濾波器中占用了大部分硬件資源。因此,節(jié)省矢量乘法器,便可以節(jié)省系統(tǒng)資源。由此可見,時分復用的實質是指矢量乘法器的時分復用。

下面以實例說明時分復用的實現(xiàn)方法。

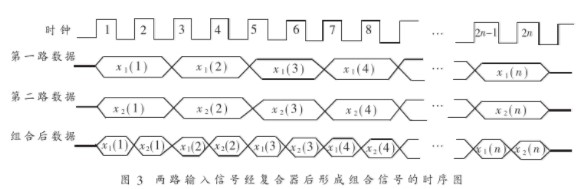

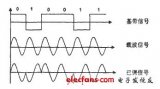

為討論方便,假定FIR濾波器的階數(shù)為8階,時分復用的路數(shù)k=2。設FIR濾波器的沖激響應為h?n,第一路輸入信號為x1?n,第二路輸入信號為x2?n,濾波器的工作頻率為2倍輸入數(shù)據(jù)率。兩路信號經(jīng)復合器形成組合信號,其時序如圖3所示。

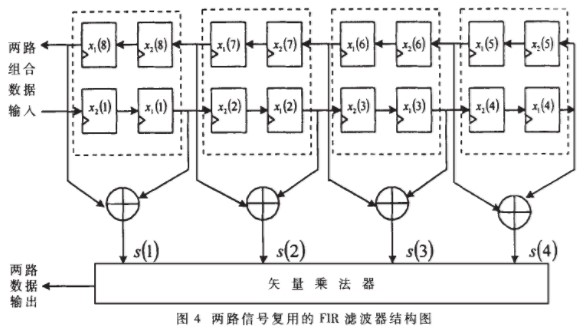

由圖3可以看出,復合器輸出的組合信號實際上是將第一路信號和第二路信號進行了交織,在奇數(shù)時刻出現(xiàn)的為第一路信號,在偶數(shù)時刻出現(xiàn)的為第二路信號。為使同一路信號同時從移位相加器中輸出到矢量乘法器,必須保證在奇數(shù)時刻移位相加器輸出的信號都為第一路信號,而偶數(shù)時刻輸出的信號都為第二路信號。此外還要保證兩路數(shù)據(jù)都能夠在時鐘的控制下順序移位。為了滿足上述條件,設計了兩路信號復用的FIR濾波器,其結構框圖如圖4所示。

該濾波器只是在8階FIR濾波器的基礎上增加了8個移位寄存器?3,正是這8個移位寄存器使得矢量乘法器計算第一路信號時,第二路信號得以緩存;而在下一時刻到來時,才將第二路信號輸出給矢量乘法器。這樣就完成了兩路信號的同時濾波。濾波后的信號仍以交織的形式輸出,可利用分路器將它們分開。

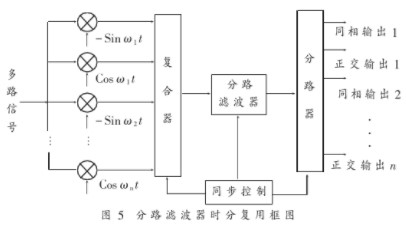

同理,如果同時進行k路濾波,則濾波器中移位寄存器的個數(shù)將是單路FIR濾波器中移位寄存器個數(shù)的k倍。即假定FIR濾波器的階數(shù)為N,則單路濾波器需要移位寄存器的個數(shù)為N,k路濾波器需要的移位寄存器個數(shù)為k·N。 另外,值得注意的是:采用時分復用方法后,整個系統(tǒng)就工作于不同的時鐘頻率下。假定系統(tǒng)采樣頻率為fs,進行時分復用后同時處理k路信號,則非時分復用部分的時鐘頻率為fs,時分復用部分的時鐘頻率為k·fs為使系統(tǒng)能夠正常工作,還要在系統(tǒng)中加上時鐘和控制電路,以控制系統(tǒng)的時鐘和同步。圖5給出了分路濾波器的時分復用框圖。

利用MAX+plusII對兩路信號復用濾波器的AHDL源代碼進行編譯,發(fā)現(xiàn)兩路信號復用濾波器比單路濾波器多用的硬件資源不到單路硬件資源的20%。所以說,利用時分復用的方法達到了預期目標。

這種基于FPGA的數(shù)字式解調器的優(yōu)點是容易和計算機相結合形成數(shù)字式FM-FM遙測數(shù)據(jù)處理系統(tǒng)。一方面,遙測數(shù)據(jù)可以傳送給計算機,進行存儲、分析和顯示;另一方面,計算機也可以給數(shù)字式解調器加載不同的程序,以改變解調器的參數(shù)設置,使之適合于IRIG的全部標準。

但是,該數(shù)字式解調器仍有其不足之處,即運算精度不夠高,因為利用FPGA難以進行浮點運算。如果濾波器用FPGA實現(xiàn),數(shù)據(jù)寬度取12bit,鑒頻器用DSP實現(xiàn),采用浮點運算,則系統(tǒng)精度必會得到改善,但付出的代價是系統(tǒng)復雜度增加。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602037 -

集成電路

+關注

關注

5382文章

11396瀏覽量

360953 -

數(shù)字信號處理

+關注

關注

15文章

559瀏覽量

45801

發(fā)布評論請先 登錄

相關推薦

解調器

一種基于FPGA的全數(shù)字短波解調器設計

如何利用FPGA技術實現(xiàn)數(shù)字式頻分多路副載波解調器的設計?

全數(shù)字QAM解調器方案采用了載波相位和符號定時的聯(lián)合估計環(huán)——基于FPGA的同步電路設計與實現(xiàn)研究 精選資料分享

基于FPGA的QPSK解調器的設計與實現(xiàn)

基于FPGA的OQPSK解調器的設計與實現(xiàn)

一種全數(shù)字BPSK解調器的設計與FPGA實現(xiàn)

基于FPGA的MSK調制解調器設計與應用

一種全數(shù)字BPSK解調器的設計與FPGA實現(xiàn)

認知無線電中自適應調制解調器的FPGA實現(xiàn)

基于FPGA的全新數(shù)字化PCM中頻解調器設計

基于FPGA的BPSK調制與解調器設計

基于FPGA技術實現(xiàn)數(shù)字式解調器的設計

基于FPGA技術實現(xiàn)數(shù)字式解調器的設計

評論