20世紀80年代初興起的RISC技術一直是計算機發展的主流,RISC微處理器的一些基本理論則是計算機領域的重要基礎常識,但具體實現仍有難度。電子設計自動化(Electronic Design Automation,簡稱EDA)是現代電子設計的核心技術。利用EDA技術進行電子系統設計的主要目標是完成專用集成電路(ASIC)的設計,而現場可編程門陣列(FPGA)和復雜可編程邏輯器件(CPLD)是實現這一途徑的主流器件。現場可編程通用門陣列(Field Program mableGateArray,簡稱FPGA)的內部具有豐富的可編程資源。FPGA外部連線很少、電路簡單、便于控制。FPGA目前已達千萬門標記(10million-gatemark),速度可達200~400MHz。本文介紹了一種基于FPGA技術用VHDL(VHSICHardw are Description Language)語言實現的8位RISC微處理器,并給出了仿真綜合結果。

微處理器功能、組成及指令集

本文設計的RISC微處理器遵循了RISC機器的一般原則:指令條數少而高效、指令長度固定、尋址方式不超過兩種、大量采用寄存器、為提高指令執行速度、指令的解釋采用硬聯線控制等等。

RISC微處理器的功能和組成

微處理器是整個計算機系統的核心,它具有如下基本功能:指令控制、操作控制、時間控制、數據加工。本文設計的微處理器主要由控制器、運算器和寄存器組成,還包括程序計數器、譯碼器等一些其他的必要邏輯部件。控制器是發布命令的“決策機構”,即完成協調和指揮整個計算機系統的操作。相對于控制器而言,運算器接受控制器的命令而進行動作,即運算器所進行的全部操作都是由控制器發出的控制信號來指揮的,所以它是執行部件。存儲器是記憶設備,存儲單元長度是8位,用來存放程序和數據。

微處理器的指令集

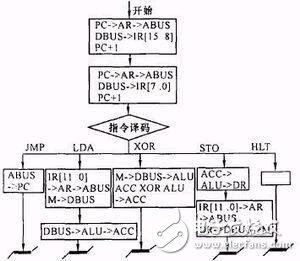

微處理器的指令長度為16位定長,每條指令占兩個存儲單元,尋址方式僅有立即尋址、直接尋址兩種。該RISC微處理器選取了使用頻度較高的8種指令LDA、STO、JMP、ADD、AND、XOR、SKZ、HLT等。指令操作碼占用指令字的高4位,預留了空間,便于以后指令集的擴展。指令周期是由8個時鐘組成,每個時鐘都要完成固定的操作。部分典型指令的操作流程圖如圖1所示。

圖1部分指令操作流程

關鍵模塊的設計

RISC微處理器是一個復雜的數字邏輯電路,但其基本部件的邏輯并不復雜,可以把它分為時鐘產生器、指令寄存器、累加器、算術邏輯單元、數據控制器、狀態控制器、程序計數器、地址多路器等單元來考慮。在硬件驗證時還需要建立一些如ROM/RAM和地址譯碼器等必要的外圍器件。以下是幾個關鍵模塊的設計。

時鐘產生器的設計

圖2時鐘產生器電路的設計

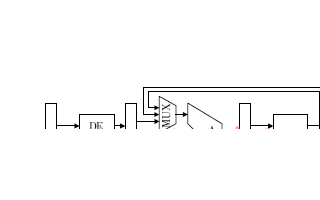

時鐘產生器Pulse產生的電路如圖2所示,計算機的協調動作需要時間標志,它用時序信號體現,時鐘產生器正是產生這些時序信號的器件。圖2中時鐘產生器利用外來時鐘信號clk產生一系列時鐘信號clk1,fetch,aluclk等,并送往微處理器的其他部件。rst控制著微處理器的復位和啟動操作,當rst一進入高電平,微處理器就結束現行操作,并且只要rst停留在高電平狀態,微處理器就維持復位狀態。rst回到低電平后在接著到來的fetch上升沿啟動微處理器開始工作。

由于時鐘產生器對微處理器各種操作實施時間上的控制,所以其性能好壞從根本上決定了整個微處理器的運行質量。本設計采用的同步狀態機的設計方法,使得clk1,fetch,alu_clk在跳變時間同步性能上有顯著提升,為整個系統性能的提高打下良好的基礎。

狀態控制器的設計

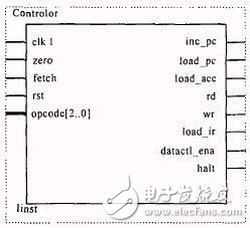

狀態控制器的電路圖如圖3所示。從實現的途徑看,RISC微處理器與一般的微處理器的不同之處在于,它的時序控制信號的形成部件是用硬布線邏輯實現而不是采用微程序控制。由于器件本身設計比較復雜,且對各個控制信號的時序有嚴格要求,所以其VHDL程序用有限狀態機FSM來實現。

圖3狀態控制器電路

結構體程序如下:

architecturertlofstatctlis

typemystateis(st0,st1,st2,st3,st4,st5,st6,st7);

signalcurstate:mystate;

begin

process(clk1,ena)

begin

iffallingedge(clk1)then

if(ena=’0’)then

curstate《=st0;incpc《=’0’;

load_acc《=’0’;loadpc《=’0’;

rd《=’0’;wr《=’0’;loadir《=’0’;

datactlena《=’0’;halt《=’0’;

else

casecurstateis

whenst0=》。..。..

whenst1=》。..。..

whenst2=》。..。..

whenst3=》cur_state《=st4;

if(opcode=hlt)then.。..。.

else.。..。.

whenst4=》curstate《=st5;

if(opcode=jmp)then.。..。.

elsif(opcode=addoropcode=ann

oropcode=“xoooropcode”=lda)then

elsif(opcode=sto)then.。.else.。.

whenst5=》curstate《=st6;

if(opcode=addoropcode=annor

opcode=“xoooropcode”=lda)

then.。..。.

elsif(opcode=skzandzero=’1’)

then.。..。.

elsif(opcode=jmp)then.。..。.

elsif(opcode=sto)then.。..。.

else.。..。.

whenst6=》curstate《=st7;

if(opcode=sto)then.。..。.

elsif(opcode=addoropcode=ann

oropcode=xoooropcode=lda)

then.。..。.

else.。..。.

whenst7=》curstate《=st0;

if(opcode=skzandzero=’1’)then.。..。.

else.。..。.

whenothers=》。..。..

endcase;

endif;

endif;

endprocess;

endrtl;

算術邏輯單元ALU的設計

ALU是絕大多數指令必須經過的單元,所有的運算都在算術邏輯單元ALU進行。ALU接受指令寄存器IR送來的4位指令操作碼,根據不同的指令,ALU在信號alu_clk的正跳變沿觸發下完成各種算術邏輯運算。微處理器各部件結構如圖4所示。

軟件綜合與仿真和硬件實現

微處理器的軟件綜合與仿真

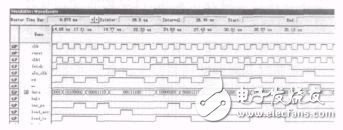

該微處理器設計共有11個基本模塊,除前文分析的3個模塊外,還有指令寄存器IR、累加器ACC、程序計數器PC、簡單的存儲器ROM/RAM、地址多路器ADDR等模塊。所有的模塊采用Quartus4.2單獨綜合,并調試通過,且都生成有單獨的*.bsf文件,最后創建一個頂層文件top.bdf,把所有基本模塊的bsf文件連接成如圖4的形式。做完頂層設計后,采用Quartus4.2進行綜合與仿真。系統仿真的部分結果如圖5所示,從圖5可以看出,存放在存儲器不同地址中的2個操作數3CH(00111100)和18H(00011000)相異或時,結果24H(00100100)在信號wr的上升沿觸發下存入存儲器中。我們可清楚地看到每條指令都是在一個指令周期中完成。數據總線data上記錄著指令的運行情況,同時也可看到空閑時其呈高阻狀態。

圖4微處理器各部件的結構

圖5仿真波形

主要的程序如下:

地址機器代碼匯編語言源程序

&

nbsp; 0011000000JMPL1;L1-》PC

0100000100

0410100000LDAR2;(0E)-》R2

0500001110

0610000000XORR1,R2;(R1)xor(R2)- 》(R1)

0700001111

0811000001STO;(R1)-》(0F)

0A00000000HLT;stop

0B00000000

0E00111100

0F00011000

微處理器的硬件實現

基于FPGA的RISC微處理器的最終硬件驗證在杭州康芯公司生產的GW48EDA系統上進行。前面的仿真結果確認無誤后,選用GW48EDA系統的電路模式No.5,查閱此系統的引腳對照表鎖定各引腳,之后需重新編譯一次,以便把引腳鎖定信息編譯進編程下載文件。最后把編譯好的top.sof文件對目標器件FPGA下載,得到滿足設計要求的芯片。本設計的載體選用Altera公司的Cyclone系列FPGA器件EP1C6Q240C6,硬件驗證結果表明,該RISC微處理器時鐘頻率為23.02MHz,其功能完全達到設計要求。

結束語

本文基于FPGA的微處理器具備了RISC微處理器的基本功能,而且其容易優化升級。該微處理器不僅可作為一個模塊用于片上系統的設計,而且也充分展示了使用FPGA和VHDL進行EDA數字系統設計的優越性,具有實用價值。

-

FPGA

+關注

關注

1626文章

21670瀏覽量

601875 -

cpld

+關注

關注

32文章

1247瀏覽量

169220 -

微處理器

+關注

關注

11文章

2247瀏覽量

82321

發布評論請先 登錄

相關推薦

基于AVR 8位微處理器的FSPLC微處理器SOC設計

基于80C186XL16位嵌入式微處理器的CPLD解決方案

ARM微處理器介紹

ARM處理器設計RISC介紹(下)

16位低功耗微處理器的設計

通用微處理器功能驗證中的仿真加速

基于FPGA的VLIW微處理器基本功能實現設計

利用FPGA和CPLD技術實現8位RISC微處理器的設計并進行仿真分析

利用FPGA和CPLD技術實現8位RISC微處理器的設計并進行仿真分析

評論