PLD(可編程邏輯器件)以其操作靈活、使用方便、開發(fā)迅速、投資風(fēng)險低的特點,很快發(fā)展起來,并越來越受人們的矚目。PLD是可以由用戶在工作現(xiàn)場編程的邏輯器件,它從簡單的PAL、GAL,已發(fā)展到CPLD、EPLD、FPGA和FLEX系列。他們都具有體系結(jié)構(gòu)和邏輯單元靈活、集成度高以及適用范圍廣等特點。

同以往的PAL、GAL等相比較,F(xiàn)PGA/CPLD的規(guī)模比較大,適合于時序、組合等邏輯電路等場合應(yīng)用。可編程邏輯器件易學(xué)、易用,簡化了系統(tǒng)設(shè)計,縮小了系統(tǒng)規(guī)模,提高了系統(tǒng)的可靠性。一個器件的可用門已達(dá)數(shù)萬門,引腳間延時僅幾ns,而且仍在朝著高密度、高速度的方向迅速發(fā)展。

計算機(jī)總線是計算機(jī)各部件之間進(jìn)行信息傳輸?shù)墓餐ǖ馈T诋?dāng)今的微型機(jī)中主要采用的是PCI總線,ISA、EISA總線正逐步被淘汰。所以對硬件設(shè)計人員來說,掌握PCI總線板卡的開發(fā)技術(shù)是非常重要的。板卡的設(shè)計方法通常有這么幾種:一是做ASIC,開發(fā)周期長;另一種是在專用接口芯片下開發(fā),但使用不是很靈活,系統(tǒng)規(guī)模大;目前最新的方法是用PLD來開發(fā)設(shè)計。

在進(jìn)行CPLD設(shè)計時,筆者使用的軟件是Altera的MAX+PLUSII。Altera的MAX+PLUSII開發(fā)系統(tǒng)是一個完全集成化、易學(xué)易用的、與結(jié)構(gòu)無關(guān)的可編程邏輯設(shè)計環(huán)境,它使通用系列設(shè)計者能方便的進(jìn)行設(shè)計輸入、快速處理和器件編程,使用此軟件的設(shè)計方法是很靈活的,可以采用硬件描述語言(PLD)、電路圖,甚至是時序圖。根據(jù)不同的情況可以采用不同的方法,在一個設(shè)計中也可以采用多種方法。下面以一個簡單的PCI從設(shè)備設(shè)計為例,說明設(shè)計思想與過程。

在本例中,設(shè)計的PCI卡作為從設(shè)備使用,可以實現(xiàn)即插即用功能,卡上有1MB的存儲器可供使用。在PCI即插即用板卡的設(shè)計中,核心設(shè)計有兩部分:時序控制和配置空間。時序控制保證了板卡能按正常的PCI時序工作,配置空間部分保證了板卡的即插即用功能。

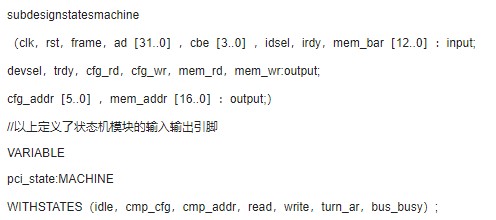

在本例中,這兩部分都由AHDL語言來實現(xiàn)的(AHDL語言是Altera公司專門為其芯片設(shè)計開發(fā)的一種硬件描述語言)。在時序控制程序中采用狀態(tài)機(jī)模型來實現(xiàn)不同時序的轉(zhuǎn)換,采用這種方式既節(jié)省資源,程序也簡單易懂。

本例中的狀態(tài)機(jī)共使用了七種狀態(tài),分別對應(yīng)空閑、存儲器讀寫的判斷、配置讀寫的判斷、讀、寫、過渡周期、總線忙周期的時序。板卡接到復(fù)位信號后,對系統(tǒng)進(jìn)行復(fù)位,然后轉(zhuǎn)入空閑狀態(tài)。在空閑狀態(tài)中采樣總線,并根據(jù)總線的變化來決定下一個時鐘上升沿后,狀態(tài)機(jī)轉(zhuǎn)入何種狀態(tài)。這些時序和程序中用到的信號都是基本且必須的。在進(jìn)行開發(fā)時可以根據(jù)需要增添必要的狀態(tài)和信號。程序描述如下:

//定義狀態(tài)機(jī)變量,共有七個狀態(tài)空閑狀態(tài)idle,配置空間操作cmp_cfg,比較地址cmp_addr,讀狀態(tài)read,寫狀態(tài)write,過渡周期狀態(tài)turn_ar,總線忙狀態(tài)bus_busy。通過狀態(tài)機(jī)的不同狀態(tài)實現(xiàn)時序的轉(zhuǎn)換,在每個狀態(tài)中實現(xiàn)不同的時序周期。

BEGIN

初始化:對內(nèi)部信號和各個輸入輸出引腳進(jìn)行初始化,設(shè)定它們的連接關(guān)系。

IFrst==b“0”THEN//判斷是否復(fù)位

實現(xiàn)復(fù)位的時序操作。

ELSE

CASEpci_stateIS

WHENidle=》//空閑狀態(tài)

在此狀態(tài)中,每個時鐘周期判斷frame和idsel信號的變化,一旦發(fā)現(xiàn)frame被置為有效,就根據(jù)idsel信號判斷下一狀態(tài)轉(zhuǎn)入對配置空間操作的cmp_cfg或是比較地址對存儲器操作的cmp_addr

WHENcmp_cfg=》//對配置空間操作的狀態(tài)

在此狀態(tài)中根據(jù)地址線的低兩位判斷是否是對配置空間的操作,若不是轉(zhuǎn)入總線忙狀態(tài)bus_busy;若是則根據(jù)cbe的信號是A或B來判斷是讀還是寫,轉(zhuǎn)入相應(yīng)的狀態(tài)read,write。

WHENcmp_addr=》//地址比較狀態(tài)

在此狀態(tài)中判斷要讀寫地址的高位與配置空間中分配的地址是否相同,若不同轉(zhuǎn)入總線忙狀態(tài)bus_busy;若相同則根據(jù)cbe的信號是6或7來判斷是讀還是寫,轉(zhuǎn)入相應(yīng)的狀態(tài)read,write。

WHENread=》//讀狀態(tài)

在此狀態(tài)中,根據(jù)cbe的值判斷是配置讀還是存儲讀,然后控制輸出信號mem_rd,cfg_rd,trdy,devsel產(chǎn)生相應(yīng)的讀時序,同時在此周期中判斷frame,irdy信號,若irdy變低并且frame變高,則讀狀態(tài)結(jié)束,轉(zhuǎn)入turn_ar狀態(tài).

WHENwrite=》//寫狀態(tài)

在此狀態(tài)中,根據(jù)cbe的值判斷是配置寫還是存儲寫,然后控制輸出信號mem_wr,cfg_wr,trdy,devsel產(chǎn)生相應(yīng)的寫時序,同時在此周期中判斷frame,irdy信號,若irdy變低并且frame變高,則寫狀態(tài)結(jié)束,轉(zhuǎn)入turn_ar狀態(tài)。

WHENturn_ar=》//信號的過渡周期狀態(tài)

按照PCI的總線規(guī)范,S/T/S信號,從有效變?yōu)楦】罩氨仨毐WC使其具有至少一個時鐘周期的高電平狀態(tài),此狀態(tài)中,將所有的S/T/S信號置為高。

WHENbus_busy=》//總線忙狀態(tài)

總線不對本卡操作,因此通過對frame信號的判斷,來決定何時脫離本狀態(tài)。

WHENOTHERS=》

若進(jìn)入此狀態(tài),則應(yīng)根據(jù)需要,馬上轉(zhuǎn)入bus_busy或idle

ENDCASE;

ENDIF;

END;

配置空間部分也采用AHDL語言來描述實現(xiàn),在配置空間中定義PCI卡的功能、內(nèi)存空間的分配、以及產(chǎn)品號、ID號等.通過對配置空間的定義,才能保證板卡的即插即用功能.描述如下:

寫入系統(tǒng)啟動時分配給本卡的中斷向量

endif;

end;

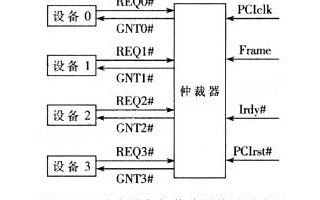

兩部分都通過軟件生成模塊,兩模塊之間的接口部分,可以很容易的通過電路圖的連接來實現(xiàn)。兩個模塊圖如圖。

使用CPLD技術(shù)開發(fā)PCI板卡有以下優(yōu)點:

1、開發(fā)周期短、成本低、投資風(fēng)險小,標(biāo)準(zhǔn)產(chǎn)品無需測試、質(zhì)量穩(wěn)定,可實時在線檢驗。采用CPLD技術(shù)設(shè)計完成后,可以進(jìn)行實時的時序仿真。驗證改進(jìn)設(shè)計結(jié)果,而不需重復(fù)的硬件試驗。設(shè)計通過后寫入芯片,通過測試即可投入使用。比使用一些專用的PCI芯片開發(fā)要簡單,而且省去了其他開發(fā)設(shè)備,所以成本也較低。比之ASIC開發(fā)的周期則要短的多。

2、使用靈活方便。由于開發(fā)的板卡是直接在總線的基本規(guī)范上進(jìn)行,沒有使用一些專用芯片,因而開發(fā)更靈活、自由,受到的限制更少,整個硬件模塊的規(guī)模也較小,可以將很多自己的算法與技術(shù)和PCI合成在一起,做出技術(shù)含量更高的產(chǎn)品。

3、有利于知識產(chǎn)權(quán)的保護(hù)和軟件性能的提高。利用這項技術(shù)可以將自己的的算法、技術(shù)和一些軟件做成硬件固化到卡上,既提高了運(yùn)行速度,也使盜版者難以復(fù)制。

本文結(jié)合一個實例給出了在PCI總線上利用CPLD技術(shù)設(shè)計各種板卡的設(shè)計方案,簡單實用,有很高的應(yīng)用價值。

-

cpld

+關(guān)注

關(guān)注

32文章

1247瀏覽量

169217 -

pci總線

+關(guān)注

關(guān)注

1文章

203瀏覽量

31797 -

vhdl

+關(guān)注

關(guān)注

30文章

816瀏覽量

128078

發(fā)布評論請先 登錄

相關(guān)推薦

基于CPLD器件實現(xiàn)雙主設(shè)備PCI總線仲裁器的設(shè)計

采用PCI總線流水式高速數(shù)據(jù)采集系統(tǒng)設(shè)計

采用CH365芯片實現(xiàn)PCI總線接口卡設(shè)計

基于PCI總線的CPLD實現(xiàn)

采用PCI總線集成電路實現(xiàn)測試儀接口設(shè)計

采用CPLD實現(xiàn)32 bit 33 MHzPCI從設(shè)備接口

使用CPLD技術(shù)開發(fā)PCI板卡有什么優(yōu)點?

求一款在PCI總線上利用FPGA技術(shù)設(shè)計PCI總線接口的設(shè)計方案

PCI總線至UTOPIA接口控制的CPLD設(shè)計實現(xiàn)

AMCCS5933 在PCI板卡設(shè)計中的應(yīng)用

CPLD在基于PCI總線的功率模塊設(shè)計中的應(yīng)用

PCI總線從設(shè)備接口的CPLD實現(xiàn)

PCI總線接口芯片可以在哪里應(yīng)用

采用CPLD技術(shù)實現(xiàn)PCI從設(shè)備接口的設(shè)計

在PCI總線上采用CPLD技術(shù)實現(xiàn)多種板卡的設(shè)計

在PCI總線上采用CPLD技術(shù)實現(xiàn)多種板卡的設(shè)計

評論