電容式觸摸感應檢測按鍵電路是一類對靜電特別敏感的電路,因此靜電放電(ESD)保護結構的選擇問題對這一類電路顯得特別重要。一方面要確保所選擇的ESD保護結構有足夠的抗靜電能力,另一方面這種ESD保護結構又不能使芯片的面積和成本增加太多,基于此要求,介紹了3種應用在電容式觸摸感應檢測按鍵電路中的ESD保護結構。主要描述了這3種結構的電路形式和版圖布局,著重闡述了為滿足電容式觸摸感應檢測按鍵電路的具體要求而對這3種結構所作的改進。列出了這3種改進過后的ESD保護結構的特點、所占用芯片面積以及抗靜電能力測試結果的比較。結果表明,經過改進后的3種ESD保護結構在保護能力、芯片面積利用率以及可靠性等方面都有了非常好的提升。

電容式觸摸感應檢測按鍵電路是近年來行業內較高的集成電路產品,這類電路通常設有一路或者多路高靈敏度的感應輸入端,實際應用時通過人體手指靠近芯片檢測電荷的移動,產生額外電容而改變頻率或占空比,從而判斷人體手指觸摸動作,實現按鍵功能。眾所周知人體是最大的靜電攜帶者,因此在人體手指靠近芯片時會有大量靜電向芯片傳送,將產生潛在的破壞電壓、電流以及電磁場,從而將芯片擊毀,這就是靜電保護(electronic staticdischarge,ESD)問題。ESD是金屬-氧化物-半導體(metal-oxide-semiconductor,MOS)集成電路中最重要的可靠性問題之一,尤其是針對本文所討論的電容式觸摸感應檢測按鍵電路。為了保證高可靠性,這類電路的ESD保護能力通常要求達到8000 V,甚至要達到10 000 V,因此必須通過在電路中加入有效的ESD保護結構才能滿足設計要求。此外,這種保護結構又不能占用太多的芯片面積,否則將明顯增加芯片成本,從而限制芯片的推廣應用。因此如何選擇合適的ESD保護結構,既能保護這一類觸摸感應按鍵檢測電路,又不至于太多增加芯片成本是這類電路設計中至關重要的問題。

本文介紹了3種應用于筆者所開發的電容式觸摸感應檢測按鍵電路中的ESD保護結構。這3種保護結構在傳統ESD結構基礎上結合電容式觸摸感應檢測按鍵電路的具體特點進行全面改進,以達到保護電路且盡量少地增加芯片面積的要求。這些結構也適用于其他類似的電路,希望能夠給廣大從事集成電路設計的工程師在考慮ESD問題時提供一些參考設計。

1、3種ESD保護結構

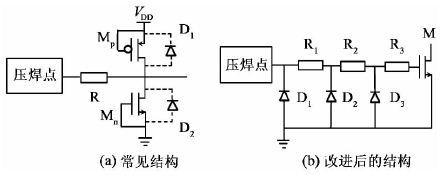

圖1(a)是MOS集成電路中最常見的一種ESD保護結構。需要在電路的每一個壓焊點都插入該結構,保護圖中的Mp和Mn兩個MOS管。這種結構包括與壓焊點直接相連的柵極和源極短接的PMOS管Mp以及柵極和源極短接的NMOS管Mn.其中Mp和Mn這兩個管子可以等效成兩個二極管D1和D2.實際應用時在壓焊點上會引入較大的靜電,根據晶體管原理,這個較大的靜電會引起Mp和Mn兩個管子被雪崩擊穿。通過插入圖1(a)中的ESD保護結構,在這個大靜電還沒有到達Mp和Mn之前首先引起兩個二極管D1和D2反向擊穿,形成到電源和地的電流通路,把大電流泄放掉;另外電阻R起限流作用。這兩個措施就起到了保護Mp和Mn的作用。這種ESD保護結構的ESD保護能力通常在2000~3000V.為了進一步提高ESD保護能力,在電容式觸摸感應檢測按鍵電路中對這種結構進行改進,如圖1(b)所示。圖1(b)顯示了一種針對NMOS管的三級二極管加電阻網絡的ESD保護結構,針對PMOS管的保護結構與此類似。每一級的原理與圖1(a)類似,但這種結構能夠利用三級電阻和二極管網絡的限流和分壓作用提供多個泄放通路,從而逐級泄放大電流,提高ESD保護能力。以圖1(b)中的MOS管Mn為例來說明這種改進的ESD保護結構的電路結構參數應該如何選擇。Mn的柵擊穿電壓是12.5V,按照ESD保護原理,經過多級限流電阻之后落在Mn柵極的電壓須小于這個管子的柵擊穿電壓,保護電路才能起到保護作用,通過計算,采用三級二極管加電阻網絡結構可以達到保護Mn的目的,其中每一級限流電阻值為100Ω,而D1,D2和D3 3個二極管也可以采用圖1(a)中所示的柵極和源極短接的MOS管。

1.2、可控硅整流器的ESD保護結構

圖2(a)是可控硅整流器(silicon controlledrectifiers,SCR)ESD保護結構的縱向剖面圖,圖2(b)是這種結構的等效電路圖。

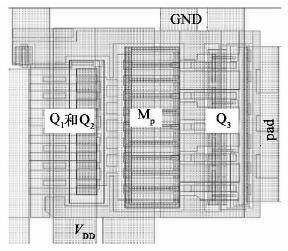

圖2(b)中Mp是一個柵極和源極短接的PMOS管,起到ESD保護作用;Q1是一個pnp型三極管,其發射區是由n阱內的p+擴散區構成,n阱是它的基區,p襯底作為集電區;另一個Q2是npn型三極管,阱外的n+是其發射區,p襯底是它的基區,n阱是集電區。以上兩個管子組成一個稱之為可控硅整流器的4層半導體器件。這4層依次是p+擴散區、n阱、p襯底和n+擴散區,此種pnpn結構內有npn和pnp之間的正反饋,提供了良好的ESD泄放通路,具有非常明顯的ESD保護性能。因此在芯片的每一個壓焊點上都插入這樣一個結構,就能在最小的布局面積下提供最高的ESD防護能力。圖2(b)中R1是n阱接觸電阻,R2是p襯底接觸電阻。

據半導體器件原理,上述的4層結構作為ESD保護器件來說,其起始導通電壓等效于MOS工藝下n阱與p襯底之間的擊穿電壓。由于n阱具有較低的摻雜濃度,這是由半導體工藝所決定的,因此其與p襯底之間的擊穿電壓高達30~50V,如此高的擊穿電壓使SCR結構在ESD防護設計上需要再加上額外的二級保護結構,在圖2(b)中已經標注出來。這是因為圖2(b)中需要保護的MOS管M的柵擊穿電壓只有12.5V左右,而SCR要到30V以上才導通,在ESD電壓尚未升到30V之前,這個SCR結構是關閉的,這時SCR器件所要保護的M管早就被ESD電壓破壞了,因此必須加入二級保護結構。利用這個二級保護結構,在其被ESD破壞之前,SCR結構能夠被觸發導通,從而泄放ESD電流,只要SCR結構一導通,其低的保持電壓便會鉗制住ESD電壓在很低的值,因此這個SCR結構可以有效地保護M管。但這種額外增加的二級保護結構必然會造成芯片面積的增加,導致芯片成本的上升。

為解決這個問題,在電容式觸摸感應檢測按鍵電路中采用了一種改進的SCR ESD保護結構。在該結構中增加一個圖2(b)虛線框中所示的薄柵氧NMOS管Q3.依據晶體管原理,擊穿電壓與柵氧是直接相關的。這個NMOS管以橫跨的方式在n阱與p襯底的界面上,可以使SCR結構的起始導通電壓下降到10~15V,這就使SCR結構不需要額外的二級保護結構便可以有效地保護電路內部M管,從而減小了芯片面積。SCR結構的導通過程描述如下:其內嵌的薄柵NMOS管Q3發生回流擊穿時,引發電流自其柵極流向p襯底,這會引起電流自n阱流向p襯底,也因而觸發了SCR結構的導通。為了防止SCR結構在普通MOS管正常工作情形下會被導通,其內嵌的薄柵NMOS管Q3的柵極必須要連接到地,以保持該NMOS管關閉,如圖2(b)所示。

圖3顯示了改進的SCR ESD保護結構的版圖,包括作為ESD保護器件的Q1,Q2和寬長比為180/1的PMOS管Mp,還有就是作為ESD二級保護器件的薄柵管Q3.圖中VDD是管子所接的電源端,GND是管子所接的地端。

1.3、全芯片ESD保護結構、

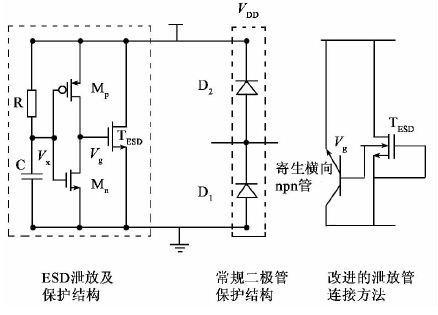

圖4顯示了一種全芯片的ESD保護電路結構。這種保護結構由ESD泄放及保護結構和常規二極管保護結構兩部分組成。其中ESD泄放及保護結構由RC網絡、Mp和Mn兩個邏輯控制管以及ESD電流泄放管TESD等組成。這部分原理簡述如下:ESD對電路的損傷主要是電路的pn逆向擊穿造成的不可逆而導致電路漏電。當VDD網絡上出現ESD電壓時,圖中Vx點的初始電壓為零,由于電容的“惰性”,其兩端電壓不能突變,因此Mp管導通,Vg端電壓將隨著ESD電壓上升,TESD管導通,為ESD電流提供了一條到地的泄放通路。TESD的薄柵氧決定了圖中Vg點的電壓不能上升太高,否則會擊穿柵氧從而損壞器件。因此RC網絡充電抬高Vx端電壓,限制Vg升高,RC充電時間一定要能夠保證ESD能泄放完才關斷Mn管,一般要求在200ns左右,要求TESD管的設計能夠承載大電流,因此要設計足夠的柵寬長比。正常情況下,TESD管的柵壓為0V,其實是關閉的,因此不影響芯片的正常工作。

這種全芯片的ESD保護結構能夠很好地提高電路的ESD保護能力,但當半導體工藝到深亞微米階段,為了防止熱載流子效應,都會在MOS的源漏端采用淺摻雜( lightly doped drain,LDD)結構。圖4中的TESD管就采用了LDD結構。當TESD管導通泄放ESD電流時,大電流從這個管子的表面通過,這樣結深很淺的淺摻雜處很容易損壞,從而限制了這種全芯片ESD保護結構的防護能力。

在電容式觸摸感應檢測按鍵電路中采用了一種改進的全芯片ESD保護結構,改進的是ESD電流泄放管TESD的連接方式,如圖4所示。經過改進后,TESD管的柵接地,而Vg輸出接TESD管的襯底,其余器件結構和參數保持不變。與通常的全芯片ESD保護結構相比,這種改進的全芯片ESD保護結構引入了寄生的橫向npn管,如圖4所示。

在這種改進的全芯片ESD結構中,當VDD網絡上出現ESD電壓時,會引起Vg電壓變化,由于電壓的存在,會引起襯底上電子的遷移而形成電流,電流流過襯底電阻后會抬高寄生npn管的基極電壓,最終會觸發這個npn管的導通,這時ESD電流是通過npn管在襯底上流過而不是在MOS管表面流過,TESD管并沒有開啟而是用其寄生的橫向npn管來泄放ESD電流,而LDD結構不會受到ESD電流的損害,這樣就能大幅提高這種保護電路ESD防護能力。

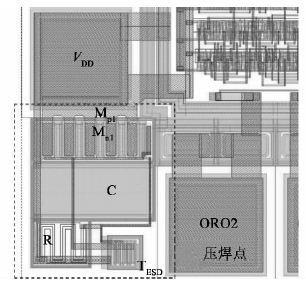

圖5中虛線框部分是這種改進的全芯片ESD保護結構的版圖,該圖顯示了邏輯控制管Mp,Mn和RC網絡以及最重要的薄柵管TESD的位置,其中電容與其下的阱電阻組成ESD探測器。從圖5可以看出,一個全芯片的ESD保護結構所占的芯片面積只比一個壓焊點的面積略大,也就是說在某一個芯片中插入這種全芯片的ESD保護結構后,不會引起該芯片的面積增加太多,但可以大大提高該芯片的ESD保護能力。

2、3種ESD保護結構比較和測試結果

2.1、3種結構在不同ESD測試模式下的優劣性比較

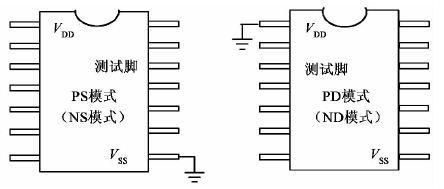

對于芯片的每個端口,都有4種ESD的測試模式,針對±VDD和±VSS模式進行測試,分別稱為所有測試腳對+VDD的PS模式,所有測試腳對-VDD的NS模式,所有測試腳對+VSS的PD模式和所有測試腳對-VSS的ND模式。如圖6所示,針對其中某一個測試腳,施加正的或負的ESD電壓,其余不測的端口全部懸空,只有當4種模式全部成功通過某一電壓(如4000V)測試,才能認為此端口的ESD保護能力達到了4000V.

對于二極管加電阻的ESD保護結構,其中二極管通常采用柵極接地的NMOS管和柵極接電源的PMOS管來實現。采用這種ESD保護結構的電路一般對NS和PD兩種測試模式的ESD能力保護比較高,而針對ND和PS兩種測試模式的ESD保護能力則要差許多。這是因為在NS測試模式下某一個測試腳上接入負的ESD電壓,NMOS管寄生的二極管正向導通,同理PD模式下VDD端接地,某一個測試腳上接入正ESD電壓,PMOS寄生的二極管正向導通,如圖1(b)所示。在ND和PS模式下,寄生二極管需要反向擊穿來泄放ESD電流。對于某一特定器件所能承受的ESD能量是固定的,二極管的正向導通電壓為0.7V左右,遠小于其反向擊穿電壓,因此二極管正向導通時能承受的ESD泄放電流也遠遠大于其反向擊穿時,即ESD電壓遠高于反向擊穿時的ESD電壓。因此ND和PS模式下ESD保護能力差是這種保護結構的缺點。

同樣,可控硅整流器ESD保護結構也有同樣的問題。全芯片ESD保護電路正好可以解決這個問題,從而顯示出這種結構較前兩種結構的優越性。原理簡述如下:以PS模式為例,電源腳懸空,地腳接低電平,在沒有全芯片ESD保護電路時,D1寄生二極管將反向擊穿泄放ESD電流,而現在ESD電壓則會通過D2充到VDD網絡上,如圖4所示,再通過ESD保護電路泄放到地。以上ESD泄露方式避免了D1反向擊穿情況的出現,同理ND模式也可以用這種思路分析。

2.2、3種結構所占用的芯片面積以及ESD耐壓測試結果比較

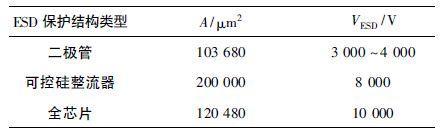

將以上3種結構應用到電容式觸摸感應按鍵檢測電路的設計中,芯片采用的是0.35μm MOS工藝,共有10個壓焊點。3種結構所占用的芯片面積如表1所示。表中A為ESD結構所占用的芯片面積,VESD為ESD耐壓測試的電壓。

對采用3種改進的ESD保護結構的芯片進行ESD耐壓測試,結果如表1所示。從表1比較結果可以看出,全芯片ESD保護結構比二極管ESD保護結構所占用的芯片面積增加了16800μm2,面積增加的比例為16%,但ESD保護能力提高了2倍多;而跟可控硅整流器ESD保護結構相比,全芯片ESD保護結構所占的芯片面積只有可控硅整流器ESD保護結構的60%,但ESD保護能力卻提高了2000V,表明全芯片ESD保護結構具有最好的ESD保護能力。

2.3、3種結構的ESD保護能力測試結果

用ESD模型之一的人體模型工業測試標準HBMMIL—STD—883F3.15.7對采用以上3種改進后的ESD保護結構的電容式觸摸感應檢測按鍵電路進行ESD保護能力測試。以PS模式為例具體說明測試方法如下:每種電路準備3個樣品,這3個樣品首先必須通過功能的測試;電源腳懸空,地腳接低電平,其他所有管腳也都浮懸空,在某一個測試腳上施加正電壓來等效實際電路使用時所承受的正的ESD電壓,起始電壓為500V,以后每做一次測試電壓往上增加500V,也就是說步進電壓為500V;然后監控該測試腳在施加ESD電壓前后的電流-電壓曲線,通常采用包絡線法來判斷施加ESD電壓前后測試腳的電流-電壓曲線的變化。當相對包絡線小于15%判斷為施加ESD電壓前后的電流-電壓曲線沒有變化,該管腳還可以承受更高的ESD電壓。繼續往上增加電壓,直到超出15%這個范圍,比如加到4500V,相對包絡線超出了15%,就表明該測試管腳已經超過了ESD承受范圍,而這時所加的ESD電壓4500V的前一檔,也就是說4000V就是該測試腳所能承受的最高ESD電壓;再對該測試腳進行NS,PD和ND等其他3種模式的測試,如果4種模式都能通過4000V,并且經過ESD打擊后電路的功能沒有改變,還要3個樣品都能重復該試驗,這才表示這個管腳的ESD耐壓為4000V.

通常ESD水平分為三級:一級為0~1999V;二級為2000~3999V;三級為4000~8000V.對于一些特殊的應用,ESD耐壓要求超過10000V,那就是在三級的基礎上繼續往上增加ESD電壓,直到所加電壓超過10000V,并且測試腳的電流-電壓曲線沒有變化,表明該芯片的ESD耐壓可以高達10000V.

3、結語

電容式觸摸感應檢測按鍵電路要求具有特別高的ESD保護能力,因此必須采用有效的ESD保護結構。本文列舉了二極管加電阻、可控硅整流器和全芯片等3種ESD保護結構,并重點針對電容式觸摸感應檢測按鍵電路的結構和工藝特點,提出了對這3種保護結構的改進措施。結果表明經過改進后的3種ESD保護結構在保護能力、芯片面積的利用率以及可靠性等方面都有了非常好的提升,其中全芯片ESD保護結構占用的芯片面積最小,且針對所有ESD測試模式都有最好的ESD保護能力,這種結構可以推廣到其他類型集成電路的ESD保護結構設計中。

-

ESD

+關注

關注

48文章

2012瀏覽量

172798 -

感應電路

+關注

關注

0文章

11瀏覽量

9629

發布評論請先 登錄

相關推薦

感應電動機工作原理是什么?有哪些基本結構?

產生感應電流和感應電動勢的條件一樣嗎

感應電會導致漏電保護跳閘嗎

5針M16接口結構設計

異步感應電機的特性是什么

3針M5插座結構設計

FPGA設計中,對SPI進行參數化結構設計

7芯M9插頭需采用彈性結構設計嗎

觸摸感應電路中的ESD保護結構設計方案

觸摸感應電路中的ESD保護結構設計方案

評論