引言

分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本單元之一。盡管目前在大部分設(shè)計(jì)中還廣泛使用集成鎖相環(huán)(如altera的PLL,Xilinx的DLL)來進(jìn)行時鐘的分頻、倍頻以及相移設(shè)計(jì),但是,對于時鐘要求不太嚴(yán)格的設(shè)計(jì),通過自主設(shè)計(jì)進(jìn)行時鐘分頻的實(shí)現(xiàn)方法仍然非常流行。首先這種方法可以節(jié)省鎖相環(huán)資源,再者,這種方式只消耗不多的邏輯單元就可以達(dá)到對時鐘操作的目的。

1 整數(shù)分頻器的設(shè)計(jì)

1.1 偶數(shù)倍分頻

偶數(shù)分頻器的實(shí)現(xiàn)非常簡單,通過計(jì)數(shù)器計(jì)數(shù)就完全可以實(shí)現(xiàn)。如進(jìn)行N倍偶數(shù)分頻,就可以通過由待分頻的時鐘觸發(fā)計(jì)數(shù)器計(jì)數(shù),當(dāng)計(jì)數(shù)器從0計(jì)數(shù)到N/2-1時,輸出時鐘進(jìn)行翻轉(zhuǎn),并給計(jì)數(shù)器一個復(fù)位信號,以使下一個時鐘從零開始計(jì)數(shù)。以此循環(huán),就可以實(shí)現(xiàn)任意的偶數(shù)分頻。

1.2 奇數(shù)倍分頻

奇數(shù)倍分頻有兩種實(shí)現(xiàn)方法,其中之一完全可以通過計(jì)數(shù)器來實(shí)現(xiàn),如進(jìn)行三分頻,就可通過待分頻時鐘上升沿觸發(fā)計(jì)數(shù)器來進(jìn)行模三計(jì)數(shù),當(dāng)計(jì)數(shù)器計(jì)數(shù)到鄰近值時進(jìn)行兩次翻轉(zhuǎn)。比如可以在計(jì)數(shù)器計(jì)數(shù)到1時,輸出時鐘進(jìn)行翻轉(zhuǎn),計(jì)數(shù)到2時再次進(jìn)行翻轉(zhuǎn)。這樣,就在計(jì)數(shù)值鄰近的1和2進(jìn)行了兩次翻轉(zhuǎn)。如此便實(shí)現(xiàn)了三分頻,其占空比為1/3或2/3。

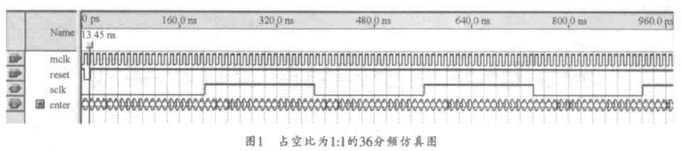

占空比1/15的15分頻設(shè)計(jì)的主要代碼如下:

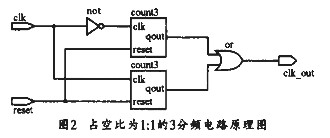

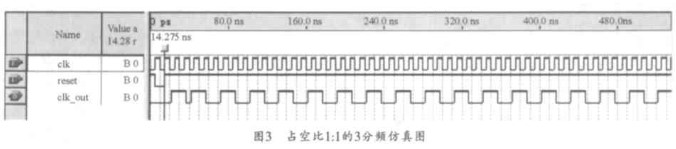

如果要實(shí)現(xiàn)占空比為50%的三分頻時鐘,則可通過待分頻時鐘下降沿觸發(fā)計(jì)數(shù),并以和上升沿同樣的方法計(jì)數(shù)進(jìn)行三分頻,然后對下降沿產(chǎn)生的三分頻時鐘和上升沿產(chǎn)生的時鐘進(jìn)行相或運(yùn)算。即可得到占空比為50%的三分頻時鐘這是奇數(shù)分頻的第三種方法。這種方法可以實(shí)現(xiàn)任意的奇數(shù)分頻。如將其歸類為一般的方法:對于實(shí)現(xiàn)占空比為50%的N倍奇數(shù)分頻,首先要進(jìn)行上升沿觸發(fā)以進(jìn)行模N計(jì)數(shù),計(jì)數(shù)選定到某一個值再進(jìn)行輸出時鐘翻轉(zhuǎn),然后過(N-1)/2再次進(jìn)行翻轉(zhuǎn),就可得到一個占空比非50%的奇數(shù)n分頻時鐘。再同時進(jìn)行下降沿觸發(fā)的模N計(jì)數(shù),當(dāng)其到達(dá)與上升沿觸發(fā)輸出時鐘翻轉(zhuǎn)選定值相同時,再進(jìn)行輸出時鐘翻轉(zhuǎn),同樣,經(jīng)過(N-1)/2時,輸出時鐘再次翻轉(zhuǎn)以生成占空比非50%的奇數(shù)n分頻時鐘。將這兩個占空比非50%的n分頻時鐘相或運(yùn)算,就可以得到占空比為50%的奇數(shù)n分頻時鐘。

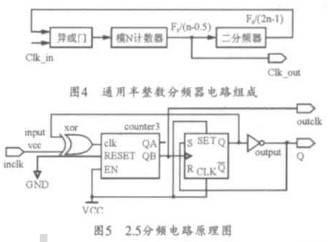

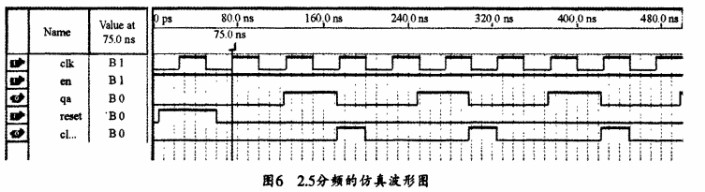

2 半整數(shù)分頻器設(shè)計(jì)

進(jìn)行n+0.5分頻一般需要對輸入時鐘先進(jìn)行操作。其基本設(shè)計(jì)思想是:首先進(jìn)行模n的計(jì)數(shù),在計(jì)數(shù)到n-1時,將輸出時鐘賦為‘1’,而當(dāng)回到計(jì)數(shù)0時,又賦為0,這樣,當(dāng)計(jì)數(shù)值為n-1時,輸出時鐘才為1,因此,只要保持計(jì)數(shù)值n-1為半個輸入時鐘周期,即可實(shí)現(xiàn)n+0.5分頻時鐘。因此,保持n-1為半個時鐘周期即是該設(shè)計(jì)的關(guān)鍵。從中可以發(fā)現(xiàn),因?yàn)橛?jì)數(shù)器是通過時鐘上升沿計(jì)數(shù),故可在計(jì)數(shù)為n-1時對計(jì)數(shù)觸發(fā)時鐘進(jìn)行翻轉(zhuǎn),那么,時鐘的下降沿就變成了上升沿。即在計(jì)數(shù)值為n-1期間的時鐘下降沿變成了上升沿,也就是說,計(jì)數(shù)值n-1只保持了半個時鐘周期。由于時鐘翻轉(zhuǎn)下降沿變成上升沿,因此,計(jì)數(shù)值變?yōu)?。所以,每產(chǎn)生一個n+0.5分頻時鐘的周期,觸發(fā)時鐘都要翻轉(zhuǎn)一次。

3 任意整數(shù)帶小數(shù)分頻

任意整數(shù)帶小數(shù)分頻的基本原理是采用脈沖吞吐計(jì)數(shù)器和鎖相環(huán)技術(shù)先設(shè)計(jì)兩個不同分頻比的整數(shù)分頻器,然后通過控制單位時間內(nèi)兩種分頻比出現(xiàn)的不同次數(shù)來獲得所需要的小數(shù)分頻值。若設(shè)計(jì)一個分頻系數(shù)為10.1的分頻器,即可以將分頻器設(shè)計(jì)成9次10分頻和1次11分頻,這樣,總的分頻值為:

F=(9×10+1×11)/(9+1)=10.1

從這種實(shí)現(xiàn)方法的特點(diǎn)可以看出,由于分頻器的分頻值不斷改變,分頻后得到的信號抖動一般較大。當(dāng)分頻系數(shù)為N-0.5(N為整數(shù))時,可控制扣除脈沖的時間,以使輸出成為一個穩(wěn)定的脈沖頻率,而不是一次N分頻,一次N-1分頻。一般而言,這種分頻由于分頻輸出的時鐘脈沖抖動很大,故在設(shè)計(jì)中的使用已經(jīng)非常少。但是,這也是可以實(shí)現(xiàn)的。

4 結(jié)束語

利用本文介紹的方法可在對時鐘要求比較嚴(yán)格的FPGA系統(tǒng)中,用FPGA內(nèi)嵌的鎖相環(huán)資源來實(shí)現(xiàn)分頻。該設(shè)計(jì)方法簡單方便、節(jié)約資源、可移置性強(qiáng)、便于系統(tǒng)升級,因此,在時鐘要求不太嚴(yán)格的系統(tǒng)中應(yīng)用非常廣泛,同時在以后的FPGA設(shè)計(jì)發(fā)展中也有很大的應(yīng)用空間。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601840 -

鎖相環(huán)

+關(guān)注

關(guān)注

35文章

583瀏覽量

87694 -

分頻器

+關(guān)注

關(guān)注

43文章

447瀏覽量

49813

發(fā)布評論請先 登錄

相關(guān)推薦

基于FPGA的通用數(shù)控分頻器設(shè)計(jì)方案

基于FPGA的任意數(shù)值分頻器的設(shè)計(jì)

基于FPGA的任意分頻器設(shè)計(jì)

如何利用CPLD/FPGA設(shè)計(jì)多功能分頻器?

基于FPGA的多種形式分頻的設(shè)計(jì)與實(shí)現(xiàn)

基于CPLD/FPGA的多功能分頻器的設(shè)計(jì)與實(shí)現(xiàn)

什么是分頻器 分頻器介紹

FPGA實(shí)現(xiàn)小數(shù)分頻器

用Verilog實(shí)現(xiàn)基于FPGA的通用分頻器的設(shè)計(jì)

分頻器有哪些_分頻器分類

奇數(shù)分頻器的介紹和實(shí)現(xiàn)

基于CPLD/FPGA的半整數(shù)分頻器設(shè)計(jì)方案

FPGA分頻器的設(shè)計(jì)方法

FPGA學(xué)習(xí)-分頻器設(shè)計(jì)

利用FPGA技術(shù)實(shí)現(xiàn)各類分頻器的設(shè)計(jì)

利用FPGA技術(shù)實(shí)現(xiàn)各類分頻器的設(shè)計(jì)

評論